СХЕМОТЕХНИКА ЭВМ_18.2.17 (855859), страница 9

Текст из файла (страница 9)

В заключение следует снова отметить, что традиционная минимизация логических функций, преследующая цель уменьшить количество вхождений переменных и количество операций не учитывает множества других критериев, как например минимизации задержки сигналов и т.п.

Вопросы и упражнения к главе 2

Вопрос 1. Из скольких строк максимально состоит Таблица истинности логической функции от трех аргументов ?

Вопрос 2. Что такое схема устройства , выполняющего логическую функцию,

Вопрос 3. Что такое критический путь сигнала в схеме?

Вопрос 4. Сколько элементов 2И-НЕ понадобится для реализации функции 3И ?

Упражнение

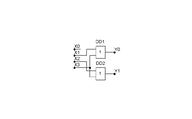

Для схемы, представленной ниже, просчитайте максимальную и минимальную задержки выходного сигнала в предположении, что задержки в элементах НЕ=2 нс, И-НЕ- 3 нс, ИЛИ-НЕ -4 нс , составьте таблицу истинности реализуемой логической функции, выполните ее алгебраическое описание в виде СДНФ и на HDL.

…………Рис.2.12.Комбинационная схема ….

Вопрос 5. Как влияет критерий минимизации количества микросхем при проектировании цифровых устройств ?

.

Глава 3. ЦИФРОВЫЕ УЗЛЫ КОМБИНАЦИОННОГО ТИПА.

(Лекции 5-7)

При проектировании с использованием микросхем среднего уровня интеграции, проектировщик обычно покрывает схему функциональными узлами типа дешифратор,мультиплексор,сумматор и т.п.

Рассмотрим некоторые из них.

3.1. Дешифраторы.

Дешифратором называется комбинационная схема, преобразующая входное кодовое слово размерности n в выходное кодовое слово размерности 2n. На входы управления обычно подаются сигналы разрешения. Обобщенное представление функции дешифратора представлено на рис.3.1.

Рис. 3.1. Обобщенное представление функции дешифратора.

Промышленность выпускает микросхемы дешифраторов типа n х 2n. На следующем рисунке показана схема дешифратора 2 х 22 (2 х 4) типа ИД14.

а) б)

а) схема дешифратора; б) условное графическое обозначение (УГО)

Рис. 3.2. Схема дешифратора КР1533ИД14 и его УГО.

Дешифратор имеет два информационных входа А0 и А1 и вход разрешения Е. Если на вход Е подать запрещающий сигнал "1", то на выходах Y0 – Y3 будет сигнал "1" при любых сигналах на входах А0 и А1.

Если на вход Е подать разрешающий сигнал "0", то на одном из выходов Y0 – Y3 будет сигнал низкого уровня. Номер выхода соответствует двоичному числу, поданному на входы А0 и А1.

Таблица 3.1. Таблица истинности дешифратора типа ИД14.

| Входы | Выходы | |||||

| E | A1 | A0 | Y3 | Y2 | Y1 | Y0 |

| 1 | х | х | 1 | 1 | 1 | 1 |

| 0 | 0 | 0 | 1 | 1 | 1 | 0 |

| 0 | 0 | 1 | 1 | 1 | 0 | 1 |

| 0 | 1 | 0 | 1 | 0 | 1 | 1 |

| 0 | 1 | 1 | 0 | 1 | 1 | 1 |

Возможны разные варианты описаний устройств на языке VHDL. Следующее описание на VHDL дешифратора, схема которого приведена на рис.3.2., выполнено в форме , аналогичной системе уравнений. В этом описании присутствует отдельный оператор присваивания для каждого выходного сигнала в соответствии с таблицей истинности дешифратора( табл.3.1).

library IEEE; --[1][2]

use IEEE.STD_LOGIC_1164.all;

entity DC_2_4 is

port(E,A0,A1:in STD_LOGIC; Y0,Y1,Y2,Y3 : out STD_LOGIC );

end ;

architecture FLOW of DC_2_4 is

begin

Y0<= not( not E and not A0 and not A1 );

Y1<= not( not E and not A0 and A1 );

Y2<= not( not E and A0 and not A1 );

Y3<= not( not E and A0 and A1 );

end ;

Описание на VHDL теста для проверки модели дешифратора имеет следующий вид:

LIBRARY ieee; USE ieee.std_logic_1164.ALL;-- [1][2]

ENTITY dec_2_4_TB IS

END dec_2_4_TB;

ARCHITECTURE behavior OF dec_2_4_TB IS

COMPONENT DC_2_4

PORT(

E : IN std_logic;

A0 : IN std_logic;

A1 : IN std_logic;

Y0 : OUT std_logic;

Y1 : OUT std_logic;

Y2 : OUT std_logic;

Y3 : OUT std_logic

);

END COMPONENT;

--Inputs

signal E : std_logic := '0'; signal A0 : std_logic := '0';

signal A1 : std_logic := '0';

--Outputs

signal Y0 : std_logic; signal Y1 : std_logic;

signal Y2 : std_logic; signal Y3 : std_logic;

BEGIN

-- Instantiate the Unit Under Test (UUT)

uut: DC_2_4 PORT MAP

(

E => E, A0 => A0, A1 => A1, Y0 => Y0,

Y1 => Y1, Y2 => Y2, Y3 => Y3

);

-- Stimulus process

stim_proc: process

begin

wait for 20 ns; A0<='0'; A1<='1';

wait for 20 ns; A0<='1'; A1<='0';

wait for 20 ns; A0<='1'; A1<='1';

wait for 20 ns; A0<='0'; A1<='0';

wait for 20 ns;E<='1';

wait for 20 ns; E<='0'; A0<='0'; A1<='1';

wait;

end process;

END;

Временная диаграмма работы модели дешифратора, полученная в результате моделирования, показана на рисунке 3.3.

Рис. 3.3. Результаты моделирования дешифратора 2-4.

Для увеличения разрядности кодовых слов на входах и выходах дешифратора применяются схемы каскадирования.

Приведем стандартные схемы каскадирования для дешифраторов типа ИД7 (рис. 3.4) и ИД14 (рис. 3.5).—входы V0, V1, V2 разрешают работу дешифратора при V0=1, V1=0, V2=0.

Рис. 3.4. Каскадирование дешифраторов типа ИД7 при помощи входов управления.

Рис. 3.5. Каскадирование дешифраторов типа ИД14 при помощи дополнительного дешифратора DD1.

3.1.1. Поведенческое описание схемы дешифратора на VHDL.

Описание дешифратора 3 х 8 типа ИД7 на VHDL можно провести, в отличие от ранее приведенного описания, в другом стиле, так называемом поведенческом, на основе оператора process с использованием операторов case и if и векторного представления сигналов. Такой стиль для случая многовыходовых дешифраторов позволяет сделать описания устройств компактнее.

library IEEE; [2][1][почему сразу не прививать поведенческий стиль?]

use IEEE.STD_LOGIC_1164.all;

entity DEC_1 is

port( E_n : in STD_LOGIC;

X : in STD_LOGIC_VECTOR(2 downto 0);

Y : out STD_LOGIC_VECTOR(7 downto 0) );

end DEC_1;

architecture DEC_1_ARC of DEC_1 is

begin

process(E_n)

begin

if (E_n = '0') then

case(X) is

when "000" => Y <= "11111110";

when "001" => Y <= "11111101";

when "010" => Y <= "11111011";

when "011" => Y <= "11110111";

when "100" => Y <= "11101111";

when "101" => Y <= "11011111";

when "110" => Y <= "10111111";

when "111" => Y <= "01111111";

when others => Y <= "11111111";

end case;

else Y <= "11111111";

end if;

end process;

end DEC_1_ARC;

Вход E_n является разрешающим, вектор X – входы {X0, X1 и X2}, вектор Y – выходы {Y0, … Y7}.

3.2. Шифратор и кодовый преобразователь.

Шифратором называется комбинационная схема, преобразующая входное кодовое слово размерности 2n в выходное кодовое слово размерности n. На входы управления подаются сигналы разрешения.

Шифратор выполняет операцию, обратную к дешифратору. Обобщенное представление его функции представлено на рис.3.6.

На практике широко применяется комбинация схем дешифратора и шифратора для реализации кодовых преобразователей.

Рис. 3.6 Обобщенное представление функции шифратора.

Принципиальная схема шифратора 4 х 2 представлена на рис. 3.7.

Для нормальной работы шифратора необходимо, что бы сигнал приходил только на один его вход. Понятно, что если подать сигналы "1" на любые два входа, то дешифратор будет работать неправильно.

Этого недостатка лишена схема приоритетного шифратора, в котором добавлена специальная схема, выделяющая старшую по приоритету единицу.

На базе приоритетного шифратора строится, например, схема выработки кодов клавиш в клавиатуре компьютера. В этом случае, при одновременном нажатии на несколько клавиш вырабатывается код только одной из них, имеющей максимальный приоритет. [почему x0 пустой?]

| Входы | Выходы | ||||

| Х0 | Х1 | Х2 | Х3 | Y0 | Y1 |

| 1 | 0 | 0 | 0 | 0 | 0 |

| 0 | 1 | 0 | 0 | 1 | 0 |

| 0 | 0 | 1 | 0 | 0 | 1 |

| 0 | 0 | 0 | 1 | 1 | 1 |

а) б)

а) - принципиальная схема

б) - таблица истинности

Рис. 3.7. Принципиальная схема шифратора и его таблица истинности.

3.2.1. Приоритетный шифратор.

Работа приоритетного шифратора 4 х 2 определяется таблицей истинности (табл. 3.2). Входные сигналы Х0, Х1, Х2 и Х3 и сигнал выбора Е имеют высокий логический уровень. Приоритет сигналов убывает в порядке Х3, Х2, Х1, Х0.

Выходные сигналы шифратора Y0 и Y1, сигнал переноса Е0 и сигнал группового выбора GS имеют высокий уровень.

Сигнал Е разрешает работу шифратора. Выходной сигнал Е0 подключается к входу разрешения Е другого шифратора, имеющего более низкий приоритет. Сигнал GS имеет низкий уровень, если активный сигнал подан хотя бы на один из входов шифратора. Таким образом проводится каскадирование дешифраторов.

Таблица 3.2. Таблица истинности приоритетного шифратора.

| Е | Х3 | Х2 | Х1 | Х0 | Y0 | Y1 | GS | Е0 |

| 0 | х | х | х | х | 0 | 0 | 0 | 0 |

| 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 |

| 1 | 0 | 0 | 0 | 1 | 0 | 0 | 1 | 0 |

| 1 | 0 | 0 | 1 | x | 1 | 0 | 1 | 0 |

| 1 | 0 | 1 | x | x | 0 | 1 | 1 | 0 |

| 1 | 1 | x | x | x | 1 | 1 | 1 | 0 |

Если на входе разрешения Е сигнал низкого уровня, то при любых сигналах {Xi} на входах шифратор не работает, при этом все сигналы на выходах имеют низкий уровень.

Шифратор включается в работу, если на вход разрешения Е подан сигнал высокого уровня. Если ни на один из входов Х0, Х1, Х2 или Х3 активный сигнал не подан, то вырабатывается сигнал Е0, который подается на вход разрешения шифратора с меньшим приоритетом.

Если на один или несколько входов Х0, Х1, Х2 или Х3 поданы сигналы, то на выходах Y0 и Y1 появляется двоичное число, соответствующее номеру старшего по приоритету входу. В этом случае сигнал Е0 равен нулю, а сигнал группового выбора GS – единице.