СХЕМОТЕХНИКА ЭВМ_18.2.17 (855859), страница 13

Текст из файла (страница 13)

tpHL (RQ) – время, необходимое для переключения от высокого логического уровня сигнала к низкому. Эти времена задержки могут быть не равны между собой.

Сигналы, поступающие на входы RS-триггера, должны иметь достаточную длительность. Если длительность входных сигналов меньше заданного в справочниках минимального значения tp(min) (обычно это время близко к времени задержки распространения), то переходный процесс может не дойти до конца, и работа схемы будет нарушена.

4.2.2 Описание асинхронного RS-триггера-защелки на VHDL.

Ниже представлены два варианта описания RS-триггера-защелки.

Первый вариант прямо соответствует схеме рис.4.1, второй иллюстрирует процессный стиль описания триггера и несколько искажает его поведение т.к. допускает одновременное появление одинаковых значений на выходах- или двух 0, или двух 1. [зачем он нужен?]

Первый вариант- описание схемы RS- триггера на элементах ИЛИ-НЕ.

library IEEE; [2][1]

use IEEE.STD_LOGIC_1164.all;

entity RS_Latch is port

( S,R : in STD_LOGIC; Q, Qbar : out STD_LOGIC :=’0’ );

end ;

architecture SXEMA of RS_Latch is

begin

Q<= not (S OR Qbar) ;

Qbar<= not (R OR Q);

end ;

Второй вариант –описание RS - триггера функциональное

library IEEE; [1][2]

use IEEE.STD_LOGIC_1164.all;

entity RS_Tr is

port( S : in STD_LOGIC;

R : in STD_LOGIC;

Q : out STD_LOGIC;

Qbar : out STD_LOGIC );

end RS_Tr;

architecture BEH of RS_Tr is

begin

process (R,S)

begin

if (S ='1') and (R = '0') then

Q <= '1'; Qbar <= '0';

end if;

if (R ='1') and (S = '0') then

Q <= '0'; Qbar <= '1';

end if;

end process;

end ;

. Переключение триггера происходит при изменении сигналов R или S и при возникновении "разрешенной" комбинации, перечисленной в условных операторах if.

4.2.3 Асинхронный триггер-защелка на элементах И-НЕ.

R

S-триггер может быть построен на элементах И-НЕ.

S-триггер может быть построен на элементах И-НЕ.

а) б) в)

а) схема, б) таблица функционирования, в) УГО

Рис. 4.3. Асинхронный триггер –защелка на элементах И-НЕ.

Активными уровнями сигналов R и S на входе являются низкие уровни. Запрещенным состоянием является R = 0 и S = 0. По такой схеме выпускается отечественная микросхема RS-триггера типа ТР2. [его диаграмма ]

4.2.4. Синхронный RS-триггер.

Для синхронизации переключений триггера вводится дополнительный сигнал синхронизации С, активный уровень которого разрешает переключение триггера в соответствии с входными сигналами R и S.

| S | R | C | Q | Q |

| 0 | 0 | 1 | Qt-1 | Q |

| 0 | 1 | 1 | 0 | 1 |

| 1 | 0 | 1 | 1 | 0 |

| 1 | 1 | 1 | 0 | 0 |

| x | x | 0 | Qt-1 | Q |

а) б)

а) схема б) таблица функционирования

Рис. 4.4. Синхронный RS-триггер.

Временная диаграмма работы синхронного RS-триггера показана на рисунке 4.5.

Рис. 4.5. Временная диаграмма работы синхронного RS-триггера.

Отсчет моментов времени на временной диаграмме проводится от середины фронтов импульсов. Если сигналы на входах S = 1 и R = 0, то через время tpLH на выходе Q появится сигнал Q = 1.

Минимально необходимое для правильной работы триггера время упреждения подачи входных сигналов перед появление синхроимпульса называется временем предустановки ( tsetup ).Минимальное время ,в течение которого эти сигналы еще должны удерживаться после фронта синхросигнала называется временем удержания ( thold ).

4.2.5 Описание синхронного RS-триггера на VHDL.

library IEEE; [1][2]

use IEEE.STD_LOGIC_1164.all;

entity RSC_Tr is

port( S : in STD_LOGIC;

C : in STD_LOGIC;

R : in STD_LOGIC;

Q : out STD_LOGIC;

Qbar : out STD_LOGIC);

end RSC_Tr;

architecture RSC_Tr_arc of RSC_Tr is

begin

process(C)

begin

if(C = '1') and (R = '1') and (S = '0') then

Q <= '0'; Qbar <= '1';

elsif (C = '1') and (R = '0') and (S = '1') then

Q <= '1'; Qbar <= '0';

end if;

end process;

end RSC_Tr_arc;

Переключение триггера происходит при появлении сигнала С = '1'. "Разрешенная" комбинация сигналов R и S должна появиться на входах триггера раньше сигнала С.

Если на входах триггера "разрешенная" комбинация сигналов не появляется или появляется "не разрешенная" комбинация, то сигнал С = '1' не изменяет состояние триггера.

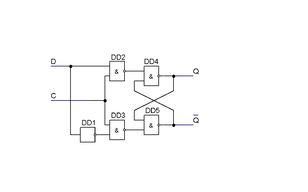

4.2.6. D-триггер с управлением уровнем синхросигнала( защелка ).

Для хранения одного бита информации, поступающего по отдельной сигнальной линии, применяется D-триггер. Его схема приведена на рис. 4.6.

Когда подан синхросигнал С высокого уровня, D-триггер "прозрачен", так как сигнал на выходе Q повторяет сигнал на входе D с учетом задержки распространения. Если приходит сигнал С низкого уровня, то D-триггер переходит в режим хранения и сохраняет на выходе последнее значение сигнала D.

Триггер "прозрачен" все время, пока действует синхросигнал.

| C | D | Q | Q |

| 1 | 0 | 0 | 1 |

| 1 | 1 | 1 | 0 |

| 0 | x | Qt-1 | Q |

а) б)

а) схема D-триггера, б) таблица функционирования.

Рис. 4.6. D-триггер ( D-защелка).

Временная диаграмма работы D-триггера-защелки представлена на рис. 4.7. Если сигнал на входе D = 1, то после появления сигнала С = 1 через время tpLH(CQ) на выходе Q появится сигнал Q = 1. [что делает DD1]

Поведение D-триггера в районе спада сигнала С имеет особенности. В это время сигнал на входе D не должен меняться. Этот интервал времени начинается за время установки tsetup до спада сигнала С и заканчивается через время удержания thold после спада сигнала С. Если сигнал D изменяется в течение этого интервала, то последующее состояние триггера оказывается непредсказуемым. Это может привести к сбою в работе цифровой схемы.

Рис. 4.7. Временная диаграмма работы D-триггера (защелки).

Асинхронные триггеры и триггеры с синхронизацией по уровню синхросигнала (триггеры с потенциальным управлением) являются наиболее простыми. Поэтому они широко применяются в качестве базовых элементов в современных заказных интегральных схемах. Недостатки, присущие этим триггерам, устраняются средствами САПР.

4.2.7. Описание синхронного D-триггера (защелки) на VHDL.

library IEEE; [1][2]

use IEEE.STD_LOGIC_1164.all;

entity D_Tr_1 is

port( C : in STD_LOGIC;

D : in STD_LOGIC;

Q : out STD_LOGIC;

Qbar : out STD_LOGIC );

end D_Tr_1;

architecture D_Tr_1_arc of D_Tr_1 is

begin

process(C)

begin

if (C = '1') then

Q <= D;

Qbar <= not D;

end if;

end process;

end D_Tr_1_arc;

4.2.8. Триггеры с динамическим управлением.

В микросхемах средней степени интеграции широко применяются триггеры с динамическим управлением. Такой триггер изменяет свое состояние только в малой окрестности фронта синхросигнала. [диаграмма отличия]

Промышленность выпускает различные типы микросхем триггеров с динамическим управлением, схемы которых близки между собой.

Схема и УГО шестиэлементного D-триггера с динамическим управлением приведены на рис. 4.8, а временная диаграмма его работы – на рис. 4.9.

Н а временной диаграмме названия графиков совпадают с обозначениями контрольных точек на выходе логических элементов.

а временной диаграмме названия графиков совпадают с обозначениями контрольных точек на выходе логических элементов.

В этой схеме хранение информации происходит в выходном RS-триггере (элементы DD5 и DD6) с инверсными сигналами на входах.

Управление схемой осуществляют еще два RS-триггера (элементы DD1 и DD2, DD3 и DD4).