Лекция 6. Блок ввода-вывода

Лекция 6 – Блок ввода/вывода и конфигурируемый логический блок ПЛИС серии ХС2000 фирмы Xilinx

ПЛИС серии ХС2000 состоят из двух семейств ХС2000 с номинальным напряжением питания 5 В и ХС2000L –3,3 В. Микросхемы этих семейств (ХС2064, ХС2018 и ХС2064L, ХС2018L) имеют одинаковую архитектуру и различаются лишь параметрами, зависящими от напряжения питания (потребляемой мощностью, быстродействием, уровнями входных и выходных сигналов). Некоторые параметры МС этой серии приведены в таблице 6.1.

Таблица 6.1 – Параметры ПЛИС серии ХС2000

| ПЛИС | Число вентилей 2И-НЕ | Число логических блоков | Максимальное число доступных входов/выходов | Объём памяти конфигурации, бит |

| ХС2064 | Рекомендуемые материалыДомашнее задание №1 (вариант №6) Гидравлический пресс 1.6 МН (для листовой штамповки) Домашнее задание №1 (вариант №6) Домашнее задание №2 (вариант №6) FREE Лабораторная работа №6 Отчет по учебной практике (Вариант 3) - ГОСТ 2.101-68 600 – 1000 | 64 | 58 | 12038 |

| ХС2018 | 1000 – 1500 | 100 | 74 | 17838 |

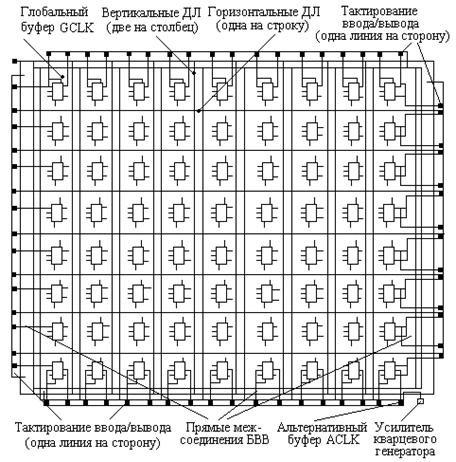

Архитектура ПЛИС серии ХС2000. Общая структура ПЛИС серии

|

Рисунок 6.1 – Структура ПЛИС серии ХС2000 фирмы Xilinx (ХС2064) | ХС2000 показана на рисунке 6.1. Микросхема ХС2064 содержит 64 КЛБ (матрица 8´8), ХС2018 – 100 КЛБ (матрица 10´10). В обозначении микросхемы ХС2064 последние две цифры соответствуют количеству КЛБ. Начиная с МС ХС2018, последние две цифры соответствуют максимальной эквивалентной ёмкости, а именно 1800 вентилей (реальная ёмкость для ХС2018 оказалась меньше (см. таблицу 6.1)). |

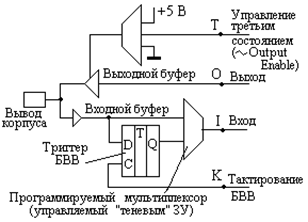

Блок ввода/вывода (БВВ) служит для выбора пользователем конфигурации сопряжения внешних выводов корпуса МС с внутренней частью ПЛИС. Большинство выводов МС связано с конфигурируемыми БВВ, за исключением выводов питания, «земли» и некоторых других. Располагаются БВВ по всем четырём сторонам кристалла ПЛИС.

|

Рисунок 6.2 – Блок ввода/вывода ПЛИС серии ХС2000 | На рисунке 6.2 показана структура БВВ ПЛИС серии ХС2000. Каждый БВВ включает программируемый входной канал (через вывод 1) и программируемый выходной буфер. Входной буфер обеспечивает согласование внешних сигналов, поступающих на выводы корпуса ПЛИС, и внутренних логических сигналов. Порог входного буфера можно запрограммировать на совместимость с уровнями либо ТТЛ-схем (пороговое напряжение 1,4 В), либо схем на КМОП-структурах (пороговое на- |

пряжение 2,2 В). Буферизованный входной сигнал поступает на вход данных триггера и на один из входов программируемого мультиплексора. Выходной сигнал триггера поступает на другой вход мультиплексора. Наличие программируемого мультиплексора даёт возможность пользователю выбрать либо прямой ввод сигнала, либо ввод с запоминанием на триггере. Расположенные входы на одной стороне кристалла БВВ, используют общие синхронизирующие импульсы, поступающие на вход К. Триггеры сбрасываются в 0 в процессе установления конфигурации, а также входом RESET, имеющим активный нижний уровень (при переходе этого сигнала в логический 0).

Вывод 0 является источником данных для выходного буфера. Каждый БВВ может содержать простой буфер или же буфер с тремя состояниями. Пользователь может удалить выходной буфер из БВВ. Тогда данный вывод корпуса будет работать только как вход.

Пользователь также может управлять третьим состоянием выходного буфера, подсоединяя к выводу Т, либо специальный сигнал, либо сам выходной сигнал. Если на вывод Т подан сигнал высокого уровня (логическая 1), то выход буфера переходит в третье состояние и вывод корпуса МС имеет большой импеданс. То есть активным значением управляющего сигнала на выводе Т является логическая 1, что и отражено в обозначении выходного буфера. В обозначения буферов ряда других МС аналогичный сигнал носит название ОЕ (Output Enable – разрешение выхода) и его действующее значение, как правило, соответствует логическому 0.

В случае соединения цепей управляющего сигнала Т и вывода О одного и того же БВВ выходной буфер этого блока становится эквивалентным каскаду с открытым коллектором (стоком).

Выходные буферы в БВВ могут вырабатывать сигналы, соответствующие по уровням схемам на КМОП-структурах. Нагрузочная способность БВВ по току равна 4 мА; номинальная емкостная нагрузка 50 пф. Каждый блок имеет также схемы защиты от электростатического пробоя и режима защёлкивания по входу.

Имена БВВ для МС во всех типах корпусов, кроме PGA, состоят из бук-

вы Р и порядкового номера вывода корпуса (Р1, Р2…). Если БВВ не подсоединён к выводу МС, то его имя начинается с буквы U. Для корпуса PGA имя БВВ соответствует номеру вывода МС (А1, F5, U7, W10…). Один и тот же кристалл может размещаться в корпусах как с большим количеством выводов, что делает доступными все БВВ, так и в корпусах с малым количеством выводов, что уменьшает габаритные размеры МС.

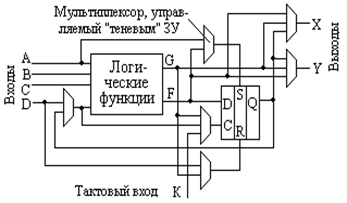

Конфигурируемые логические блоки расположены в виде матрицы в центре кристалла ПЛИС. Строки и столбцы матрицы обозначаются буквами А, В, С, D и т.д., которые используются для задания имени (адреса) блока, например, блоки AA, AD, HH. Разработчик аппаратуры может присвоить блоку новое имя для обозначения, например, узла схемы, занимаемого этим блоком. В этом случае блок будет иметь два имени.

|

Рисунок 6.3 – Конфигурируемый логический блок ПЛИС серии ХС2000 | На рисунке 6.3 показана структура КЛБ. В КЛБ можно выделить три части: · комбинаторный узел, служащий для выработки логических функций; · запоминающий элемент (триггер) для хранения значения одной из логической функции; · узел соединений (мультиплексор), предназначенный для внутренних соединений и управления. |

Каждый КЛБ имеет два выхода X и Y, четыре входа общего назначения А, В, С и D, а также специальный вход синхронизации (тактовый вход) К.

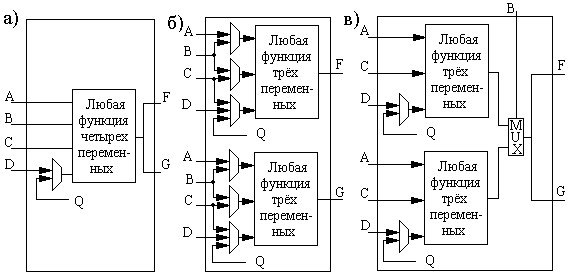

В МС серии ХС2000 можно генерировать любую логическую функцию четырёх переменных (максимум), т.к. для этого используется 16-разрядный регистр «теневого» ЗУ. Время распространения сигнала через комбинаторный узел не зависит от генерируемой функции. Каждый блок может выполнять любую функцию четырёх переменных или любые две функции трёх переменных (см. рисунок 6.4). Переменные для логической функции могут поступать с четырёх входов А, В, С, D и выхода Q триггера.

Запоминающий элемент КЛБ может быть сконфигурирован либо как D-триггер, запоминающий состояние на входе данных по переднему фронту тактового сигнала (FF-триггер), либо как триггер-защёлка (Latch), срабатывающий по заднему фронту. Полярность тактового сигнала триггера может программироваться (то есть тактовый сигнал может иметь вид положительного импульса, так и отрицательного импульса).

Узел соединений с помощью программируемых мультиплексоров обеспечивает различные пути прохождения сигналов от входов до выходов КЛБ, позволяя тем самым изменять общую конфигурацию.

Рисунок 6.4 – Варианты конфигурации функций в МС серии ХС2000: а) – одна функция четырёх переменных; б) – две функции трёх переменных; в) – динамический выбор одной из двух функций трёх переменных

Вопросы для проверки усвоения материала

Лекция "6. Малые архитектурные формы" также может быть Вам полезна.

1. Структура ПЛИС серии ХС2000 фирмы Xilinx.

2. Блок ввода/вывода ПЛИС серии ХС2000 фирмы Xilinx.

3. Конфигурируемый логический блок ПЛИС серии ХС2000 фирмы Xilinx

4. Три составные части конфигурируемого логического блока.

Литература

1. Мальцев П.П., Гарбузов Н.И., Шарапов А.П., Кнышев Д.А. Программируемые логические ИМС на КМОП-структурах и их применение.1998. –М.: Энергоатомиздат, -159 с. (11-15 с)