Лекция 5. Архитектура ПЛИС фирмы Xilinx

Лекция 5 – Архитектура ПЛИС фирмы Xilinx

ПЛИС является одной из современной микросхем. Разработка цифрового управляющего устройства (ЦУУ) на базе ПЛИС осуществляется с помощью высокотехнологичного САПР. В общем случае ПЛИС похожа на СБИС, если прошивка конфигурации будет выполнена один раз на заводе-изготовителе. Стоимость последней будет ниже стоимости микросхемы ПЛИС. Но ПЛИС может изменять свою конфигурацию для каждого конкретного проекта. Выпускники кафедры «Автоматизация и управление» ФЭСТ МГУЛ должны знать:

· архитектуру ПЛИС, принцип её действия;

· САПР цифровых устройств на базе ПЛИС.

Назначение ПЛИС. В ЦУУ микросхема. ПЛИС предоставляет разработчикам большой спектр кристаллов с различной технологией производства, степенью интеграции, архитектурой, быстродействием, потребляемой мощностью и напряжением питания, выпускаемых в различных типах корпусов и в нескольких вариантах исполнения, включая промышленное, военное и радиационно-стойкое. Кристаллы в полной мере реализуют преимущества ПЛИС:

· высокое быстродействие;

· возможность перепрограммирования непосредственно в системе;

· высокая степень интеграции позволяет разместить ЦУУ на одном кристалле и снизить время и затраты на трассировку и производство печатных плат;

· сокращение времени цикла разработки и производства устройства;

Рекомендуемые материалы

· наличие мощных инструментов САПР, позволяющих устранить возможные ошибки в процессе проектирования устройства;

· сравнительно низкая стоимость (в пересчете на один логический вентиль);

· возможность последующей реализации проектов ПЛИС для серийного производства в виде заказных СБИС, что снижает их себестоимость.

|

Рисунок 5.1 – Структура кристалла ПЛИС | До недавнего времени, несмотря на все достоинства ПЛИС Xilinx, существовало обстоятельство сдерживающее их применение (особенно недорогих кристаллов при разработке несерийных устройств) – необходимость дополнительных затрат на приобретение пакета программных средств проектирования и программирования. Чтобы устранить это препятствие, фирма Xilinx предоставила разработчикам возможность использование бесплатного ПО – пакет WebPACK™ ISE™ (Integrated Synthesis Environment). |

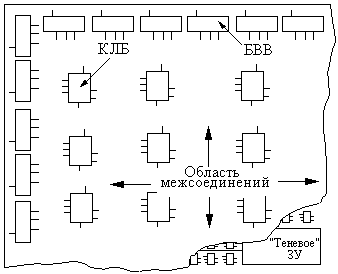

Архитектура ПЛИС. Существует достаточно большое количество МС, отличающихся своей внутренней структурой. Рассмотрим более подробно архитектуру ПЛИС, простейших микросхем фирмы Xilinx. Основной особенностью ПЛИС является наличие трёх типов элементов, конфигурация которых может изменяться разработчиком при проектировании ЦУУ. Этими элементами являются:

· блоки ввода/вывода (БВВ) (IOB – Input/Output Block),

· конфигурируемые логические блоки (КЛБ) (CLB - Configurable Logic Block),

· межсоединения (Intercоnnection).

Общая структура кристалла ПЛИС показана на рисунке 5.1, из которой видно, что БВВ располагаются по периферии кристалла, а КЛБ – в виде матрицы в центре, между ними расположены конфигурируемые межсоединения.

Любой отдельный блок ввода/вывода может быть настроен для выполнения функций буферов: входного, выходного, с тремя состояниями, с запоминанием и других, и обеспечения требуемого вида сопряжения с внешними схемами. Конфигурируемые логические блоки предназначены для выполнения простых логических функций от нескольких переменных, а также функций триггера. Цепи межсоединений служат для формирования сложных логиче-

|

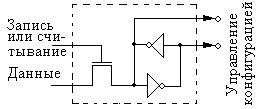

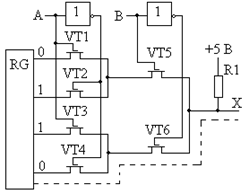

Рисунок 5.2 – Элемент памяти «теневого» ЗУ | ских функций и построения узлов, состоящих из многих КЛБ и БВВ. Логические функции ПЛИС и межсоединения определяются данными, хранящимися во внутренних статических запоминающих элементах («теневом» ЗУ), схема которых приведена на рисунке 5.2, а схема реализации логической функции – на рисунке 5.3. |

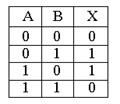

Для реализации требуемой функции в регистр RG (элементы памяти «теневого» ЗУ) записывается нужная информация. Например, для функции «Сумма по модулю два» это 0110. Транзисторы VT1…VT6 переводятся в проводящее состояние напряжением логической 1 на затворе и подключают к выходу Х соответствующие разряды регистра. Если А=0 и В=0, то открыты транзисторы VT4 и VT6. В этом случае сигнал на выходе определяется состоянием четвёртого разряда регистра (на рисунке этот путь показан пунктиром), т.е. Х = 0.

|

Рисунок 5.3 – Реализация фун-кции на МДП-транзисторах в «теневом» ЗУ |

| Полная таблица истинности для данного состояния регистра выглядит следующим образом. Из таблицы следует, что схема в этом |

| случае реализует функцию Х = что соответствует функции «Сумма по модулю два». Для получения другой функции следует записать в регистр RG другую информацию. Программируемые межсоединения в ПЛИС позволяют объединять входы и выходы |

любых БВВ и КЛБ. Все межсоединения представляют собой сетку вертикаль-

ных и горизонтальных металлических сегментов, в местах пересечения которых расположены программируемые переключающие точки (транзисторы – англ. Physical Interconnect Point (PIP) – точка физического межсоединения). PIP позволяют реализовать любой требуемый маршрут цепи и получить для критических цепей задержку менее 0,1 нс. Для разводки по всему кристаллу сигналов с минимальной задержкой служат так называемые длинные линии (ДЛ – англ. LL – Long line) и тактовые буферы.

На кристаллах многих ПЛИС имеется внутренний быстродействующий инвертирующий усилитель, позволяющий с помощью внешнего кварцевого резонатора и двух резисторов создавать кварцевый генератор, используемый в проекте. Схема генератора активизируется в начале загрузки конфигурации, что позволяет стабилизировать генератор. Реальное внутреннее подключение генератора задерживается до завершения загрузки конфигурации.

Отличительной особенностью ПЛИС является возможность перепрограммирования функций КЛБ, БВВ и межсоединений путём перезагрузки во внутреннее («теневое») ЗУ микросхемы (МС) информации о её конфигурации. Это позволяет получать разные устройства на одном и том же кристалле ПЛИС в динамическом режиме, т.е. в течение малого времени и во время работы МС в составе устройства. Автоматическую загрузку информации о конфигурации обеспечивают специальные схемы на кристалле ПЛИС. Исходные данные о конфигурации могут находиться в ПЗУ, установленном на печатной плате рядом с ПЛИС, или в файле на диске.

Эксплуатационные параметры ПЛИС. Гибкая архитектура ПЛИС позволяет создавать различные управляющие устройства с широким спектром возможных параметров по быстродействию, температурному диапазону, напряжению питания, потребляемой мощности и т. п.

Быстродействие ПЛИС обеспечивается применением современной технологии: частота переключения одного триггера в счётном режиме для разных модификаций МС может составлять от 50 до 320 МГц, а время выработки логической функции на КЛБ – от 15 до 1 нс.

Температурный диапазон работы ПЛИС зависит от исполнения: МС в коммерческом исполнении работоспособны при температурах от 0 до +70 °С; в промышленном – от –40 до +85 °С; в военном – от –55 до +125 °С.

Напряжение питания в активном режиме составляет +5,0 или +3,3 В, в пассивном режиме +2,3 В (без потери конфигурации).

Потребляемая мощность ПЛИС, как и всех МС на КМОП-структурах, существенно зависит от типа МС и её номинального напряжения питания, частоты переключения элементов и сложности схемы. Для реальных схем потребляемая мощность одной ПЛИС в динамическом режиме составляет от 0,1 до 4 Вт и более. В статическом режиме, т.е. когда элементы не переключаются, потребляемая мощность ПЛИС составляет единицы милливатт.

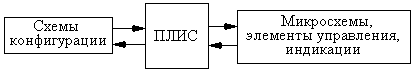

Построение устройств на ПЛИС. К входам и выходам ПЛИС подключаются другие МС, тумблеры, элементы индикации и т.д., составляющие другую часть разрабатываемого устройства (см. рисунок 5.4).

Так как при выключенном питании в ПЛИС не содержится полезной ин-

формации, то основная проблема заключается во вводе в ПЛИС информации о требуемой конфигурации. Существует несколько способов ввода конфигурации в ПЛИС, различающихся количеством задействованных выводов, сложностью управления и т.п.

|

Рисунок 5.4 – Структурная схема устройства, реализованного на базе ПЛИС |

|

Принцип действия ПЛИС. В про стейшем случае процесс конфигурирования ПЛИС осуществляется следующим образом. Предварительно программа конфигурации длиной несколько тысяч бит, автоматически получаемая в результате проектирования устройства, заносится в МС ПЗУ. Затем ПЗУ устанавливается на печатную плату рядом с ПЛИС и соединяется с ней по определённой схеме. После включения питания ПЛИС сама переписывает из ПЗУ в своё «теневое» ЗУ информацию о конфигурации и начинает выполнять заданные при проектировании функции.

Время, необходимое для загрузки программы конфигурации в ПЛИС, зависит от объёма их «теневого» ЗУ и частоты тактового сигнала CCLK, которая, как правило, не должна превышать 2 МГц. Типичное время загрузки 1 бита программы конфигурации составляет 1 мкс. Время конфигурирования составляет от нескольких единиц до нескольких сотен миллисекунд для разных ПЛИС и разных режимов их конфигурирования.

Вопросы для проверки усвоения материала

1. Преимущества ПЛИС.

2. Основные элементы кристалла ПЛИС.

3. Блок ввода/вывода.

4. Конфигурируемый логический блок.

5. Программируемые межсоединения

6. Чем обеспечивается изменение структуры ПЛИС, необходимое разработчику при проектировании конкретного устройства?

7. Назначение и принцип действия «теневого» ЗУ ПЛИС.

8. Структурная схема проекта, реализованного на базе ПЛИС.

9. Эксплуатационные параметры ПЛИС.

10. Принцип действия ПЛИС.

Рекомендация для Вас - Лекция 2.

Литература

1. Мальцев П.П., Гарбузов Н.И., Шарапов А.П., Кнышев Д.А. Программируемые логические ИМС на КМОП-структурах и их применение.1998. –М.: Энергоатомиздат, -159 с. (6-10 с)

2. Зотов В. WebPACK ISE – свободно распространяемый пакет проектирования цифровых устройств на базе ПЛИС фирмы Xilinx. /Компоненты и технологии/ №6, 2001

3. www.plis.ru – сайт с информацией о САПР и ПЛИС фирмы Xilinx.

4. www.xilinx.ru – сайт с информацией о САПР и ПЛИС фирмы Xilinx.

5. www.inlinegroup.ru – сайт с информацией о САПР и ПЛИС фирмы Xilinx.

*B + А

*B + А

,

,