мультиплексоры (1067234), страница 2

Текст из файла (страница 2)

jgero^pjjoj^^ojWTO-gMeTHWttoc^jtoflOB. Функционирование дешифратора двоично-десятичного кода (Д-кода) с весами разрядов I 8-4-2-1 определяется системой логических функций: :

10 •

(5)

Дешифратор имеет 4 входа и *0 выходов, т.е. является неполным. Неиспользуемые, т.е. запрещенные, наборы входных сигналов используются для минимизации системы функций (5). В качестве примера на рис. 9 и Ю приведены карты Вейча, на которых соответственно отражены функции /J. и ^ .

Рис, 9 Рис. Ю

Знаками "х" отмечены клетки неиспользуемых наборов переменных

Аналогично можно получить зсе выходные функции:

А>о • ^i • Ч? » ■ ^3 . Минимизируя функции /^- и f~f с учетом неиспользуемых наборов переменных, получим: '

(б)

Каждый вид Д-кода имеет свои неиспользуемые наборы входных переменных. Кодирование десятичных цифр в различных Д-кодах поясняет табл. 2.

12

- Таблица 2

: Задание и порядок выполнения работы

1. Исследование линейного двухвходового дешифратора с

инверсными выходами:

а) собрать линейный стробируемый дешифратор на элементах

ЗИ - НЕ; наборы входных сигналов Ао , А/ задать с выходов

Qo , Qi четырехразрядного счетчика на УК-г- триггерах (см. рис. И, а,б); подключить световые индикаторы к выходам триггеров и дешифратора;

б) подать на вход счетчика сигнал с выхода генератора

ОДИНОЧ. ИШ1.; изменяя состояние счетчика, составить таблицу

истинности нестробируемого дешифратора (т.е. при Е - I);

в) подать на вход счетчика сигналы СИ-I _ГТ_ и снять

временные диаграммы сигналов дешифратора;

г) определить амплитуду помех, вызванных гонками, на вы

ходах дешифратора;

д) снять временные диаграммы сигналов стробируемого дешиф

ратора; в качестве стробирующего сигнала использовать сигнал

СИ-I ~LJ~ , задержанный линией задержки лабораторного макета

УМ-П;

е) определить время задержки, необходимое для исключения

помех на выходах дешифратора, вызванных гонками.

2. Исследование дешифратора двоично-десятичного кода:

а) составить таблицу истинности дешифратора Д-кода, номер •

которого в табл. 2 задается преподавателем;

б) провести синтез дешифратора Д-кода;

в) собрать линейный дешифратор Д-кода на элементах И - НЕ;

входные сигналы Ас- и At- задать с выходов <?с- и ^четырех

разрядного счетчика на У/с -триггерах (см. рис. И);

г) подать на вход счетчика сигналы СИ-I __П_ ;

д) снять временные диаграммы сигналов дешифратора;

е) используя временные диаграммы входных и выходнчк сигна

лов, проверить соответствие работы дешифратора его тябхипе ис

тинности. ) . . '

Примечете^ Допускается собирать часть схемы дети^эпто!:^ для трех или четырех выходов.

3. Исследование дешифраторов ИМС К155ИД4 (см. рис. Ь):

а) снять временные диаграммы сигналов двухтсодоэого де>: лЪ-ратора, подавая на его адресные входы сигналы Qo и Qy с в> годов счетчика (см. рис. И), а на стробирувдие входы S? и <f> -

13

импульсы СИ-1 —П—, задержанные линией задержки макета;

импульсы СИ-1 —П—, задержанные линией задержки макета;

б) определить время задержки стробируюшего сигнала, необ

ходимое для исключения помех на выходах дешифратора;

в) собрать схему трехвходового дешифратора на основе де

шифратора К155ИД4 (см. рис. 8), задавая входные сигналы Ао ,

Aj , .Ар Q выходов Qo> Qt i Qo с*?етчика (рис. И); снять временные диаграммы сигналов дешифратора и составить по ней таблицу истинности.

Ю Рис. И

4. Исследовать работоспособность дешифраторов ИМС 533ИД7 (рис. 12):

а) собрать стробируемый дешифратор на четыре входа на осно

ве двух ИМС 533ИД7;

14 '

б) снять временные диаграммы сигналов дешифратора, подавая на его адресные входы сигналы Qo , Qy , Ог , Qg с выходов счетчика Сем. рис. II), а на стробиругаий вход - импульсы СИ-1 _T~L_ • задержанные линией задержки макета.

5. Составить отчет.

Требования к отчету

v |T Рис. 12

Отчет должен содержать электрические функциональные схемы, таблицы истинности, временные диаграммы сигналов исследуемых дешифраторов, результаты измерений параметров выходных сигналов дешифраторов.

Контрольные вопросы

Я. Что называется дешифратором?

-

Какой дешифратор называется полным (неполным)?

-

Определите закон функционирования дешифратора аналити

чески и таблично. -

Поясните основные способы построения дешифраторов.

-

Что называется гонками и как они устраняются?

-

Каковы способы наращивания дешифраторов по количеству

входов и выходов и как они реализуются схемотехнически? -

Объясните схему включения дешифратора-демультиплексора.

-

Поясните методику синтеза неполных дешифраторов.

Работа № 2. ИСОЩЦОВАНИЕ МУЛЬТИПЛЕКСОРОВ

Цель работы - изучение принципов построения и практического применения, макетирование и экспериментальные исследования мультиплексоров.

Самостоятельная работа студента включает изучение принципов построения мультиплексоров и подготовку индивидуального задания. Перед началом работы преподаватель проводит собеседование, целью которого является проверка теоретической и практической подготовленности студента к лабораторной работе. Студент должен подготовить отчет по каждому пункту раздела "Задание и порядок выполнения работы" и знать методику выполнения каждого пункта задания. После выполнения работы студент обязан предста-

. -15

вить на проверку преподавателю оформленный индивидуальный

вить на проверку преподавателю оформленный индивидуальный

отчет.

Продолжительность работы - 4ч.

Теоретические сведения

Мультиплексор - это функциональный узел, имеющий /?, адресных и гп = 2 п информационных входов и выполнявший коммутацию сигнала на выход с того информационного входа, адрес которого установлен на адресных входах.

Мультиплексор реалиэу_ет логическую функцию

(7)

где А- - адресные входа и сигналы, t =• 0,1...,/?- I; -Z^' -информационные входы и сигналы, J ■ 0,1..., 2 п- I; К- - кон-ституента I, т.е. конъюнкция всех аргументов, номер которой равен числу, образованному двоичным кодом сигналов на адресных

входах.

Такой мультиплексор называется мультиплексором с прямым выходом. Выход мультиплексора может быть инверсным. Тогда на этом выходе реализуется функция У . Некоторые разновидности интегральных схем (ИС) мультиплексоров имеют как прямой, так и инверсный выходы.

Мультиплексор может иметь вход стробирования С . Стробиру-емый мультиплексор выполняет логическую Функцию

(8)

Вход стробирования можно использовать для устранения ложных сигналов на выходе мультиплексора, возникающих при переключении' его логических элементов, а также в качестве дополнительного адресного входа при наращивании мультиплексора.

ИС мультиплексоров строятся пб линейной схеме в соответст

вии с (7) или (8). Вариант реализации мультиплексора с четырех

входных линий на одну выходную линию (4-1) и его условное

графическое обозначение (УГО) приведены на рис 13, а,б соот

ветственно. Мультиплексор состоит из дешифратора, каждый конъ-

юнктор которого имеет дополнительный вход для соответствующего

информационного сигнала Д. Выходы конъюнкторов объединяются -

по операции ИЛИ дизъюнктором. Время задержки распространения

сигнала в мультиплексоре определяется задержкой цепи последо

вательно соединенных элементов НЕ, И, ИЛИ.

-16 -

4 Рис. 13

мультиплексоры широко применяются для построения:

-

коммутаторов-селекторов цифровых ..сигналов; : ~~-

-

постоянных запоминающих устройств емкостью 2 х £ бит;

-

комбинационных схем, реализующих логические функции;

-

преобразователей кодов (например, параллельного кода в

последовательный или кода с одними весами разрядов в код с дру

гими весами разрядов) и других узлов.

Ha^a^fflaKHejggbjrHjjj^KjMga^. ЧЗ^робируёмыеГ'мультй*^ илексоры можно использовать для построения ZKm -•канального мультиплексора. В общем случав для этого требуется З^л^-ка-йальных стробируемых мультиплексоров, дешифратор с К входами л 2* выходами и 2 *"-входовой логический элемент ИДИ.

(9)

(-10) (Ю),

-17

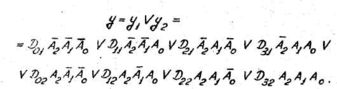

Рассмотрим построение 8-канального мультиплексора на основе 1-канального стробируемого мультиплексора. Для получения 8-ка-кального мультиплексора требуется два 4-канальных стробируемых мультиплексора- Цулииплексоры I и 2 выполняют логические функции:

Полагая С, = А„ и Cj =/4^, и логически суммируя IV) и получим

Электрическая функциональная схема 8-канального мультиплексора приведена на рис. 14. При Аг ■ • 0 происходит выбор (стробирование) мультиплексора MS1 , при Аг * 1 - мультиплексора MS 2. ' .

Рис. 14

Мультиплексоры, иыеющие три состояния на выходах, допускают непосредственное объединение внходов. Таким образом исключается элемент ИЛИ. Вход разрешения £ используется при атом как атрофирующий.

т -канального стробируемого мультиплексора {гп'ш 2") можно реализовать любую функцию отп +1 логических переменных.

Примечание. Реализация функций п переменных нат -канальном мультиплексоре тривиальна и основана на использовании только его адресных входов.

Пример. Синтезировать комбинационную схему (КС), выполня

ющую функцию у (JCj, jcp , зс^ , jx^ ), заданную диаграммой Вейча

(рис. 15), на основе 8-канального мультиплексора. Минимальная

дизъюнктивная нормальная форма (МДНФ) функции,/ (-x-y,jc~, ас , лс^)

имеет два представления: ■ ■ ■ . ■ .

18 .."■■'■•

ионовной задачей синтеза по на мультиплексорах является оптимальный выбор переменных, подаваемых х на его адресные входы, так как сложность ~—т—i—i— .

функций К: , а значит, и КС в общем слу- Х2 — — —