Функциональные узлы последовательностного типа

3.функциональные узлы последовательностного типа (автоматы с памятью)

3.1.Триггеры (элементарные автоматы). Классификация. Основные сведения

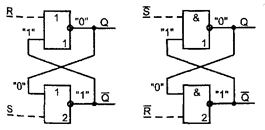

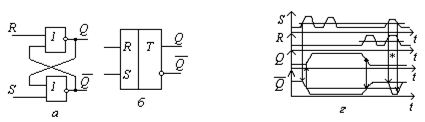

Триггеры — элементарные автоматы, предназначенные для записи и хранения 1 бита информации. Они состоят из элемента памяти (фиксатора) и схемы управления. Фиксатор строится на двух инверторах, связанных друг с другом "накрест", так что выход одного соединен с входом другого. Такое соединение дает цепь с двумя устойчивыми состояниями (рис. 3.1.). Действительно, если на выходе инвертора 1 имеется логический ноль, то он обеспечивает на выходе инвертора 2 логическую единицу, благодаря которой сам и существует. То же согласование сигналов имеет место и для второго состояния, когда инвертор 1 находится в единице, а инвертор 2 — в нуле. Любое из двух состояний может существовать неограниченно долго.

а б

Рис.3.1. Схемы элементов памяти(фиксаторов) со входами управления: а) на элементах ИЛИ-НЕ; ) на элементах И-НЕ

Чтобы управлять фиксатором, нужно иметь, как минимум, в логических элементах дополнительные входы. Обычно схемы управления триггером сложнее. На входы управления поступают внешние установочные сигналы для записи в триггер логического 0 или 1. Установочные сигналы показаны на рис. 3.1 штриховыми линиями. Буквой R латинского алфавита (от Reset) обозначен сигнал установки триггера в ноль (сброса), а буквой S (от Set) — сигнал установки в состояние логической единицы (установки). Состояние триггера считывается по значению прямого выхода, обозначаемого как Q. Обычно триггер имеет и второй выход с инверсным сигналом  Для фиксатора на элементах ИЛИ-НЕ установочным сигналом является единичный, поскольку только он приводит логический элемент в нулевое состояние независимо от сигналов на других входах элемента. Для фиксатора на элементах И-НЕ установочным сигналом является нулевой, как обладающий тем же свойством однозначно задавать состояние элемента независимо от состояний других входов.

Для фиксатора на элементах ИЛИ-НЕ установочным сигналом является единичный, поскольку только он приводит логический элемент в нулевое состояние независимо от сигналов на других входах элемента. Для фиксатора на элементах И-НЕ установочным сигналом является нулевой, как обладающий тем же свойством однозначно задавать состояние элемента независимо от состояний других входов.

Классификация триггеров

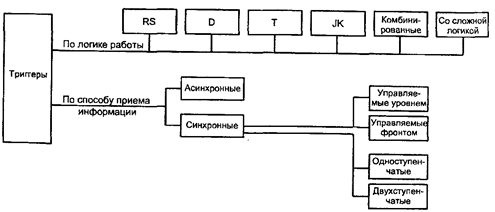

Классификация триггеров проводится по признакам логического функционирования и способу записи информации (рис. 3.2).

Рис.3.2.Классификация наиболее распространенных триггеров

Рекомендуемые материалы

По логическому функционированию или типу управляющих информационных входов различают триггеры типов RS, D, Т, JK и др. Кроме того, используются комбинированные триггеры, в которых совмещаются одновременно несколько типов, и триггеры со сложной входной логикой (группами входов, связанных между собой логическими зависимостями).

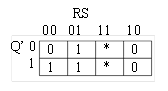

Триггер типа RS имеет два информационных входа — установки в единицу (S) и установки в ноль(R ), его таблица истинности представлена в таб.3.1. Этой таблице соответствует схема на элементах ИЛИ—НЕ (рис.3.1 а).

Таблица 3.1. Таблица истинности RS-триггера

| R | S | Q |

| Режим |

| 1 | 0 | 0 | 1 | Запись 0 |

| 0 | 1 | 1 | 0 | Запись 1 |

| 0 | 0 | Q’ |

| Хранение |

| 1 | 1 | * | * | Запрещенное |

Одновременная подача сигналов установки S и сброса R не допускается (эта комбинация сигналов называется запрещенной). Q’ и  ’ – значения выходов, которые были установлены предыдущими входными сигналами. Для RS-триггера, реализованного на элементах И-НЕ и имеющего инверсные R и S входы (рис.3.1 б), сигналами установки является 0, а не 1. Его таблица истинности представлена в таб.3.2.

’ – значения выходов, которые были установлены предыдущими входными сигналами. Для RS-триггера, реализованного на элементах И-НЕ и имеющего инверсные R и S входы (рис.3.1 б), сигналами установки является 0, а не 1. Его таблица истинности представлена в таб.3.2.

Таблица 3.2. Таблица истинности

-триггера

-триггера

|

|

| Q |

| режим |

| 0 | 1 | 0 | 1 | Запись 0 |

| 1 | 0 | 1 | 0 | Запись 1 |

| 1 | 1 | Q’ |

| хранение |

| 0 | 0 | * | * | Запрещенное |

Триггер типа D (от слова Delay — задержка) имеет один информационный вход. Его состояние Q повторяет входной сигнал D (Q=D), но с задержкой, определяемой тактовым сигналом.

Триггер типа Т изменяет свое состояние на противоположное (Q =  ’) при поступлении входного сигнала T. Имеет один вход T, называется триггером со счетным входом или счетным триггером.

’) при поступлении входного сигнала T. Имеет один вход T, называется триггером со счетным входом или счетным триггером.

Триггер типа JK универсален, имеет входы установки (J) и сброса (К), подобные входам триггера RS. В отличие от последнего, допускает ситуацию с одновременной подачей сигналов на оба эти входа (J = К = 1). В этом режиме работает как T-триггер относительно синхровхода (C играет роль Т).

В комбинированных триггерах совмещаются несколько режимов. Например, триггер типа RST — счетный триггер, который дополнительно имеет входы установки и сброса.

Примером триггера со сложной входной логикой служит JK-триггер с группами входов J1J2J3 и К1К2К3, соединенными операцией конъюнкции: J= J1J2J3 , K= К1К2К3.

По способу записи информации различают асинхронные (нетактируемые) и синхронные (тактируемые) триггеры. В нетактируемых триггерах переход в новое состояние вызывается непосредственно изменениями входных информационных сигналов. В тактируемых триггерах есть специальный вход синхронизации, переход триггера в новое состояние происходит только при подаче на этот вход разрешающих тактовых сигналов. Тактовые сигналы называют также синхронизирующими. Обозначается синхровход буквой С (от слова Clock).

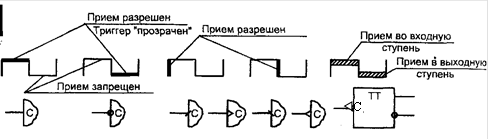

По способу восприятия тактовых сигналов триггеры делятся на управляемые уровнем и управляемые фронтом. Управление уровнем означает, что на всем интервале времени пока действует разрешающий уровень тактового сигнала триггер воспринимает входные информационные сигналы и реагирует на них, а при запрещающем уровне — не воспринимает информационные сигналы и остается в неизменном состоянии . При управлении фронтом синхросигнала разрешение на переключение триггера дается только в момент перепада тактового сигнала (на его фронте или спаде). В остальное время независимо от уровня тактового сигнала триггер не воспринимает входные информационные сигналы и остается в неизменном (после последнего переключения) состоянии. Триггеры, управляемые фронтом, называют также триггерами с динамическим управлением.

Динамический вход может быть прямым или инверсным. Прямое динамическое управление означает разрешение на переключение триггера при изменении тактового сигнала с нулевого значения на единичное, инверсное — при изменении тактового сигнала с единичного значения на нулевое.

По характеру процесса переключения триггеры делятся на одноступенчатые и двухступенчатые.

В одноступенчатом триггере переключение в новое состояние происходит сразу, а в двухступенчатом — по этапам. Двухступенчатые триггеры состоят из входной и выходной ступеней. Переход в новое состояние происходит в обеих ступенях поочередно. Один из уровней тактового сигнала разрешает прием информации во входную ступень при неизменном состоянии выходной ступени. Другой уровень тактового сигнала наоборот разрешает передачу нового состояния из входной ступени в выходную , а входная ступень сохраняет состояние, в которое она была переведена последним изменением входных информационных сигналов (когда прием в нее был разрешен). Триггеры, управляемые уровнем синхросигнала, всегда строятся по одноступенчатой схеме, а триггеры, управляемые фронтом синхросигнала, как правило, строятся по двухступенчатой схеме.

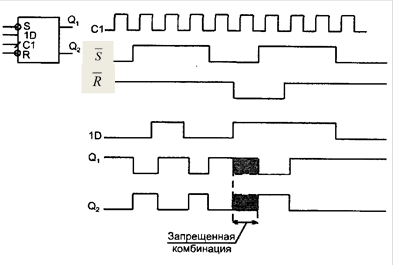

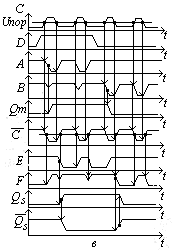

На рис. 3.3 показаны процессы, происходящие в синхронных (тактируемых) триггерах. На диаграммах тактовых импульсов отмечено содержание процессов на отдельных этапах, под диаграммами даны обозначения соответствующих типов синхровходов.

|

Рис.3.3. Временные диаграммы, поясняющие работу синхровходов разных типов в триггерах, и их условные графические изображения

В практике проектирования используется термин "триггер-защелка" (Latch). Под этим понимается триггер, который прозрачен при одном уровне тактового сигнала и переходит в режим хранения (фиксирует свое последнее состояние) при другом уровне. Таким свойством обладают все триггеры, управляемые уровнем синхросигнала, но практически в качестве «защелок» применяются D-триггеры.

Как видно из рис. 3.3, двухступенчатый триггер обозначается двумя буквами ТТ. Двухступенчатые триггеры часто называют также триггерами типа MS (от английского Master-Slave, т. е. хозяин — раб). Эта аббревиатура отражает характер работы триггера: входная ступень вырабатывает новое значение выходной переменной Q, а выходная его копирует.

На рис. 3.4 и показаны временные диаграммы, иллюстрирующие реакцию триггеров D разных типов на одинаковые входные воздействия.

Рис. 3.4. Временные диаграммы работы триггеров с разными типами синхровходов.

Среди комбинированных триггеров наиболее распространены те, у которых специфические информационные входы, синхронизирумые сигналом С, комбинируются с асинхронными R и S входами. В этом случае асинхронные входы установки и сброса являются доминирующими, при их действии сигналы на других входах игнорируются. Асинхронные R и S входы удобны для быстрой установки триггеров в конкретное состояние в начале или в процессе работы устройства. Как следует из названия, время появления сигналов R и S или  и

и  может быть любым. Как только эти сигналы получают значения, соответствующие режиму хранения (R=S=0 или

может быть любым. Как только эти сигналы получают значения, соответствующие режиму хранения (R=S=0 или  =

= =1), то дальше триггер из принудительно установленного состояния будет переключаться в соответствии с сигналами на его информационных и синхро- входах (например, на D- и С – входе для триггера RSD). Временные диаграммы, иллюстрирующие работу RSD – триггера приведены на рис.3.5.

=1), то дальше триггер из принудительно установленного состояния будет переключаться в соответствии с сигналами на его информационных и синхро- входах (например, на D- и С – входе для триггера RSD). Временные диаграммы, иллюстрирующие работу RSD – триггера приведены на рис.3.5.

|

Рис.3.5. Условное графическое обозначение и временные диаграммы D

–триггера с синхронизацией по переднему фронту С.

–триггера с синхронизацией по переднему фронту С.

Времена предустановки и выдержки

С синхронизацией (тактированием) триггера связаны два важных параметра — время предустановки tSU (Set-Up Time) и время выдержки tH (Hold Time). Важность этих параметров обуславливается еще и тем, что они свойственны не только триггерам, но и другим устройствам. Время tSU — это интервал до поступления разрешающего фронта синхросигнала, в течение которого информационный сигнал должен оставаться неизменным (рис. 3.4). Для триггеров с динамическим управлением— это время необходимое для надежного переключения нижней ступени двухступенчатого триггера. Для триггеров, управляемых уровнем синхросигнала, в которых предусматривается однократное переключение триггера в соответствии с уровнем информационного сигнала, tSU так же необходимо для установления правильных значений сигналов в элементах управляющей схемы перед подачей их на элементы фиксатора. Время выдержки tH — это время после поступления разрешающего фронта синхросигнала, в течение которого информационный сигнал должен оставаться неизменным. Для триггеров с динамическим управлением — это время необходимое для перехода нижней ступени в режим хранения и блокирования информационных входов. Для триггеров, управляемых уровнем синхросигнала в режиме однократной записи входной информации за время действия разрешающего уровня синхросигнала, значение информационного сигнала не должно меняться на протяжении всего временного интервала, пока запись в триггер разрешена. Когда допустим прозрачный режим работы триггера (многократное его переключение как реакция на многократное изменение информационного сигнала на интервале разрешения), тогда понятия tSU и tH для триггеров, управляемых уровнем синхросигнала, теряет смысл.

Таким образом , соблюдение времен предустановки и выдержки обеспечивает правильное восприятие триггером входной информации.

Рис. 3.4. Параметры триггеров: время предустановки и время выдержки.

Ряд других временных параметров триггеров непосредственно связан с задержками сигнала при прохождении через триггер и не требует специальных пояснений.

3.2. Схемотехника триггерных устройств

3.2.1 RS-триггер

Схема .RS-триггеров составляет основу для построения других триггерных схем, таких, как T-, D- и JK-триггеры.

Если записать таблицу истинности RS-триггера в виде карты Карно и доопределить запрещенные значения сигналов на выходах логическими 1-ми, получим характеристическое уравнение 3.1.

|

Q= S + Q’

S + Q’ =S + Q’

=S + Q’ (3.1)

(3.1)

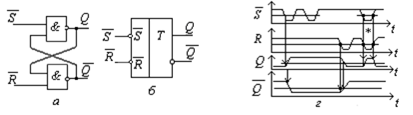

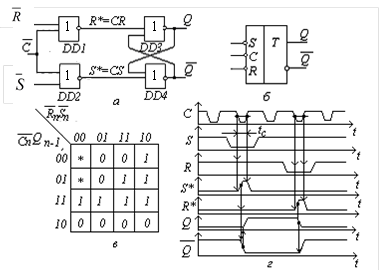

На рис. 3.5 приведена реализация RS-триггера на элементах ИЛИ—НЕ (см. таблицу истинности таб.3.1)., а на рис. 3.6. – на элементах И—НЕ (см. таблицу истинности таб.3.2).

|

Рис. 3.5 RS-триггера на элементах ИЛИ—НЕ : а) функциональная схема; б)условное графическое изображение; г) временные диаграммы работы

На условном графическом изображении (рис. 3.6,6) кружки на входах R, S показывают, что данный RS-триггер управляется инверсными сигналами (см. таблицу истинности таб.3.2).

|

Рис. 3.6. RS-триггера на элементах И—НЕ : а) функциональная схема; б)условное графическое изображение; г) временные диаграммы работы

Наиболее полное представление о работе триггеров дают временные диаграммы (рис. 3.5,г, 3.6,г), которые описывают не только значения выходных уровней в любой момент времени, но и длительности фронтов tф01 , tф10 , задержек и последовательность переключения логических элементов. Из временных диаграмм видно, что длительность переключения tпер и минимальная длительность входного сигнала данных tвх.min для асинхронных RS-триггеров определяются средним временем задержки сигнала в логических элементах

tзд.р.ср.=0.5( tзд.р01+ tзд.р10 )

tпер= tвх.min=2tзд.р.ср. (3.2.)

На временных диаграммах символом (*) помечены интервалы воздействия на входы RS-триггеров запрещенных комбинаций информационных сигналов. При этом в триггере на элементах ИЛИ—НЕ устанавливаются выходные уровни Q = 0,  = 0, а в триггере на элементах И—НЕ — Q = 1,

= 0, а в триггере на элементах И—НЕ — Q = 1,  =1. Состояние, принимаемое RS-триггером по окончании действия запрещенной комбинации, зависит от того, какой из управляющих сигналов длится дольше. Если на входах появится комбинация 01 или 10, триггер перейдет в состояние, соответствующее этой комбинации. При строго одновременном переключении сигналов на входах R и S в комбинацию, соответствующую режиму хранения, и при одинаковых значениях задержек элементов их выходы будет постоянно переключаться в противоположные состояния, т.е. триггер превратится в генератор. На практике всегда имеет место случайный разброс задержек логических элементов, поэтому триггер всё же перейдет в какое-то из устойчивых состояний (0 или 1).

=1. Состояние, принимаемое RS-триггером по окончании действия запрещенной комбинации, зависит от того, какой из управляющих сигналов длится дольше. Если на входах появится комбинация 01 или 10, триггер перейдет в состояние, соответствующее этой комбинации. При строго одновременном переключении сигналов на входах R и S в комбинацию, соответствующую режиму хранения, и при одинаковых значениях задержек элементов их выходы будет постоянно переключаться в противоположные состояния, т.е. триггер превратится в генератор. На практике всегда имеет место случайный разброс задержек логических элементов, поэтому триггер всё же перейдет в какое-то из устойчивых состояний (0 или 1).

Для устранения неоднозначности реакции RS-триггера на одновременное воздействие сигналами установки на входы R и S необходимо оговорить состояние, в которое RS-триггер должен перейти. По реакции на запрещенную для RS-триггера комбинацию входных сигналов различают S-триггеры (переключаются в единичное состояние), R-триггеры (переключаются в нулевое состояние) и E-триггеры (от Exclusive, сохраняют предыдущее состояние).

Рис. 3.7. R-триггер на элементах И—НЕ a) функциональная схема;б) временные диаграммы работы.

Схема реализации R-триггера в базисе И—НЕ и временные диаграммы его работы приведены на рис. 3.7. К схеме обычного RS – триггера добавлена обратная связь с выхода элемента DD2 на вход логического элемента DD1. Когда S =R=1 выход DD2, на котором устанавливается  = 0 , блокирует остальные входы элемента DD1 и устанавливает на его выходе логическую «1». Поэтому комбинация S=R=1 устанавливает триггер в состояние «0». Как видно из временных диаграмм (рис. 3.7,6), дополнительные логические элементы DD1 и DD2 увеличивают время переключения R -триггера и минимальную длительность входного сигнала по сравнению с выражением 3.2.:

= 0 , блокирует остальные входы элемента DD1 и устанавливает на его выходе логическую «1». Поэтому комбинация S=R=1 устанавливает триггер в состояние «0». Как видно из временных диаграмм (рис. 3.7,6), дополнительные логические элементы DD1 и DD2 увеличивают время переключения R -триггера и минимальную длительность входного сигнала по сравнению с выражением 3.2.:

tпер= tвх.min=3tзд.р.ср. (3.3)

На рис. 3.8. показана схема S-триггера в базисе И—HE . Обратная связь с выхода элемента DD1 на вход элемента DD2 обеспечивает приоритет входу S, так как на вход DD2 поступает уровень  = 0 , который для логического элемента И—НЕ является доминирующим и устанавливает на выходе элемента DD2 логическую «1» .

= 0 , который для логического элемента И—НЕ является доминирующим и устанавливает на выходе элемента DD2 логическую «1» .

Рис. 3.8 S-триггер на элементах И—НЕ a) функциональная схема;б) временные диаграммы работы.

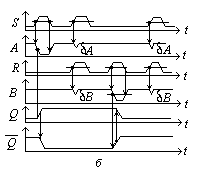

Схема, реализующая E-триггер в базисе логических элементов И—НЕ, и его временные диаграммы показаны на рис. 3.9. Дополнительные инверторы DD5, DD6 при S=R=1 блокируют сигналами  = 0 и

= 0 и  =0 логические элементы DD1, DD2, на выходах которых при этом устанавливаются уровни «логической 1», что соответствует режиму хранения ранее записанной информации.

=0 логические элементы DD1, DD2, на выходах которых при этом устанавливаются уровни «логической 1», что соответствует режиму хранения ранее записанной информации.

Рис. 3.9. Е-триггер на элементах И—НЕ a) функциональная схема; б) временные диаграммы работы.

Вследствие задержки блокирующих сигналов инверторами DD5, DD6 на выходах вентилей DD1, DD2 формируются сигналы помехи дA, дВ, аналогично помехам в асинхронных триггерах типа R и S. Помехи на управляющих входах при определенных условиях могут привести к ложному срабатыванию триггеров на элементах DD3 и DD4.

Для устранения ложных срабатываний в R-, S- и Е-триггере необходимо синхронизировать их серией импульсов С. Для этого в схемах (рис. 3.7, 3.8, 3.9) предусматривается дополнительный вход С (показан штриховой линией). Разрешающие уровни синхросигналов должны поступать с некоторой задержкой tSU относительно изменения информационных сигналов R и S, чтобы оба входа до разрешения записи успевали гарантированно переключиться. В Е-триггере разрешение С необходимо включать с задержкой на время переключения DD5, DD6 . В R-, S- триггерах – после включения разрешения С будет переключаться только один из элементов DD1 или DD2.

Таким образом, получают варианты синхронных R-, S- и Е-триггеров, которые обладают более высокой надежностью, но и большим разрешающим временем вследствие необходимой дополнительной задержки синхроимпульсов на время возникновения помехи.

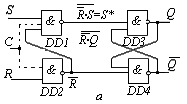

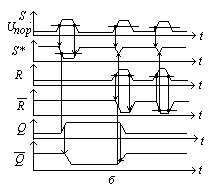

Помимо борьбы с помехами режим синхронизации RS-триггеров широко используется при построении синхронных цифровых устройств. Для обеспечения синхронизируемого режима работы обычные асинхронные RS-триггеры должны быть дополнены схемами синхронизации. На рис. 3.10. и 3.11. показана реализация синхронных RS-триггеров соответственно в базисе логических элементов ИЛИ—НЕ и И—НЕ. Схемы синхронизации построены на логических элементах DD1, DD2 и формируют сигналы R*, S*, управляющие состоянием асинхронных RS-триггеров на логических элементах DD3, DD4. Информация, поступающая на входы S и R, как видно из временных диаграмм, воспринимается только на интервале действия разрешающих синхроимпульсов С длительностью tс.В остальное время триггер находится в режиме хранения ранее записанной информации.

|

Рис. 3.10 Синхронный RS-триггер на элементах ИЛИ—НЕ:а)функциональная схемы; б) условное графическое изображения; в) карта Карно; г) временные диаграммы работы

Рис. 3.11. Синхронный RS-триггер на элементах И—НЕ:а)функциональная схемы; б) условное графическое изображения; в) карта Карно; г) временные диаграммы работы

Все изменения информационных сигналов R и S ( ,

, ) в интервале tс передаются на вход асинхронного триггера на логических элементах DD3, DD4 и вызывают переключение его состояний (прозрачный режим асинхронной записи), что характерно для всех схем синхронизируемых уровнем. Запрещенной, аналогично асинхронным триггерам, является комбинация входных сигналов C=R=S=1 (

) в интервале tс передаются на вход асинхронного триггера на логических элементах DD3, DD4 и вызывают переключение его состояний (прозрачный режим асинхронной записи), что характерно для всех схем синхронизируемых уровнем. Запрещенной, аналогично асинхронным триггерам, является комбинация входных сигналов C=R=S=1 ( =

= =

= =0 ), обусловливающая установку на прямом и инверсном выходах уровней Q=

=0 ), обусловливающая установку на прямом и инверсном выходах уровней Q= =0 в триггере (рис 3.10,а), а в триггере (рис. 3.11,а) Q=

=0 в триггере (рис 3.10,а), а в триггере (рис. 3.11,а) Q= =1. Такая ситуация еще называется « разрыв внутренних связей», поскольку они не оказывают влияния на выходные сигналы триггера.

=1. Такая ситуация еще называется « разрыв внутренних связей», поскольку они не оказывают влияния на выходные сигналы триггера.

В RS-триггерах, синхронизируемых фронтом (динамических), отсутствует режим прозрачной асинхронной записи. Информационные сигналы S и R могут переключаться многократно, но триггер переключается в состояние, соответствующее комбинации входных сигналов S и R непосредственно перед разрешающим положительным (или отрицательным) фронтом синхроимпульса.

Для построения динамических триггеров любых типов наиболее часто используются 3 типа схемных решений:

· 6-элементная схема;

· 2-х ступенчатая схема;

· схема "с запрещающими связями" .

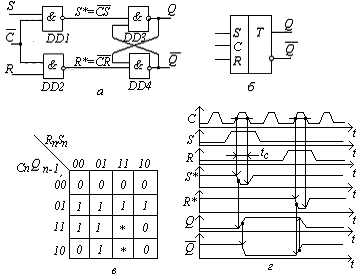

Так называемая 6-элементная схема синхронизации фронтом принципиально включает запоминающий элемент, который в течение времени tc действия синхроимпульса обеспечивает управление состоянием асинхронного RS-триггера. В синхронизируемых фронтом RS-триггерах (рис. 3.12) схемы синхронизации триггеров фронтом построены на логических элементах DD1—DD4 типа ИЛИ—НЕ (а) или И—НЕ (в). RS-триггер на элементах ИЛИ—НЕ синхронизируется отрицательным фронтом, на элементах И—НЕ — положительным фронтом. Пунктирной линией на схеме показан принцип подключения RS- входов для асинхронной установки/сброса в начальное состояние (независимо от тактируемых информационных входов и самого входа синхронизации).

| |||

|

|

Рис. 3.12. RS-триггер с динамическим управлением ( 6-элементная схема): а) схема на элементах ИЛИ—НЕ; б) ее условное графическое обозначение; в) схема на элементах И—НЕ ; г) ее условное графическое обозначение

Рассмотрим работу схемы на элементах ИЛИ—НЕ (рис. 3.12,а). Когда C=I на выходах элементов DD3 и DD4 поддерживаются уровни «логического 0», что обеспечивает режим хранения для асинхронного триггера DD5. Входы S и R на состояние DD3, DD4 влияния не оказывают, так как уровень С = 1 является доминирующим. Пусть непосредственно перед отрицательным фронтом синхроимпульса на информационных входах установилась комбинация входных сигналов S = 1, R =0 (т.е. выход DD1=0, а выход DD2=1). Тогда при переключении входа С из «1» в «0» на выходе DD4 сохраняется «0»,а на трех входах элемента DD3 имеем «0», что приводит к установлению на его выходе уровня «1».Эта «1» подается на входы DD1 и DD4, блокируя переключение их внешними сигналами. Поэтому в течение времени tс действия уровня C = 0 триггер не реагирует на переключения управляющих входов S и R . Так как на входах DD5 и DD6 имеем S = 1, R =0 , то триггер устанавливается в состояние «1». Аналогично происходит установка триггера в состояние «0». Комбинация сигналов S = R = 1 по прежнему является запрещенной, поскольку в этом случае по отрицательному фронту синхроимпульса происходит состязательное переключение триггера на элементах DD3, DD4 в одно из двух возможных состояний, которое автоматически переписывается в триггер DD5. В случае, когда S=R=0 (режим хранения), на выходе DD1 установится состояние инверсное DD3, а на выходе DD2 – инверсное DD4. То есть состояние DD3 и DD4 не меняется, следовательно и DD5 также остаётся в прежднем состоянии.

Следует однако отметить, что для правильной работы схемы в этом режиме смену входных сигналов S и R можно производить только при С=1, иначе, возможен режим сквозного управления, когда триггер от смены сигналов S и R будет переключаться асинхронно. Это происходит тогда, когда перед задним фронтом С было DD3= DD4 =0, а после заднего фрота С при S=R=0 эти значения сохранятся. Но в таком случае после заднего фронта С блокировки входов S и R будет отсутствовать (на обратных связях нет ни одной «1»), и все изменения сигналов S и R при С=0 будут свободно записываться в DD3, DD4, а затем – в DD5.

Аналогично построен и функционирует синхронизируемый положительным фронтом RS-триггер на элементах И—НЕ (рис. 3.12,в). Полярность синхронизирующего фронта на условном графическом обозначении (рис. 3.12,б, г) показана косой линией на входе С.

Длительность переключения tпер и минимальная длительность входного сигнала tвх.min для синхронизируемых уровнем и фронтом RS-триггеров одинакова и составляет :

tпер = tвх.min = 3tзд. р. ср , (3.4.)

где tзд. р. ср, — средняя задержка распространения одного вентиля.

Другой разновидностью динамической реализации являются двухступенчатые схемы. Прием информации во входную и выходную ступени разрешается поочередно. Следствие этого — практически нулевое время выдержки tH, необходимое для блокировки информационных входов после разрешающего фронта синхросигнала, что позволяет реализовать любые типы триггеров без опасных временных состязаний. В то же время схемы этих триггеров более сложные, чем 6 -элементные схемы, а их быстродействие несколько ниже.

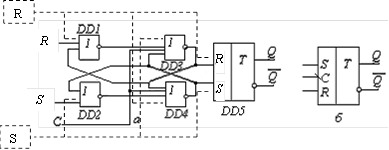

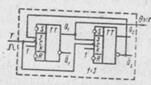

Двухступенчатые триггеры строятся несколькими способами: с разнополярным управлением ступенями (рис. 3.13, а), с инвертором (рис. 3.13, б)

|

Рис. 3.13. Схема двухступенчатого триггера: а) с разнополярным управлением; б) с инвертором

В первом варианте поочередное тактирование ступеней очевидно, поскольку ступени имеют разнополярные синхровходы. Во втором варианте ступени идентичны по синхровходам, а для их поочередного управления в цепь тактовых сигналов включен инвертор. В такой схеме возможны временные состязания сигналов: входной триггер состязается с инвертором. Если триггер переключится быстрее инвертора, то его новое состояние может успеть "проскочить" в выходной триггер, т. к. инвертор не успеет блокировать входы этого триггера. Несмотря на это, вариант с инвертором находит широкое применение (однородность элементной базы), при его проектировании просто заботятся об обеспечении нужного соотношения задержек инвертора и входного триггера.

Комбинированный триггер с асинхронными входами RS- установки на основе схем (рис. 3.13) может быть построен таким образом: дополнительные RS-входы включаются в элементы памяти обеих ступеней. Например, для триггера (рис. 3.10) дополнительный R–вход включается как третий вход элемента ИЛИ–НЕ DD3, а S–вход – элемента DD4, аналогично для триггера (рис. , 3.11) дополнительный  –вход включается как третий вход элемента И-НЕ DD3, а

–вход включается как третий вход элемента И-НЕ DD3, а  –вход – элемента DD4.

–вход – элемента DD4.

Разрешающее время по входу синхронизации и минимально допустимая длительность синхроимпульса двухступенчатого триггера составляют :

;

;

tрас=7t зд.р.ср. (3.5)

В качестве RS- триггера по схеме "с запрещающими связями" может быть использован JK- триггер (отличия в работе триггеров будут наблюдаться только в случае комбинации входных сигналов R=S=1, которая для RS- триггера является запрещенной). Пример схемы на элементах И—НЕ приведен на рис 3.19. В чистом виде (без обратных связей с выходов М-ступени на входы S- ступени ) RS- триггер по схеме «с запрещающими связями» не строится, поскольку в случае комбинации сигналов R=S=0, возможен прозрачный режим асинхронной записи.

3.2.2 D-триггер

К D-триггерам относятся последовательностные бистабильные устройства с одним информационным входом D и входом синхронизации С, которые в моменты действия разрешающего уровня или фронта синхросигнала устанавливаются в состояние, соответствующее логическому уровню сигнала на входе D, а после перехода синхросигнала в запрещающее состояние находятся в режиме хранения информации. Таким образом, триггеры типа D реализуют задержку сигнала с помощью тактирования, принимая сигнал только по разрешению тактового сигнала С.

Принципиально осуществимы и асинхронные D-триггеры, которые, однако, не представляют практического интереса.

|

Рис. 3.14. Cинхронные D-триггеры: а) функциональная схема на элементах ИЛИ—НЕ; б) ее условное графическое изображение; в) временные диаграммы работы; г) функциональная схема на элементах И—НЕ ; д) ее условное графическое изображение; в) временные диаграммы работы; ж) карта Карно D-триггера

Функционирование синхронного D-триггера в статических режимах описывается картой Карно (рис.3.13, ж) и характеристическим уравнением:

Q= CD v  Q’ (3.6)

Q’ (3.6)

Реализации синхронных D-триггеров, удовлетворяющих уравнению (3.6), показаны на рис. 3.14. Если на синхронизирующий вход D-триггера (рис. 3.14,а) подан уровень  =1 (или C = 0 для рис. 3.14,г), который является доминирующим для логических элементов DD1, DD2, то на их выходах устанавливаются уровни R* =S*=0 (

=1 (или C = 0 для рис. 3.14,г), который является доминирующим для логических элементов DD1, DD2, то на их выходах устанавливаются уровни R* =S*=0 ( *

* *=1). Эти уровни обеспечивают режим хранения для асинхронного триггера на элементах DD3, DD4, и не зависят от состояния информационного входа D. При

*=1). Эти уровни обеспечивают режим хранения для асинхронного триггера на элементах DD3, DD4, и не зависят от состояния информационного входа D. При  =0 (С = 1) информационный вход однозначно определяет состояние выхода элемента DD1 , который в свою очередь обусловливает инверсный уровень на выходе элемента DD2, и в триггер записывается информация, поданная на вход D. Поскольку сигналы на информационных входов триггеров должны быть установлены раньше (время предустановки ) подачи сигнала синхронизации, а также вследствие задержек переключения логических элементов DD1– DD4 (рис. 3.14, в, е), то сигнал на выходе Q повторяет сигнал D с задержкой относительно информационного входа . Это обусловило название D – триггера.

=0 (С = 1) информационный вход однозначно определяет состояние выхода элемента DD1 , который в свою очередь обусловливает инверсный уровень на выходе элемента DD2, и в триггер записывается информация, поданная на вход D. Поскольку сигналы на информационных входов триггеров должны быть установлены раньше (время предустановки ) подачи сигнала синхронизации, а также вследствие задержек переключения логических элементов DD1– DD4 (рис. 3.14, в, е), то сигнал на выходе Q повторяет сигнал D с задержкой относительно информационного входа . Это обусловило название D – триггера.

Для синхронизируемых уровнем D - триггеров переключение состояния происходит при переключении информационного входа D на всем интервале синхронизации С. Для того, чтобы триггер фиксировал значение сигнала на D – входе в определенный момент времени используется синхронизация фронтом синхроимпульсa.

D - триггер, синхронизируемый фронтом, показан на рис. 3.15 . Он построен по 6-элементной схеме (на трех элементарных триггерах), из них 2 триггера на элементах DD1– DD4 образуют схему синхронизации основной запоминающей ячейки на элементах DD5, DD6 . Из временных диаграмм работы D – триггера (рис. 3.15 в) видно, что при С = 0 на выходах  *,

*,  * поддерживаются единичные уровни независимо от состояния входа D. Это соответствует режиму хранения информации в основном триггере на элементах DD5, DD6. Переключение уровня на входе D влияет только на логические состояния выходов А и В триггеров схемы синхронизации. Если D = 0 , то В = 1, А = 0, а в случае D = 1 имеем В = 0, А = 1. При этом один из триггеров схемы синхронизации находится в устойчивом состоянии, а другой - в режиме разрыва триггерных связей при уровнях «логической 1» на обоих выходах. Например, если D = 0, то на выходах триггера, состоящего из элементов DD3, DD4, устанавливаются одинаковые уровни

* поддерживаются единичные уровни независимо от состояния входа D. Это соответствует режиму хранения информации в основном триггере на элементах DD5, DD6. Переключение уровня на входе D влияет только на логические состояния выходов А и В триггеров схемы синхронизации. Если D = 0 , то В = 1, А = 0, а в случае D = 1 имеем В = 0, А = 1. При этом один из триггеров схемы синхронизации находится в устойчивом состоянии, а другой - в режиме разрыва триггерных связей при уровнях «логической 1» на обоих выходах. Например, если D = 0, то на выходах триггера, состоящего из элементов DD3, DD4, устанавливаются одинаковые уровни  * = B = 1.

* = B = 1.

рис. 3.15. D -триггер с динамическим управлением ( 6-элементная схема): а) схема на элементах И—НЕ; б) условное графическое обозначение; в)временные диаграммы работы

По положительному фронту синхроимпульса С = 0 → 1 триггер, находившийся до этого в режиме разрыва триггерных связей, переходит в нормальное устойчивое состояние и на входах основного триггера формируются взаимно инверсные логические уровни. Если D = 0 ,то  *=0,

*=0,  *=1 и триггер устанавливается в состояние «0»; если D = 1 , то

*=1 и триггер устанавливается в состояние «0»; если D = 1 , то  *=1,

*=1,  *=0 и происходит установка в состояние «1».

*=0 и происходит установка в состояние «1».

Из диаграмм (рис.3.15,в) так же видно, что при С = 1 переключение состояния информационного входа D не влияет на состояние данного D-триггера. Это объясняется тем, что при установке основного триггера в состояние «0» сигналом  *=0 одновременно блокируется логический элемент DD4 и на его входе устанавливается В = 1 независимо от состояния входа D.При установке основного триггера в состояние «1» сигналом

*=0 одновременно блокируется логический элемент DD4 и на его входе устанавливается В = 1 независимо от состояния входа D.При установке основного триггера в состояние «1» сигналом  *=0 блокируются логические элементы DD1 и DD3 , по этому переключение состояний D и В не влияет на состояние основного триггера.

*=0 блокируются логические элементы DD1 и DD3 , по этому переключение состояний D и В не влияет на состояние основного триггера.

Комбинированный D-триггер асинхронной установкой. Организация асинхронной установки триггера в схеме на рис.3.15 показана штриховыми линиями. Состояние D-триггера, синхронизируемого фронтом, также как и синхронизируемого уровнем, описывается уравнением (3.6). Длительность процесса переключения и минимальная длительность синхроимпульса зависят от среднего времени задержки распространения сигнала через логические элементы:

tпер = tвх.min = 3tзд. р. ср , (3.7)

Триггер, аналогичный (рис.3.15), можно реализовать на элементах ИЛИ-НЕ.

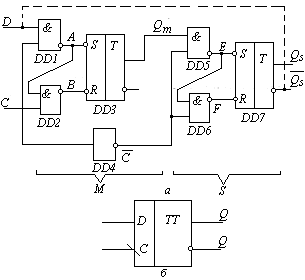

Еще один способ построения динамического D-триггера состоит в использовании двухступенчатых структур MS-типа. Двухтактный D-триггер строится на основе двух синхронизируемых противофазами уровнями D-триггеров (рис.3.16).

Рис.3.16. D -триггер с динамическим управлением ( двухступенчатая схема): а) схема на элементах И—НЕ; б) условное графическое обозначение; в)временные диаграммы работы

Благодаря синхронизации противофазными импульсами С и  запись новой информации в триггеры М и S ступеней принципиально разделена во времени, что исключает сквозную передачу информации со входа D на выходы Qs,

запись новой информации в триггеры М и S ступеней принципиально разделена во времени, что исключает сквозную передачу информации со входа D на выходы Qs, s.

s.

При С = 0 триггер вспомогательной ступени М находится в режиме хранения информации, а в выходной триггер уровнем  =1 разрешена перезапись содержимого триггера М. Переключение синхроимпульса С = 0→1 и

=1 разрешена перезапись содержимого триггера М. Переключение синхроимпульса С = 0→1 и  =1→0 (рис.3.16,в) изменяет режим работы триггеров М и S. Теперь триггер М переходит в режим записи информации со входа D, а триггер S – в режим хранения информации, записанной на предыдущем шаге. Во вспомогательном триггере М возможен режим асинхронной многократной записи в течении интервала времени действия синхроимпульса С = 1. При переключении синхроимпульса С = 1→0 информационный вход D блокируется и в основной триггер S предписывается последнее состояние QM.

=1→0 (рис.3.16,в) изменяет режим работы триггеров М и S. Теперь триггер М переходит в режим записи информации со входа D, а триггер S – в режим хранения информации, записанной на предыдущем шаге. Во вспомогательном триггере М возможен режим асинхронной многократной записи в течении интервала времени действия синхроимпульса С = 1. При переключении синхроимпульса С = 1→0 информационный вход D блокируется и в основной триггер S предписывается последнее состояние QM.

Разрешающее время по входу синхронизации (время необходимое для переключения двух ступеней) и минимально допустимая длительность синхроимпульса (время необходимое для переключения одной ступени) в двухступенчатом триггере составляют :

;

;

tрас=7t зд.р.ср. (3.8)

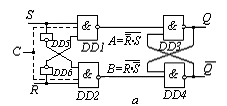

D – триггер может быть реализован и по схеме "с запрещающими связями" (рис. 3.19,а), если соединить ее входы по схеме, показанной на рис.3.19,б. При этом обратные связи с выходов Q и  на входы можно удалить, поскольку в отличии от RS-триггера в D – триггере на входы элементов DD1 и DD2 всегда будут подаваться взаимно инверсные значения сигналов и комбинация сигналов R=S=0, которая может вызвать прозрачный режим асинхронной записи, будет отсутствовать (равно как и запрещенная комбинация R=S=1).

на входы можно удалить, поскольку в отличии от RS-триггера в D – триггере на входы элементов DD1 и DD2 всегда будут подаваться взаимно инверсные значения сигналов и комбинация сигналов R=S=0, которая может вызвать прозрачный режим асинхронной записи, будет отсутствовать (равно как и запрещенная комбинация R=S=1).

3.2.3 T-триггер

T-триггеры — последовательностные бистабильные устройства с одним управляющим входом T, которые каждым входным сигналом переключаются в противоположное состояние.

Из карты Карно (рис.3.17,а) видно, что работа Т-триггера в статическом режиме описывается уравнением:

Из карты Карно (рис.3.17,а) видно, что работа Т-триггера в статическом режиме описывается уравнением:

Q=  Q’ + T

Q’ + T ’=T Å Q’ (3.9)

’=T Å Q’ (3.9)

Из уравнения 3.9. следует, что Т-триггер реализует операцию сложения по модулю 2. Поэтому Т-триггеры, режим их работы и управляющий вход называют счетными. Схемы , управляемые уровнем синхросигнала, обычно не реализуются, т.к. в этом случае при удержании разрешающего уровня сигнала на Т – входе триггер будет многократно переключаться в противоположное состояние, т.е. находиться с режиме генерации. На рис 3.17. показан принцип построения Т- триггера на основе RS- и D-триггеров. Для исключения режима генерации схемы этих триггеров должны иметь динамический синхровход.

а б в

Рис. 3.17. Т- триггер: а)карта Карно; б) схема построения на основе RS-триггера; в) схема построения на основе D-триггера

Схема построения Т-триггер двухступенчатого MS-типа на основе соответствующего D-триггера приведена на рис 3.16,а. Для этого необходимо (рис. 3.17,в) информационный вход D-триггера соединить с инверсным выходом  (на рис 3.16,а показано штриховой линией), а на вход синхронизации С подавать счетные импульсы Т. Аналогично можно построить схемы Т-триггеров на основе схем, изображенных на рис.3.13, если соединить их R и S входы с выходами Q и

(на рис 3.16,а показано штриховой линией), а на вход синхронизации С подавать счетные импульсы Т. Аналогично можно построить схемы Т-триггеров на основе схем, изображенных на рис.3.13, если соединить их R и S входы с выходами Q и  в соответствии с рис.3.17,б.

в соответствии с рис.3.17,б.

Схема «6-ти-элементного» типа строится по принципу, показанному на рис.3.17 на основе схем рис.3.12, а (RS-триггер) или рис.3.15, а (D-триггер).

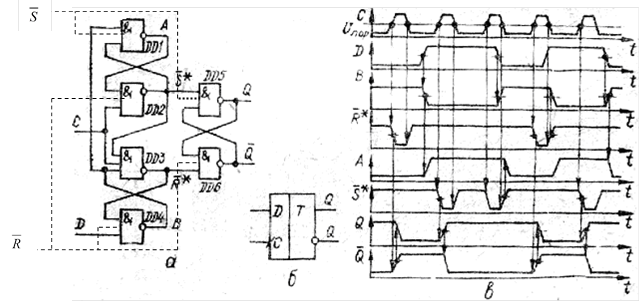

T-триггер может быть построен по схеме «c запрещающими связями» (рис. 3.18,а) . Эта схема не имеет инвертора в цепи подачи синхросигналов на вторую ступень, как. МS-схемы, аналогичные рис.3.13,б или 3.16,а. Сигналы блокировки второй ступени берутся в этом случае со входов фиксатора первой ступени. Переключения триггеров ступеней M и S разделены во времени самим счетным импульсом T. Триггер ступени M переключается единичным, а триггер ступени S - нулевым уровнем сигнала T. Т.е. состояние МS-триггера изменяется по каждому заднему фронту сигнала Т. Реализация разделенного во времени режима работы триггеров ступеней M и S достигается использованием связей выходов элементов DD1 (А) и DD2 (В) со входами DD4, DD5 вместо инвертора Т (С) сигнала DD4 в схеме на рис. 3.16,а . В этом случае запись информации в триггер ступени M одновременно блокирует запись в триггер ступени S. Поскольку в этом случае на входы элементов DD1 и DD2 всегда подаются взаимоинверсные значения сигналов с выходов триггера ступени M , а Т=1, то на одном из выходов А или В обязательно устанавливается логический «0» , который блокирует другие входы элементов DD4, DD5 , устанавливая на их выходах E и F значения логической «1», что соответствует режиму хранения для триггера ступени S. Наоборот, если Т=0 , то на выходах элементов DD1 и DD2 устанавливаются значения А = В = 1. В этом случае триггер ступени M переключается в режим хранения информации, а вентили DD4, DD5 разблокируются для перезаписи информации с выходов триггера ступени M (DD3) в триггер ступени S (DD6).

Рис. 3.18 . Т-триггер:с динамическим управлением (схема с «запрещающими связями» а) функциональная схема на элементах И—НЕ; б) условное графическое изображение; в) временные диаграммы работы.

Разрешающее время по входу синхронизации (минимальное время необходимое для переключения двух ступеней) и минимально допустимая длительность синхроимпульса (минимальное время необходимое для переключения одной ступени) в триггере с «запрещающими связями» соответствуют выражениям 3.10 : Разрешающее время здесь меньше , чем в выражении 3.8, для двухступенчатой схемы .на одну задержку инвертора в цепи синхронизации.

;

;

tрас=6t зд.р.ср. (3.10)

Важно отметить, что поскольку Т- триггер имеет обратные связи со своих выходов на входы, и либо находится в режиме хранения, либо меняет состояние на противоположное предыдущему, то для задания триггеру начального состояния , он обычно снабжается дополнительными входами RS-входами.

Комбинированный Т- триггер с асинхронными входами RS- установки на основе схем (рис. 3.18) может быть построен таким образом: дополнительные RS-входы включаются в элементы памяти обеих ступеней. Например, для схемы на рис. 3.16,а дополнительный  вход включается в элемент И-НЕ DD3 вместе с сигналом B, а для триггера DD7 в элемент И-НЕ вместе с сигналом F , а

вход включается в элемент И-НЕ DD3 вместе с сигналом B, а для триггера DD7 в элемент И-НЕ вместе с сигналом F , а  -вход аналогично включается в DD3 и DD7 вместе с сигналами A и E. Для схемы на рис. 3.18, а дополнительные

-вход аналогично включается в DD3 и DD7 вместе с сигналами A и E. Для схемы на рис. 3.18, а дополнительные  и

и  входы включаются в элементы DD3 и DD6.

входы включаются в элементы DD3 и DD6.

Как видно из временных диаграмм (рис 3.18, б), частота импульсов на выходе T-триггера fвых = fвх/2, т. е. их можно использовать в качестве делителей частоты. При этом максимальная частота счетных импульсов при минимально допустимой их длительности составляют:

fTmax = 1/(6 t зд.р.ср );.

tT>= 3 t зд.р.ср (3.11)

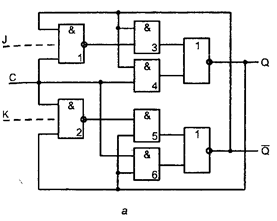

3.2.4 Универсальный JK-триггер

JK-триггеры - это последовательностные бистабильные устройства с двумя информационными входами J и K, которые в случае входной комбинации J = K= 1 переключают триггер в противоположное состояние подобно T-триггеру, а при любых других комбинациях функционируют как RS-триггер, у которого роль входов S u R выполняют соответственно входы J и К: JºS, KºR. По тем же причинам, что и Т- триггер JK-триггер обычно строится по двухступенчатой схеме, и часто имеет входы начальной S R – установки. JK – тригера называется универсальным потому, что на его основе можно построить триггеры других типов (рис. 3.19, б).

|

Рис.3.19.JK-триггер:с динамическим управлением (схема с «запрещающими связями» а) функциональная схема на элементах И—НЕ; б) условное графическое изображение и способы построения на его основе триггеров других типов; в) временные диаграммы работы; г) карта Карно

На основании карты Карно (рис.3.19,г) работу JK-триггера в статическом режиме можно описать уравнением 3.12:

Q= ’J + Q’

’J + Q’ (3.12)

(3.12)

Функционирование JK-триггера «с запрещающими связями» (рис. 3.19,а) полностью аналогично работе Т-триггера (рис.3.18) при условии J=K=1, а вход С играет роль входа Т. Т.е. триггер переключается в противоположное состояние по заднему фронту сигнала С, что обусловлено обратными связями с выходов Q и  на входы триггера. В случае, когда J ¹ K возможны две ситуации. Первая ситуация: одинаковые сигналы на входах каждого из элементов DD1( J=

на входы триггера. В случае, когда J ¹ K возможны две ситуации. Первая ситуация: одинаковые сигналы на входах каждого из элементов DD1( J=  ) , DD2( K= Q), тогда входы J и K не оказывают влияния на работу триггера (равносильно J=K=1) и он будет переключаться в противоположное состояние. Вторая ситуация: J¹

) , DD2( K= Q), тогда входы J и K не оказывают влияния на работу триггера (равносильно J=K=1) и он будет переключаться в противоположное состояние. Вторая ситуация: J¹  , K¹ Q, что будет означать попытку переключить триггер в то состояние, в котором он уже находится. В этом случае сигналы А и В примут значение логической «1», т.к. один из входных сигналов элемента DD1 (J или

, K¹ Q, что будет означать попытку переключить триггер в то состояние, в котором он уже находится. В этом случае сигналы А и В примут значение логической «1», т.к. один из входных сигналов элемента DD1 (J или ) и элемента DD2 (K или Q) будет равен «0». На выходах этих элементов установится А =В=1, что означает режим хранения для фиксатора DD3, DD4, а элементы DD5 и DD6 хоть и открываются для записи состояния нижней ступени (QM) в верхнюю ступень (Qs), но эти состояния и так уже совпадают. Поэтому JK – тригер оснанется в прежднем состоянии, что и требовалось. В случае, когда J=K=0 (режим хранения), имеем А =В=1, и состояние триггера не меняется.

) и элемента DD2 (K или Q) будет равен «0». На выходах этих элементов установится А =В=1, что означает режим хранения для фиксатора DD3, DD4, а элементы DD5 и DD6 хоть и открываются для записи состояния нижней ступени (QM) в верхнюю ступень (Qs), но эти состояния и так уже совпадают. Поэтому JK – тригер оснанется в прежднем состоянии, что и требовалось. В случае, когда J=K=0 (режим хранения), имеем А =В=1, и состояние триггера не меняется.

Следует однако отметить, что для правильной работы схемы в этом режиме смену входных сигналов J и K можно производить только при С=0., иначе, если комбинация J=K=0 будет следовать за J=K=1, то вместо режима хранения будем иметь переключение в противоположное состояние. Эта проблема отмечалась ранее для RS-триггера, там она возникает и при других комбинациях входных сигналов перед R=S=0.Это происходит потому, что при J=K=0 триггер верхней ступени открывается для записи данных из нижней ступени, а в нее при С=1 успевают записаться новые данные , т.е. QM ¹ Qs.

Разрешающее время и минимально допустимая длительность синхроимпульса триггера (рис. 3.19) соответствуют выражениям 3.10, а частотные свойства - выражениям 3.10.

JK – триггер по двухступенчатой и 6- элементной схеме ( с динамическим управлением) может быть построен, на основе схем соответствующих SR-триггеров (рис.3.12 и 3.13) с добавлением обратных связей по схеме на рис. 3.20.

|

Рис.3.21. Схема построения JK- триггера на основе SR- триггера.

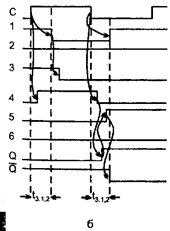

В последнее время получили распространение и одноступенчатые JK – триггеры с внутренней задержкой (рис. 3.21, а). Функционирование одноступенчатого триггера можно рассмотреть с помощью временных диаграмм (рис. 3.21, б). На диаграммах показана работа триггера в счетном режиме. Так, как в счетном режиме J = К = 1, и соответствующие входы не влияют на работу элементов И1 и И2, они показаны штриховыми линиями. На диаграмме показан процесс переключения триггера из «0» в «1». Поскольку схема симметрична, обратное переключение будет происходить аналогично.

Работоспособность триггера обеспечивается только при условии t з1,2> t з3,4,5,6 + t3или-не (задержки элементов 1 и 2 превышают суммарную задержку последующих элементов И + ИЛИ-НЕ), что отражено на временных диаграммах. Как видно из диаграмм, триггер переключается по заднему фронту синхросигнала.

Ячейка памяти триггера строится на 2-х элементах ИЛИ-НЕ, которые в совокупности с элементами И3-И6 образуют асинхронный

– триггер. Один инвертор –ИЛИ-НЕ +(И3 или И4) реализует функцию Q =not(И1

– триггер. Один инвертор –ИЛИ-НЕ +(И3 или И4) реализует функцию Q =not(И1 ’vС

’vС ’), второй инвертор –ИЛИ-НЕ +(И5 или И6) реализует функцию

’), второй инвертор –ИЛИ-НЕ +(И5 или И6) реализует функцию  =not(И2Q’vСQ’). При С=0 на выходах И4 и И6 обеспечивается логический «0» и они не оказывают влияния на ячейку памяти, а на выходах И1 и И2 устанавливаются логические «1», что обеспечивает режим хранения для

=not(И2Q’vСQ’). При С=0 на выходах И4 и И6 обеспечивается логический «0» и они не оказывают влияния на ячейку памяти, а на выходах И1 и И2 устанавливаются логические «1», что обеспечивает режим хранения для

– триггера на элементах ИЛИ-НЕ +И3, ИЛИ-НЕ +И5. При С=1 на выходах элементов И1 и И2 появляется входная информация, которая перепишется в И3 или И5, но благодаря С=1 имеем Q=not(И1

– триггера на элементах ИЛИ-НЕ +И3, ИЛИ-НЕ +И5. При С=1 на выходах элементов И1 и И2 появляется входная информация, которая перепишется в И3 или И5, но благодаря С=1 имеем Q=not(И1 ’v

’v ’)=Q’,

’)=Q’,  =not(И2Q’vQ’)=

=not(И2Q’vQ’)= ’. Таким образом, для

’. Таким образом, для

– триггера на элементах ИЛИ-НЕ +И4, ИЛИ-НЕ +И6 обеспечивается режим хранения. При последующем переключении входа С в «0» элементы И4 и И6 снова перестают влиять на ячейку памяти, и теперь Q может переключиться от И3 – Q=not(И1

– триггера на элементах ИЛИ-НЕ +И4, ИЛИ-НЕ +И6 обеспечивается режим хранения. При последующем переключении входа С в «0» элементы И4 и И6 снова перестают влиять на ячейку памяти, и теперь Q может переключиться от И3 – Q=not(И1 ’) и затем переключить И5 и

’) и затем переключить И5 и  =not(И2Q). Аналогично

=not(И2Q). Аналогично  может переключиться от И5 и затем переключить И3 и Q. И только после того, как триггер успеет переключиться в новое состояние, элементы И1 и И2 (они имеют большую задержку) переведут его в режим хранения.

может переключиться от И5 и затем переключить И3 и Q. И только после того, как триггер успеет переключиться в новое состояние, элементы И1 и И2 (они имеют большую задержку) переведут его в режим хранения.

Рис.3.21. JK- триггер: а)схема с внутренними задержками; б) временная диаграмма работы схемы

3.3. Регистры. Классификация

Регистры — самые распространенные узлы цифровых устройств. Они оперируют с многоразрядными переменными, которые также называют словами. Над словами выполняется ряд операций: прием, выдача, хранение, сдвиг в разрядной сетке, поразрядные логические операции.

Регистры строятся из разрядных схем, которые состоят из триггеров и, чаще всего, дополнительных логических элементов.

Главным классификационным признаком регистров является способ приема и выдачи данных. По этому признаку различают параллельные (статические) регистры, последовательные (сдвигающие) и параллельно-последовательные.

В параллельных регистрах прием и выдача слов производятся по всем разрядам одновременно. В них хранятся слова, которые могут быть подвергнуты поразрядным логическим преобразованиям.

В последовательных регистрах слова принимаются и выдаются разряд за разрядом. Их называют сдвигающими, т. к. тактирующие сигналы при вводе и выводе слов перемещают их на один разряд в разрядной сетке. Сдвигающий регистр может осуществлять сдвиг, записанного слова влево, вправо или быть реверсивным (с возможностью сдвига в обоих направлениях).

Последовательно-параллельные регистры имеют входы-выходы одновременно последовательного и параллельного типа. Имеются варианты с последовательным входом и параллельным выходом (SIPO, Serial Input — Parallel Output), параллельным входом и последовательным выходом (PISO), а также варианты с возможностью любого сочетания способов приема и выдачи слов.

3.3.1.Параллельные регистры

В параллельных (статических) регистрах схемы разрядов не обмениваются данными между собой. Общими для всех разрядов обычно являются цепи синхронизации, сброса/установки, разрешения выхода или приема, т. е. цепи управления. Пример схемы статического регистра, построенного на триггерах типа D с прямым динамическим управлением С, инверсным входом сброса R и выходами с третьим состоянием, которые управляются сигналом EZ, показан на рис. 3.22.

|

Рис. 3.22. Пример параллельного регистра а) схема регистра с трехстабильным выходом; б) условное графическое обозначение; в) таблица истинности

Таблица истинности регистра приведена на рис. 3.22,в. Символы « и ¯» означают соответственно задний и передний фронт сигнала, символ «Z» –высокоимпедансное (отключенное) состояние, а «–» –любое значение сигнала.

Для современной схемотехники характерно построение регистров именно на D-триггерах, преимущественно с динамическим управлением. Многие имеют выходы с третьим состоянием, некоторые регистры относятся к числу буферных, т. е. рассчитаны на работу с большими емкостными и/или низкоомными активными нагрузками. Это обеспечивает их работу непосредственно на магистраль (без дополнительных схем интерфейса).

3.3.2.СДВИГАЮЩИЕ РЕГИСТРЫ

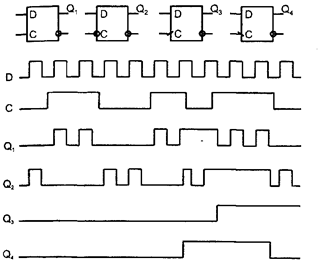

Последовательные (сдвигающие) регистры представляют собою цепочку разрядных схем, связанных цепями переноса.

В регистрах со сдвигом на один разряд вправо (рис. 3.23, а) слово сдвигается при поступлении переднего фронта синхросигнала С. Вход (DSR — Data Serial Right) и выход регистра последовательные. На временной диаграмме работы регистра все триггеры в начальный момент времени устанавливаются в «0» сигналом R=1, затем сигнал R переключается в «0» и не оказывает влияния на дальнейшую работу схемы. Теперь с каждым передним фронтом синхросигнала С сигнал со входа DSR будет записываться в триггер первого разряда (Q1=DSR), старый сигнал с выхода первого разряда Q1 — во второй разряд (Q2= Q1) , старый сигнал с выхода второго разряда — в третий разряд (Q3= Q2), а с выхода третьего — в выходной разряд (Вых = Q3). Таким образом, по истечении 4-х тактов синхросигнала С выходной сигнал регистра станет равен входному (Вых=DSR). Поскольку в нашем примере сигнал на входе DSR все время оставалось постоянным («1»), то на диаграмме работы регистра можно наблюдать поразрядное вытеснение начальных нулевых значений сигналов единичными входными. На рис. 3.23, б показана схема регистра со сдвигом влево (вход данных DSL — Data Serial Left). На временной диаграмме триггеры всех разрядов устанавливаются в начальное состояние «1» сигналом S=1, а затем входной сигнал DSL последовательно в течение 4-х тактов синхросигнала С сдвигается от выхода четвертого разряда Q4 к выходу регистра.

На рис. 3.23, в показан принцип построения реверсивного регистра, в котором имеются связи триггеров с обоими соседними разрядами, но управляющим сигналом Р разрешается работа только одних из этих связей (команды "влево" и "вправо" одновременно поданы быть не могут). На входе каждого триггера реализуется функция 3.13:

Di=PQ i+1 +  Q i -1 (3.13)

Q i -1 (3.13)

Таким образом, при Р=1 — D=Q i+1, что соответствует сдвигу влево, а при Р=0 — D=Q i -1, что соответствует сдвигу вправо.

Из рассмотренных принципов работы сдвиговых регистров видно, что применение в разрядных схемах одноступенчатых триггеров, управляемые уровнем синхросигнала, может привести к тому, что некоторые триггеры за время действия разрешающего уровня переключатся неоднократно, что недопустимо. Поэтому обычно используются триггеры с динамическим управлением.

|

Рис.3. 23. Последовательные регистры: а) регистр со сдвигом вправо и временные диаграммы его работы; б) регистр со сдвигом влево; в) реверсивный регистр

3.3.3. Универсальные регистры

В сериях ИС и библиотеках БИС/СБИС программируемой логики имеется много вариантов регистров. Среди них часто встречаются многофункциональные или универсальные регистры, способные выполнять набор микроопераций. Многофункциональность достигается композицией в одной и той же схеме частей, необходимых для выполнения различных операций. Управляющие сигналы, задающие вид выполняемой в данное время операции, активизируют необходимые для этого части схемы.

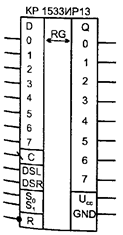

Типичным представителем универсальных регистров является схема ИР13. Это восьмиразрядный реверсивный регистр, который имеет также параллельные входы и выходы, вход асинхронного сброса R и входы выбора режима S0 и S1, задающие четыре режима (параллельная загрузка, два сдвига и хранение). Таблица истинности регистра определяется табл. 3.3. Условное обозначение регистра ИР13 приведено на рис. 3.24.

Таблица 3.3. Таблица истинности регистра ИР13

| Режим | Входы | Выходы | |||||||||||

|

| C |

| SO | S1 | DSR | DSL | Dn | Q0 | Q1 | . . . . | Q6 | Q7 | |

| Сброс | X | 0 | X | X | X | X | X | 0 | 0 | . . . . | 0 | 0 | |

| Хранение | | 1 | 0 | 0 | X | X | X | Q0 | Q1 | . . . . | Q6 | Q7 | |

| Сдвиг влево | | 1 | 1 | 0 | X | 0/1 | X | Q1 | Q2 | . . . . | Q6 | DSR | |

| Сдвиг вправо | | 1 | 0 | 1 | 0/1 | X | X | DSR | Q0 | . . . . | Q5 | Q6 | |

| Параллельная загрузка | | 1 | 1 | 1 | X | X | Dn | D0 | D1 | . . . . | D6 | D7 | |

Рис. 3.24. Условное обозначение универсального регистра

Регистры, имеющие параллельный (последовательный) вход и последовательный (параллельный) выход, служат основными блоками преобразователей параллельных кодов в последовательные и обратно.

3.4. Счетчики

Понятие "счетчик" является очень широким. К счетчикам относят автоматы, которые под действием входных импульсов переходят из одного состояния в другое, фиксируя тем самым число поступивших на их вход импульсов в том или ином коде.

Специфичной для счетчиков операцией является изменение их содержимого на единицу (может быть и условную). Прибавление такой единицы соответствует операции инкрементации, вычитание — операции декрементации. Обычно счетчиками выполняются также и другие операции — сброс, установка, параллельная загрузка и др.

Счетчик характеризуется модулем счета М (емкостью). Модуль определяет число возможных состояний счетчика. После поступления на счетчик М входных сигналов начинается новый цикл, повторяющий предыдущий.

Классификация счетчиков

По способу кодирования внутренних состояний различают двоичные счетчики, счетчики Джонсона, счетчики с кодом "1 из N" и др.

По направлению счета счетчики делятся на суммирующие (прямого счета), вычитающие (обратного счета) и реверсивные (с изменением направления счета).

По принадлежности к тому или иному классу автоматов говорят о синхронных или асинхронных счетчиках (более подробную классификацию по этому признаку не затрагиваем, учитывая реальный состав микросхем счетчиков).

Счетчики строятся из разрядных схем, имеющих межразрядные связи. Соответственно организации этих связей различают счетчики с последовательным, параллельным и комбинированными переносами.

Возможные режимы работы счетчика:

регистрация числа поступивших на счетчик сигналов;

деление частоты.

В первом режиме результат — содержимое счетчика, во втором режиме выходными сигналами являются импульсы переполнения счетчика.

Быстродействие счетчика характеризуется временем установления в нем нового состояния (первый режим), а также максимальной частотой входных сигналов

Как и любой автомат, счетчик можно строить на триггерах любого типа, однако удобнее всего использовать для этого триггеры типа Т (счетные) и JK, имеющие при J = К = 1 счетный режим.

Состояние счетчика читается по выходам разрядных схем как слово .. Q0, входные сигналы поступают на младший разряд счетчика.

.. Q0, входные сигналы поступают на младший разряд счетчика.

Двоичным счетчиком назовем счетчик, имеющий модуль М = 2n, где n — целое число, и естественную последовательность кодов состояний (его состояния отображаются последовательностью двоичных чисел, десятичными эквивалентами которых будут числа 0, 1, 2, 3,..., M—l).

Двоичные счетчики

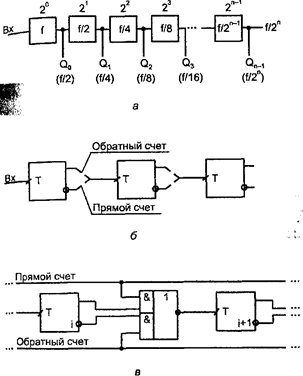

Схему двоичного счетчика можно получить с помощью формального синтеза, однако более наглядным путем представляется эвристический. Таблица истинности двоичного счетчика — последовательность двоичных чисел от нуля до М-1. Наблюдение за разрядами чисел, составляющих таблицу, приводит к пониманию структурной схемы двоичного счетчика. Состояния младшего разряда при его просмотре по соответствующему столбцу таблицы показывают чередование нулей и единиц вида 01010101..., что естественно, т. к. младший разряд принимает входной сигнал и переключается от каждого входного воздействия. В следующем разряде наблюдается последовательность пар нулей и единиц вида 001100 II... . В третьем разряде образуется последовательность из четверок нулей и единиц 00001 111... и т.д. Из этого наблюдения видно, что следующий по старшинству разряд переключается с частотой, в два раза меньшей, чем данный.

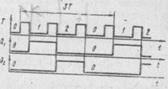

Известно, что счетный триггер делит частоту входных импульсов да два. Сопоставив этот факт с указанной выше закономерностью, видим, что счетчик может быть построен в виде цепочки последовательно включенных счетных триггеров (рис. 3.43, а). Заметим, кстати, что согласно ГОСТу входы элементов изображаются слева, а выходы справа. Соблюдение этого правила ведет к тому, что в числе, содержащемся в счетчике, младшие разряды расположены левее старших.

Представление счетчика цепочкой Т-триггеров справедливо как для суммирующего, так и для вычитающего вариантов, поскольку закономерность по соотношению частот переключения разрядов сохраняется как при просмотре таблицы сверху вниз (прямой счет), так и снизу вверх (обратный счет). Различия при этом состоят в направлении переключения предыдущего разряда, вызывающего переключение следующего. При прямом счете следующий разряд переключается при переходе предыдущего в направлении 1-0, а при обратном — при переключении 0-1. Следовательно, различие между вариантами заключается в разном подключении входов триггеров к выходам предыдущих. Если схема строится на счетных триггерах с прямым динамическим управлением, то характер подключения следующих триггеров к предыдущим для получения счетчиков прямого и обратного счета будет соответствовать рис. 3.43, б.

Из различия вариантов прямого и обратного счета следует также и способ построения реверсивного счетчика (рис. 3.43, в) путем переноса точки съема сигнала с триггера на противоположный выход под действием управляющего сигнала и с помощью элемента И-ИЛИ-НЕ, как показано на рисунке, либо элемента И-ИЛИ.

Рис. 3.43. Структура последовательного счетчика (а), ее реализация на триггерах с прямым динамическим управлением (б) и межразрядные связи реверсивного счетчика (в)

Полученные структуры относятся к асинхронным счетчикам, т. к. в них каждый триггер переключается выходным сигналом предыдущего, и эти переключения происходят не одновременно. Переключение одного триггера за другим есть не что иное, как распространение переноса по разрядам числа при изменении содержимого счетчика. В худшем случае перенос распространяется по всей разрядной сетке от младшего разряда к старшему, т. е. для установления нового состояния должны переключиться последовательно все триггеры. Отсюда видно, что время установления кода в асинхронном счетчике составит величину tycт < ntтг. Другим названием асинхронного счетчика является название "последовательный счетчик".

"Максимальная частота входных импульсов в режиме деления частоты ограничивается возможностями триггера младшего разряда, т. к. все последующие разряды переключаются с более низкими частотами.

Особенностью последовательных счетчиков является возникновение в переходных процессах ложных состояний из-за задержек переключения триггеров.

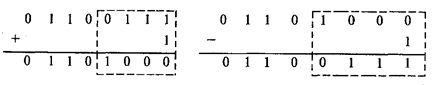

На рис. 3.44 показана временная диаграмма работы двухразрядного суммирующего счетчика на триггерах с прямым динамическим управлением, построенная с учетом задержек переключения триггеров tтг. Читая состояние счетчика Q по потенциалам на выходах триггеров Q0 и Q1, видим, что после состояний 1 и 3 появляются ложные состояния 0 и 2 (показаны штриховкой). Опасность воздействия коротких ложных импульсов на ЦУ заставляет прибегать при необходимости к стробированию выхода счетчика.

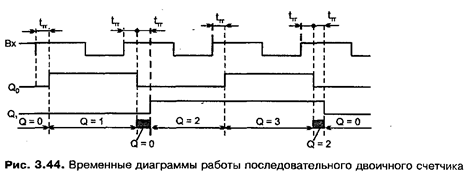

Максимальным быстродействием обладают синхронные счетчики с параллельным переносом, структуру которых найдем эвристически, рассмотрев процессы прибавления единицы к двоичным числам и вычитания ее из них, например:

Результат всегда отличается от исходного числа только в нескольких младших разрядах, значения которых инвертируются. Для суммирующего счетчика требуется инверсия разрядов до первого разряда, равного логическому нулю, включая и его, а для вычитающего аналогично до разряда, равного логической единице. Таким образом, в суммирующем счетчике должны переключиться разряды, для которых все младшие единичны, для вычитающего — те, для которых все младшие находятся в нуле.

Эти задачи и должны решать счетчики. Время установления таких счетчиков не зависит от разрядности n и равно где

где  — задержка коньюнктора. Структура суммирующего синхронного счетчика с параллельным переносом, реализованного на триггерах с управлением фронтом, показана на рис. 3.45, а. Схема межразрядной связи для реверсивного счетчика с сигналом U/D (Up/Down, т. е. прямо/обратно) показана рис. 3.45, б.

— задержка коньюнктора. Структура суммирующего синхронного счетчика с параллельным переносом, реализованного на триггерах с управлением фронтом, показана на рис. 3.45, а. Схема межразрядной связи для реверсивного счетчика с сигналом U/D (Up/Down, т. е. прямо/обратно) показана рис. 3.45, б.

С ростом числа разрядов реализация параллельных счетчиков затрудняется — требуются вентили с большим числом входов, растет нагрузка на выходы триггеров.

Счетчики с групповой структурой

В связи с ограничениями на построение параллельных счетчиков большой Разрядности широкое распространение получили счетчики с групповой структурой, в которых счетчик разбивается на группы, связанные цепями межгруппового переноса (рис. 3.46, а). При единичном состоянии всех триггеров группы приход очередного входного сигнала создаст перенос из атой группы. Эта ситуация подготавливает межгрупповая схема И к прямому пропусканию входного сигнала на следующую группу. В наихудшем для быстродействия случае, когда перенос проходит через все группы и поступает на вход последней,

где l — число групп; trp — время установления кода в группе.

Если уменьшить разрядность группы до единицы и использовать синхронные Т-триггеры, то получится схема синхронного счетчика с последовательным переносом (рис. 3.46, б). Схема относится к числу синхронных, т. к. все триггеры срабатывают одновременно под действием единого входного сигнала. В этом проявляется быстрая реакция схемы на входной сигнал, такая же, как и в счетчике с параллельным переносом. Однако по максимальной частоте входных сигналов эта схема существенно отличается от схемы с параллельным переносом, т. к. до подачи нового входного сигнала требуется дать цепочке вентилей установиться в новое состояние путем их последовательного переключения.

В развитых сериях ИС обычно имеется по 5...10 вариантов двоичных счетчиков, выполненных в виде 4-х разрядных групп (секций). Каскадирование секций может выполняться путем их последовательного включения по цепям переноса, организации параллельно-последовательных переносов или для более сложных счетчиков с двумя дополнительными управляющими входами разрешения счета и разрешения переноса путем организации параллельных переносов и в группах и между ними.

Особенностью двоичных счетчиков синхронного типа является наличие ситуаций с одновременным переключением всех его разрядов (например, для суммирующего счетчика при переходе от кодовой комбинации 11…1 к комбинации 00...0 при переполнении счетчика и выработке сигнала переноса). Одновременное переключение многих триггеров создает значительный токовый импульс в цепях питания ЦУ и может привести к сбою в их работе. Поэтому в руководящих материалах по использованию некоторых БИС/ СБИС программируемой логики, в частности, имеется ограничение на разность двоичных счетчиков заданной величиной k (например, 16). При необходимости применения счетчика большей разрядности рекомендуется переходить к коду Грея, для которого переходы от одной кодовой комбинации к другой сопровождаются переключением всего одного разряда. Правда, для получения результата счета в двоичном коде придется использовать дополнительно преобразователь кода, но это является платой за избавление от токовых импульсов большой интенсивности в цепях питания.

Пример условного обозначения счетчика приведен на рис. 3.47.

3.4.1. Двоично-кодированные счетчики с произвольным модулем

Часто при проектировании цифровых устройств возникает необходимость в делителях частоты, для которых М —любое целое число. Счетчики с модулем, не равным целой степени числа 2, т. е. с произвольным модулем, реализуются на основе нескольких методов.

Для построения счетчика с произвольным модулем М берется двоичный счетчик с модулем 2n, превышающим заданный и ближайшим к нему: 2n-1 ≤ М ≤2n .Например, для построения счетчика с М= 5 нужно взять двоичный счетчик с М=23.Такой двоичный счетчик имеет 2n — М = L лишних (неиспользуемых) состояний, подлежащих исключению. Способы исключения лишних состояний многочисленны, и для любого М можно предложить множество реализации счетчика.

Остановимся на двух способах построения счетчиков с произвольным модулем: модификации межразрядных связей и управлении сбросом. При построении счетчика с модифицированными межразрядными связями последние, лишние, состояния исключаются непосредственно из таблицы функционирования счетчика. При этом после построения схемы обычным для синтеза автоматов способом получается счетчик, специфика которого состоит в нестандартных связях, между триггерами, что и объясняет название способа. Схема получается специализированная, изменение модуля счета требует изменения самой схемы, т. е. легкость перестройки с одного модуля на другой отсутствует. В то же время реализация схемы счетчика может оказаться простой, а ее быстродействие высоким.

При управлении сбросом выявляется момент достижения содержимым счетчика значения М—1. Это является сигналом сброса счетчика в следующем такте, после чего начинается новый цикл. Этот вариант обеспечивает легкость перестройки счетчика на другие значения модуля, т. к. требуется изменять лишь код, с которым сравнивается содержимое счетчика для выявления момента сброса.

Построение счетчика первым способом

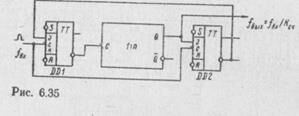

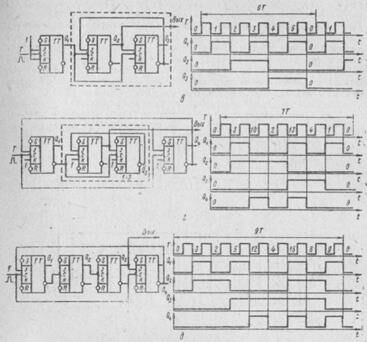

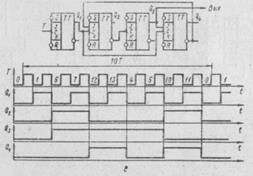

На рис. 6.35. показан общий принцип построения счетчиков с нечетным М. Данная схема была предварительно получена стандартными методами синтеза автоматов.

Если между входным и выходным триггерами включен делитель частоты на любое натуральное число п, то такая схема обеспечивает деление частоты на М = 2п+1.

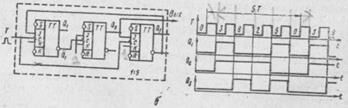

Схемы построения счетчиков с различными М показаны на рис. 6.34. Например, счетчик делитель частоты на 3 (рис. 6.34,а) реализован при n= 1, что соответствует прямой связи между входным DDI н выходным DD2 триггерами. Для M= 5 необходимо n = 2, поэтому между входным и выходным триггерами должен быть включен один дополнительный триггер-делитель частоты на 2 (рис. 6.34,6). Делитель частоты с М = 6 = 2 * 3 (рис. 6.34,в) получен последовательным соединением делителей частоты на 2 и на 3 (рис. 6.34,в). Для реализации М= 7 (рис. 6.34,г) и М= 9 (рис. 6.34,д) использована структура (рис. 6.35) соответственно при n = 3, полученном с помощью схемы (рис. 6.34,а), и при n = 4. Делитель частоты на 10 = 2 * 5 представлен (рис. 6.34,е) последовательным соединением делителя частоты на 5 и дополнительного триггера.

Приведенные на рис. 6.34 схемы последовательных счетчиков предназначены в основном для использования в режиме деления частоты без дешифрации их состояний, смена которых при использовании структуры на рис. 6.35 не соответствует естественному счету. Их достоинство — максимальное быстродействие, ограниченное предельной частотой переключения входного триггера, при минимальных затратах оборудования.

Рис. 6.34

Построение счетчика вторым способом

Второй метод построения счетчиков с произвольным модулем — метод управляемого сброса — позволяет изменять модуль счета очень простым способом, не требующим изменений самой схемы счетчика.

При построении счетчиков с регулярной сменой состояний согласно двоично-десятичному счету необходимо определить требуемое количество триггеров n согласно соотношению 2n-1 ≤ М ≤2n .

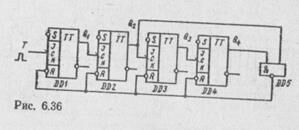

Кроме последовательно включенных N триггеров такой счетчик должен содержать логическую схему, декодирующую состояние М и при достижении содержимым счетчика этого значения формирующую сигнал сброса всех разрядов в состояние «0» при. Пример десятичного счетчика (М=10) с регулярной сменой состояний показан на рис. 6.36. Каждый десятый входной импульс переводит счетчик в состояние 1010 (10 десятичное), на двух входах вентиля DD5 устанавливаются уровни «1» и- его выходной сигнал сбрасывает все триггеры в состояние «0».

______

R =( Q2Q4) = 0; __ __

В общем случае выражение в скобках должно было бы быть Q4Q3Q2Q1, но поскольку кодовые комбинации, при которых одновременно Q2=Q4=1 и Q3=1 или Q2=1 не достигаются, то применяется упрощение.

3.5. Полупроводниковые запоминающие устройства

3.5.1 Основные сведения

Запоминающие устройства (ЗУ) служат для хранения информации и обмена ею с другими ЦУ. Микросхемы памяти в общем объеме выпуска ИС занимают около 40% и играют важнейшую роль во многих системах различного назначения. Микросхемы и системы памяти постоянно совершенствуются как в области схемо технологии, так и в области развития новых архитектур. В настоящее время созданы и используются десятки различных типов ЗУ.

Важнейшие параметры ЗУ находятся в противоречии. Так, например, большая информационная емкость не сочетается с высоким быстродействием, а быстродействие в свою очередь не сочетается с низкой стоимостью. Поэтому системам памяти свойственна многоступенчатая иерархическая структура, и в зависимости от роли того или иного ЗУ его реализация может быть существенно различной. В наиболее развитой иерархии памяти ЭВМ можно выделить следующие уровни:

- регистровые ЗУ, находящиеся в составе процессора или других устройств (т. е. внутренние для этих блоков), благодаря которым уменьшается число обращений к другим уровням памяти, реализованным вне процессора и требующим большего времени для операций обмена информацией;

- кэш-память, служащая для хранения копий информации, используемой в текущих операциях обмена. Высокое быстродействие кэш-памяти повышает производительность ЭВМ;

- основная память (оперативная, постоянная, полупостоянная), работающая в режиме непосредственного обмена с процессором и по возможности согласованная с ним по быстродействию. Исполняемый в текущий момент фрагмент программы обязательно находится в основной памяти;

- специализированные виды памяти, характерные для некоторых специфических архитектур (многопортовые, ассоциативные, видеопамять и др.);

- внешняя память, хранящая большие объемы информации. Эта память обычно реализуется на основе устройств с подвижным носителем информации (магнитные и оптические диски, магнитные ленты и др.). В настоящем пособии устройства внешней памяти не рассматриваются,

3.5.2 Классификация ЗУ

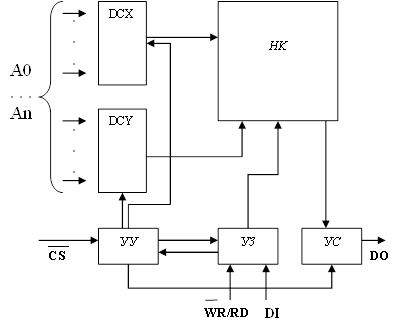

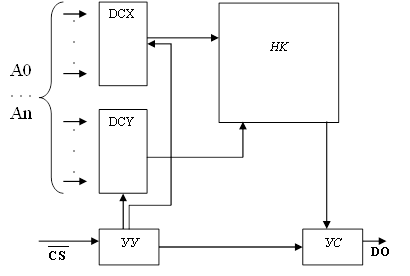

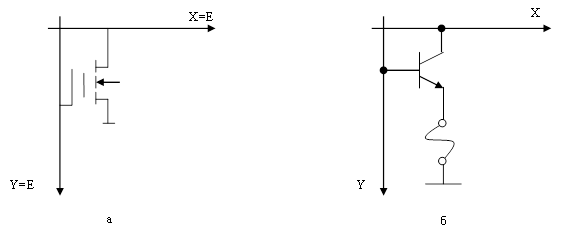

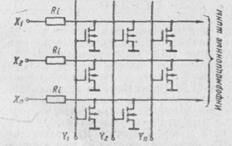

Для классификации ЗУ (рис. 3.1) важнейшим признаком является способ доступа к данным.

При адресном доступе код на адресном входе указывает ячейку, с которой ведется обмен. Все ячейки адресной памяти в момент обращения равнодоступны. Эти ЗУ наиболее разработаны, и другие виды памяти часто строят на основе адресной с соответствующими модификациями.

Адресные ЗУ делятся на RAM (Random Access Memory) u ROM (Read-Only Memory). Русские синонимы термина RAM: ОЗУ (оперативные ЗУ) или ЗУПВ (ЗУ с произвольной выборкой). Оперативные ЗУ хранят данные, участвующие в обмене при исполнении текущей программы, которые могут быть изменены в произвольный момент времени. Запоминающие элементы ОЗУ, как правило, не обладают энергонезависимостью, т.е. после отключения напряжения питания информация в них не сохраняется.

RОМ (русский эквивалент — ПЗУ, т. е. постоянные ЗУ). Содержимое либо вообще не изменяется, либо изменяется, но редко и в специальном режиме. Это "память только для чтения".

Рис. 3.1 Классификация полупроводниковых ЗУ

ЗУ делятся на статические и динамические. В первом варианте запоминающими элементами являются триггеры, сохраняющие свое состояние только при подключенном напряжении питания. Во втором варианте данные хранятся в виде зарядов конденсаторов, образуемых элементами МОП-структур. Саморазряд конденсаторов ведет к разрушению данных, поэтому они должны периодически (каждые несколько миллисекунд) регенерироваться, т.е. автоматически перезаписываться. В то же время плотность упаковки динамических элементов памяти в несколько раз превышает плотность упаковки, достижимую в статических RAM.

Статические ЗУ называются SRAM (Static RAM), а динамические — DRAM (Dynamic RAM).