Лекция 9. Состояния ПЛИС фирмы Xilinx

Лекция 9 – Состояния ПЛИС фирмы Xilinx

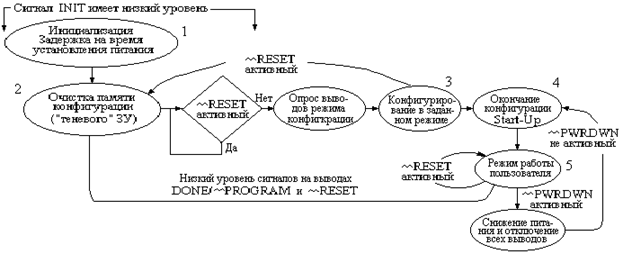

Состояния ПЛИС рассмотрены на примере МС серии ХС3000 фирмы Xilinx. ПЛИС могут находиться в одном из пяти состояний (см. рисунок 9.1):

1. инициализации;

2. очистки памяти конфигурации («теневого» ЗУ);

3. конфигурирования в заданном режиме;

4. запуска;

5. работы пользователя.

После включения питания и нарастания напряжения питания до +2,5… 3,0 В на выходе INIT (с открытым коллектором) устанавливается сигнал логического 0. Это означает, что ПЛИС перешла в состояние инициализации, которое длится несколько тысяч внутренних тактов (номинальной частоты 1 МГц). За это время напряжение питания успеет достичь +4 В. Для ведущих режимов конфигурирования состояние длится 216 тактов (что составляет от 43 до 130 мс), для не ведущих режимов – 214 тактов (от 11 до 33 мс).

После окончания инициализации все выходные буферы программируемых БВВ переходят в третье состояние и на выходах через высокоомный «подтягивающий» резистор устанавливается напряжение питания +5 В.

Рекомендуемые материалы

После этого наступает состояние очистки внутренней памяти конфигурации («теневого» ЗУ). Продолжительность этого состояния зависит от ёмкости «теневого» ЗУ и составляет (примерно):

200 тактов для ХС3020 (от 130 до 400 мкс),

250 тактов для ХС3030 (от 165 до 500 мкс),

290 тактов для ХС3042 (от 195 до 580 мкс),

330 тактов для ХС3064 (от 220 до 660 мкс),

375 тактов для ХС3090 (от 250 до 750 мкс).

Рисунок 9.1 – Диаграмма состояний ПЛИС серии ХС3000

Когда очистка заканчивается, внутреннее устройство управления ПЛИС проверяет входной логический уровень сигнала на выводе RESET (СБРОС). Если этот сигнал устанавливается (или уже установлен) в разрешающий уровень логической 1, выход с открытым коллектором INIT переходит в закрытое состояние, показывающее, что инициализация и очистка памяти закончились. После этого ПЛИС «защелкивает» значения сигналов на входах режимов конфигурирования М0, М1, М2 и переходит в состояние конфигурирования, во время которого в «теневое» ЗУ загружается программа конфигурации. Конкретный режим, используемый для загрузки программы в ПЛИС (т.е. режим конфигурирования), зависит от «защелкнутых» логических уровней на входах выбора режима (см. таблицу 9.1).

Таблица 9.1 – Режимы конфигурирования и значения сигналов на выводах выбора режима

| Наименование режима | М0 | М1 | М2 |

| Ведущий последовательный (Master Serial) | 0 | 0 | 0 |

| Ведущий параллельный низкий (Master Parallel Low) | 0 | 0 | 1 |

| Ведущий параллельный высокий (Master Parallel High) | 0 | 1 | 1 |

| Периферийный (Peripheral) | 1 | 0 | 1 |

| Подчинённый (Slave) | 1 | 1 | 1 |

| Скоростной (Express) | 0 | 1 | 0 |

Программа конфигурации представляет собой последовательный поток битов и загружается в «теневое» ЗУ как в сдвиговый регистр. На рисунке 9.2 показан вид битового потока, формируемого автоматически программой Foundation Series 2.1i фирмы Xilinx.

Программа конфигурации содержит битовое поле, которое указывает её длину. Когда вводится верное число бит, соответствующее данному значению длины, вывод Done/~Program ПЛИС (выход с открытым коллектором) переходит в высокоомное состояние, позволяющее через «подтягивающий» резистор (в том числе внутренний, специально предусмотренный для этой цели на кристалле) получить сигнал Done (СДЕЛАНО) – логическую 1, указывающую, что конфигурирование данной микросхемы завершено.

| 11111111 0010 197 разряда - счётчик> 0111 | - Начальные биты (4 бита минимум) - Начало заголовка (преамбула) - Длина программы конфигурации - Конец заголовка (4 бита минимум) | Заголовок |

| 0<Фрейм данных #001>111 0<Фрейм данных #002>111 0<Фрейм данных #003>111 … 0<Фрейм данных #195>111 0<Фрейм данных #196>111 0<Фрейм данных #197>111 | Для ХС3020 197 фреймов данных конфигурации Каждый фрейм содержит: - стартовый бит (0); - 71 бит данных; - три стоповых бита. | Программа конфигурации (повторяется для каждой ПЛИС в гирляндной цепи) |

| 1111 | Конец программы (постамбула) (4 бита минимум) |

Рисунок 9.2 – Структура битового потока конфигурации ПЛИС серии ХС3000

Процесс конфигурирования должен либо закончиться, либо его можно прервать и запустить снова. Частичное конфигурирование невозможно.

Во время конфигурирования ПЛИС для управления подключёнными к ней схемами пользователь может использовать два вывода ПЛИС с именами HDC и LDC (на этих выводах во время конфигурирования установлены сигналы логических 1 и 0 соответственно).

После окончания конфигурирования ПЛИС переходит в состояние работы пользователя и начинает выполнять логические функции, определённые разработчиком при проектировании устройства. Во время работы ПЛИС можно вновь перевести в состояние инициализации и повторить процесс конфигурирования. Возможность по переконфигурированию может быть запрещена установкой соответствующих битов в потоке битов конфигурации. В этом случае переконфигурирование ПЛИС осуществляется только через отключение и последующее включение питания.

Во время состояний инициализации, очистки памяти и конфигурирования на всех выводах ПЛИС (за исключением тех, которые используются в целях конфигурирования) внутреннее устройство управления ПЛИС поддерживает сигнал логической 1 через внутренние «подтягивающие» (к +5 В) резисторы. После перехода в состояние работы все контакты ввода/вывода ПЛИС одновременно начинают функционировать в соответствии с назначением, заданным разработчиком при проектировании устройства.

Однако перед началом работы ПЛИС проходит ещё одно состояние – состояние запуска, рассмотренное в следующей лекции.

Варианты конфигурации, задаваемые в программе Foundation Series 2.1i фирмы Xilinx. Битовый поток, кроме данных о конфигурации КЛБ и БВВ, содержит также ряд других установок, выбираемых пользователем в программе Foundation Series 2.1i фирмы Xilinx при формировании битового потока. При формировании битового потока для МС серии ХС3000 в программе Foundation Series 2.1i фирмы Xilinx пользователь может выбрать дополнительные варианты конфигурации, относящиеся ко всей ПЛИС, а именно:

· уровень входных сигналов;

· возможность обратного считывания;

· “подтягивающий” резистор на выводе DONE/~PROGRAM;

· время формирования сигнала завершения программирования DONE;

· время снятия внутреннего сигнала сброса MR (Master Reset);

· деление на два частоты кварцевого генератора.

Уровень входных сигналов. Во время конфигурирования все задействованные выводы имеют ТТЛ-совместимые уровни. После завершения конфигурирования пользователь может выбрать одновременно для всех входов либо ТТЛ- либо КМОП-совместимость. Входы DWRDWN, TCLKIN и BCLKIN имеют только КМОП-совместимые уровни. Следует учитывать, что ТТЛ-совместимость несколько увеличивает потребляемую мощность.

Возможность обратного считывания. Пользователь может выбрать однократное считывание, многократное считывание по команде или запретить эту возможность. Проведение обратного считывания позволяет не только проверить конфигурацию ПЛИС, но и считать состояния входов и выходов всех триггеров ЛБ и БВВ. Правда, для проверки состояния входов и выходов триггеров нужно знать их соответствующее место в потоке обратного считывания, а эта информация, к сожалению, в доступной документации отсутствует.

«Подтягивающий» резистор на выходе DONE/~PROGRAM (с открытым коллектором). Выбор этой возможности позволяет обойтись без внешнего резистора. Однако в гирляндной цепи при объединении выводов DONE/~PROGRAM «подтягивающий» резистор должен быть только в одной ПЛИС.

Времена формирования сигналов DONE и MR задают временную диаграмму четвёртого состояния ПЛИС – состояния запуска, рассмотренную в следующей лекции.

Деление на два частоты кварцевого генератора позволяет получить симметричный тактовый сигнал, вырабатываемый встроенным кварцевым генератором.

Вопросы для проверки усвоения материала

1. Состояния ПЛИС. Диаграмма состояний.

Информация в лекции "Орган зрения" поможет Вам.

2. Состояние очистки памяти конфигурации ПЛИС.

3. Программа конфигурации ПЛИС.

4. Структура битового потока конфигурации ПЛИС.

5. Дополнительные варианты конфигурации, задаваемые в программе Foundation Series 2.1i фирмы Xilinx.

Литература

1. Мальцев П.П., Гарбузов Н.И., Шарапов А.П., Кнышев Д.А. Программируемые логические ИМС на КМОП-структурах и их применение.1998. –М.: Энергоатомиздат, -159 с. (118-121 с.)