Лекция 8. Загрузка конфигурации в ПЛИС

Лекция 8 – Загрузка конфигурации в ПЛИС фирмы Xilinx

Режимы конфигурирования ПЛИС. Загрузка битового потока конфигурации производится по различным алгоритмам и схемам, в зависимости от выбранного режима конфигурирования. Режим конфигурирования определяется значениями логических сигналов на выводах М0, М1 и М2, предназначенных для выбора режима (см. таблицу 8.1).

Таблица 8.1 – Режимы конфигурирования и значения сигналов на выводах выбора режима

| Наименование режима | М0 | М1 | М2 |

| Ведущий последовательный (Master Serial) | 0 | Рекомендуемые материалыОтчет по лабораторной работе №1 "Построение модели изделия в PDM системе" Построение модели изделия в PDM системе КР - Расчет токовой защиты нулевой последовательности в сети с глухозаземленной нейтралью Разработка технологического процесса ковки детали Вариант 3 - Контрольная работа - Объектно-ориентированное программирование на С -60% Ответы к РК №1 0 | 0 |

| Ведущий параллельный низкий (Master Parallel Low) | 0 | 0 | 1 |

| Ведущий параллельный высокий (Master Parallel High) | 0 | 1 | 1 |

| Периферийный (Peripheral) | 1 | 0 | 1 |

| Подчинённый (Slave) | 1 | 1 | 1 |

| Скоростной (Express) | 0 | 1 | 0 |

Методы конфигурирования применимы для всех серий ПЛИC фирмы Xilinx. Однако поскольку их конкретные реализации в каждой серии хотя и незначительно, но различаются, изложение проведём на примере ХС3000 фирмы Xilinx.

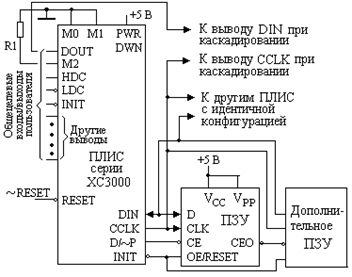

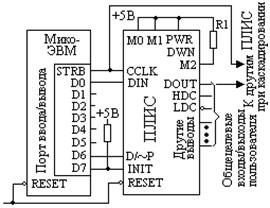

Конфигурирование ПЛИC серии ХС3000. На рисунках 8.1, 8.3, 8,5, 8.7 приведены схемы конфигурирования ПЛИС. Показанный на схемах резистор R1 позволяет использовать вывод М2 после конфигурирования как обычный

|

Рисунок 8.1 – Ведущий последовательный режим конфигурации | общецелевой вывод пользователя, т.е. для выполнения функций ввода/вывода сигналов при работе ПЛИС в составе системы. Малое сопротивление резистора R1 пересиливает влияние внутреннего «подтягивающего» резистора, подключённого к выводу во время конфигурирования. Ко всем общецелевым выводам при конфигурировании подключены внутренние резисторы, «подтягивающие» уровень сигнала на выводах к напряжению питания +5 В. Их номинальное сопротивление 100 кОм, такое под- |

ключение имеет место в любом режиме конфигурирования.

Если после конфигурирования предполагается производить обратное считывание, то последовательно с выводами М0 и М1 следует также включить резисторы сопротивлением 5 кОм. Из одного источника битового потока можно конфигурировать несколько ПЛИС, но для получения различной их конфигурации применяется каскадное включение.

Ведущий последовательный режим (см. рисунок 8.1) конфигурации

|

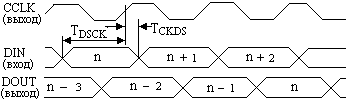

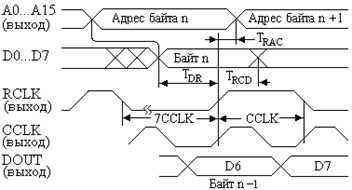

Рисунок 8.2 – Временная диаграмма ведущего последовательного режима конфигурации | использует последовательное одноразрядное ПЗУ. Для этих целей фирма Xilinx разработала МС ПЗУ серии ХС1700, выпускаемые в восьмивыводных керамических и пластмассовых DIP-корпусах (со штыревыми выводами и шагом между ними 2,54 мм), а также в более |

миниатюрных корпусах типа SOIC (с планарными выводами и шагом между

| Таблица 8.2 – Параметры сигналов ведущего последовательного режима конфигурации

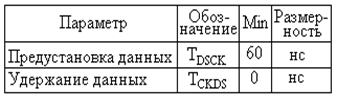

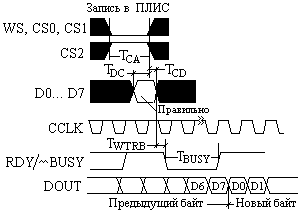

| ними 1,27 мм). Временная диаграмма ведущего последовательного режима приведена на рисунке 8.2, а её параметры – в таблице 8.2. Ведущий параллельный режим (см. рисунок 8.3) конфигурации предполагает хранение про- |

граммы конфигурации в восьмиразрядном ПЗУ с произвольной выборкой. Би-

|

Рисунок 8.3 – Ведущий параллельный режим конфигурации |

Рисунок 8.4 – Временная диаграмма ведущего параллельного режима конфигурации Таблица 8.3 – Параметры сигналов ведущего параллельного режима конфигурации

|

товой поток может храниться, начиная с нулевого адреса (для режима Master Low), или с верхнего адреса (для режима Master High). Хранение битового потока с верхнего адреса используется, когда в этой же микросхеме ПЗУ размещаются программы микропроцессоров, тем самым удаётся сократить количество микросхем ПЗУ на печатной плате.

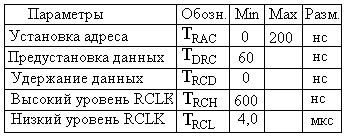

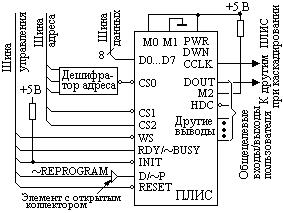

Периферийный режим конфигурации (см. рисунок 8.5) предполагает наличие вспомогательного дешифратора адреса, подключаемого к системной шине. Когда на выходе этого дешифратора (и, следовательно, на входе CSO) устанавливается сигнал логического 0, а на входы CS1 и CS2 подаются сигналы 0 и 1 соответственно, то ПЛИС подготавливается к приёму одного байта би-

|

Рисунок 8.5 – Периферийный режим конфигурации |

Рисунок 8.6 – Временная диаграмма периферийного режима конфигурации |

тового потока конфигурации с шины данных, выставляя сигнал “Готов” (Ready) – логическую 1 на выходе RDY/~BUSY (знак ~ обозначает, что активным уровнем является логический 0; это обозначение эквивалентно черте над

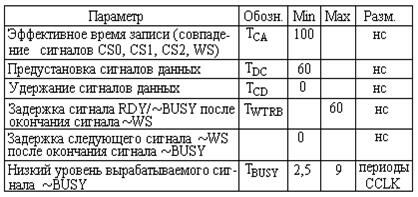

| Таблица 8.4 – Параметры сигналов периферийного режима конфигурации

| именем сигнала). Этот байт запоминается по заднему фронту сигнала WS и затем записывается в «теневое» ЗУ. На время записи ПЛИС вырабатывается сигнал «Занято» (Busy) – логический 0 на выводе RDY/~BUSY. Временная диаграмма периферийного режима |

конфигурации приведена на рисунке 8.6, её параметры – в таблице 8.4.

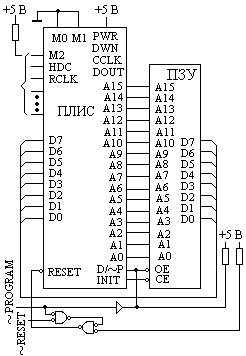

Подчинённый последовательный режим конфигурации (см. рисунок 8.7)

|

Рисунок 8.7 – Подчинённый последовательный режим конфигурации |

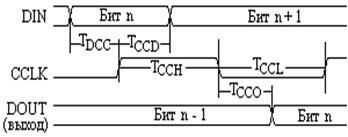

Рисунок 8.8 – Временная диаграмма подчинённого режима конфигурации |

предполагает побитную подачу потока конфигурации из внешнего источника.

Приём производится по переднему фронту тактового сигнала, подаваемого на вход CCLK. Для начала конфигурирования на вход D/~P следует подать сигнал логического 0 (в течение нескольких микросекунд). Когда счётчик тактовых импульсов на кристалле ПЛИС насчитает заданное количество импульсов, активизируются входы/выходы ПЛИС и выход D/~P переходит в высокоомное состояние. Временная диаграмма подчинённого режима приведена на рисунке 8.8.

Вопросы для проверки усвоения материала

1. Режим и схема конфигурации ПЛИС серии ХС3000 фирмы Xilinx:

Вместе с этой лекцией читают "8 - Физиология головного мозга".

· ведущий последовательный;

· ведущий параллельный;

· периферийный;

· подчинённый последовательный.

Литература

1. Мальцев П.П., Гарбузов Н.И., Шарапов А.П., Кнышев Д.А. Программируемые логические ИМС на КМОП-структурах и их применение.1998. –М.: Энергоатомиздат, -159 с. (112-118 с.)