Лекция 10. Начало работы ПЛИС

Лекция 10. Начало работы ПЛИС фирмы Xilinx после конфигурирования

Начало работы ПЛИС определяется пятым состоянием – состоянием запуска (Start-Up), которое является промежуточным состоянием между конфигурированием и работой в системе. В этом состоянии происходит переключение от одного источника тактовых сигналов (тактовые сигналы конфигурации) к другому (системные тактовые сигналы).

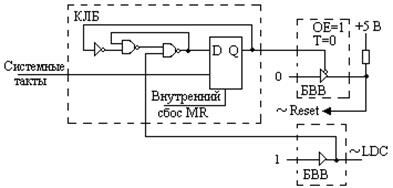

Временная диаграмма окончания процессов конфигурирования приведена на рисунке 10.1, где показано, что пользователь может выбирать моменты формирования сигнала DONE, сигнализирующего о завершении конфигурирования, и снятия внутреннего сигнала сброса MR (Master Reset) со всех триггеров ПЛИС. Для каждого из сигналов можно установить момент на один такт раньше или на один такт позже активизации входов/выходов. Этот выбор программируется при создании битового потока конфигурации в программе Foundation Series 2.1i.

Однако следует учитывать, что процесс конфигурирования не синхронизирован с тактовой частотой системы, с которой должна работать ПЛИС после конфигурирования, а потому могут возникнуть проблемы в момент его окончания.

Рисунок 10.1 – Окончание конфигурирования ПЛИС серии ХС 3000

Как известно, по переднему фронту последнего тактового сигнала конфигурации CCLK снимается сигнал внутреннего сброса MR, удерживающий триггеры КЛБ и БВВ в состоянии 0. Но к этому моменту уже работает кварцевый генератор, активна внутренняя логика ПЛИС. Поэтому на входах D и EC триггеров скорее всего установлены неправильные сигналы, которые по приходу первого системного тактового импульса на С-вход триггера переведут его в неверное состояние.

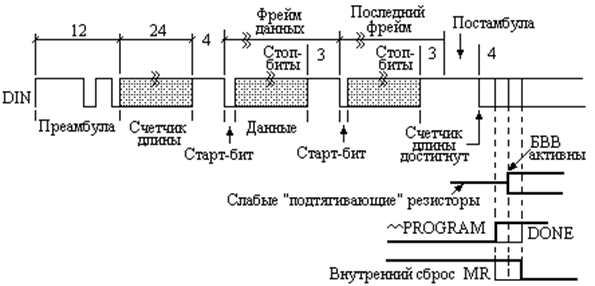

Схема формирования синхронного сигнала ~RESET после окончания процесса конфигурирования ПЛИС. На рисунке 10.2 показана схема, позволяющая устранить эту проблему. Схема использует один КЛБ и два БВВ, один из которых тот, что вырабатывает во время конфигурирования сигнал ~LDC (Low During Configuration – низкий уровень сигнала во время конфигурации). Во время конфигурирования сигнал ~Reset схемы по рисунку 9.2, соединённый с входом RESET ПЛИС, не активен (т.е. равен логической 1), но все триггеры ПЛИС удерживаются в 0 внутренним сигналом сброса MR, действующим только во время конфигурирования. После окончания конфигурирования сигнал ~LDC снимается, на D-вход триггера подаётся сигнал 1, но сигнал ~Reset продолжает удерживаться в логической 1, так как выход Q триг-

|

Рекомендуемые материалыFREE Лабораторные работы в Ansys МТ7 Все для лабораторной работы [Осадка кольцевой заготовки] ЛР №2 - Изучение основ работы с киберсредой виртуальных предприятий FREE Все для лабораторной работы [Оптимизация раскроя листового материала] FREE Все для лабораторной работы [Исследование операции вытяжки цилиндрического стакана из плоской заготовки] FREE Все для лабораторной работы [Обработка эксперимента по определению приведенного модуля объемной упругости жидкости] Рисунок 10.2 – Формирование синхронного сигнала ~Reset | гера находится в состоянии 0. По первому системному тактовому импульсу триггер перебрасывается в 1, сигнал ~Reset переходит в 0 и снова сбрасывает все триггеры ПЛИС, в том числе и триггер рассматриваемой схемы, после чего сигнал ~Reset переходит в 1 (т.е. внутренний сброс MR снимается). |

Однако, кратковременного нахождения триггера в 1 оказывается достаточным для установки на D-входе логического 0. Поэтому последующие системные тактовые импульсы не перебросят триггер. Следовательно, сигнал ~Reset больше не будет вырабатываться схемой и со второго системного тактового импульса ПЛИС начнёт функционировать в соответствии с запрограммируемой конфигурацией.

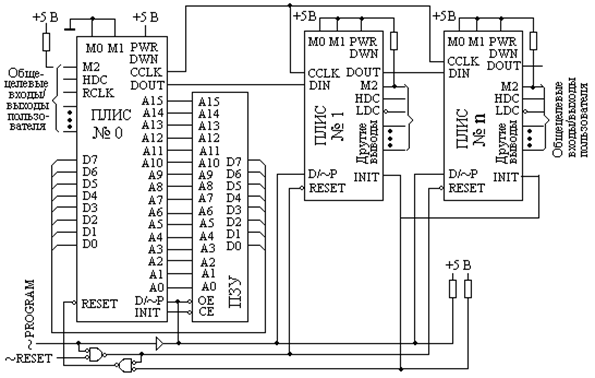

Рисунок 10.3 – Каскадирование ПЛИС при конфигурировании

Каскадирование ПЛИС при конфигурировании. Способность ПЛИС вырабатывать 16-разрядный адрес ПЗУ обеспечивает возможность хранения множества программ конфигурации в одиночном ПЗУ, благодаря чему из одного источника могут конфигурироваться несколько ПЛИС, соединённых в гирляндную цепь. Причём первая ПЛИС использует ведущий режим конфигурирования, остальные – подчинённый, управляемый от первой ПЛИС. На рисунке 10.3 приведён пример гирляндной цепи.

С целью обеспечения правильной конфигурации всех ПЛИС, соединённых в гирляндную цепь, первая ПЛИС (№ 0 на рисунке 9.3), конфигурируемая в ведущем режиме, имеет в 16 раз длиннее паузу инициализации после включения питания, чем длительность инициализации в подчинённом режиме. Это гарантировано обеспечивает инициализацию подчинённых ПЛИС (№1…№ n). Для большей гарантии инициализации всех подчинённых ПЛИС можно увеличить задержку до начала конфигурирования с помощью сигнала ~RESET (логического 0), поступающего на входы RESET всех ПЛИС.

Битовый поток конфигурации, автоматически получаемый с помощью программы Foundation Series 2.1i, представляет соединение битовых потоков всех ПЛИС и имеет один общий заголовок с указателем суммарной длины потока.

После начала конфигурирования заголовок битового потока проходит через все ПЛИС от входа Din к выходу Dout (с задержкой на 1 такт в каждой ПЛИС) и поэтому все ПЛИС узнают, сколько тактов CCLK будет длиться конфигурирование. После загрузки заголовка на выходе Dout устанавливаются сигналы логической 1. Это значение сохраняется до тех пор, пока не заполнится все «теневые» ЗУ. Таким образом, ведущая ПЛИС первую часть битового потока конфигурации записывает в своё «теневое» ЗУ, а оставшуюся часть передаёт через выход Dout на подчинённые ПЛИС. Первая подчинённая ПЛИС «забирает» свою часть битового потока конфигурации и т.д. Когда же счётчики тактовых сигналов насчитают нужное количество тактов, указанное в заголовке битового потока, все ПЛИС завершат конфигурирование.

Вопросы для проверки усвоения материала

4.2 Синтез адаптивного управления при помощи ПИ-регулятора - лекция, которая пользуется популярностью у тех, кто читал эту лекцию.

1. Начало работы ПЛИС после конфигурирования.

2. Временная диаграмма окончания процесса конфигурирования ПЛИС.

3. Схема формирования синхронного сигнала ~RESET после окончания процесса конфигурирования ПЛИС.

4. Каскадирование нескольких ПЛИС, соединённых в гирляндную цепь, при конфигурировании. Схема соединения ПЛИС.

Литература

1. Мальцев П.П., Гарбузов Н.И., Шарапов А.П., Кнышев Д.А. Программируемые логические ИМС на КМОП-структурах и их применение.1998. –М.: Энергоатомиздат, -159 с. (122-126 с.)