Способы обмена данными

6.2. Способы обмена данными

6.3.1. Общая программная модель периферийного устройства.

Вводом-выводом (ВВ) называется передача данных между ядром ЭВМ, включающим в себя МП и память, и периферийными устройствами.

За время эволюции ЭВМ подсистема ВВ претерпела наибольшие изменения благодаря расширению сферы применения ЭВМ и появлению новых периферийных устройств.

Общие принципы ввода-вывода (ВВ), характерные для большинства ЭВМ:

1) При наличии нескольких периферийных устройств необходимо генерировать специальный сигнал выбора, идентифицирующий активное устройство.

2) ВВ в медленно действующих устройствах организуется по прерываниям, а в быстродействующих на основе прямого доступа к памяти.

3) Операции ВВ инициируются только в том случае, если периферийное устройство готово к ним. Подключение периферийных устройств к системной шине осуществляется посредством электронных схем, называемых интерфейсами ВВ. Они согласуют уровни электрических сигналов, а также преобразуют машинные данные в любой формат, необходимый устройству, и наоборот.

В процессе ВВ передается информация двух видов: управляющие коды (слова) и собственно данные.

Рекомендуемые материалы

Управляющие слова (или приказы) инициируют действия, не связанные непосредственно с передачей данных, например запуск устройства запрещения прерываний и т.п.

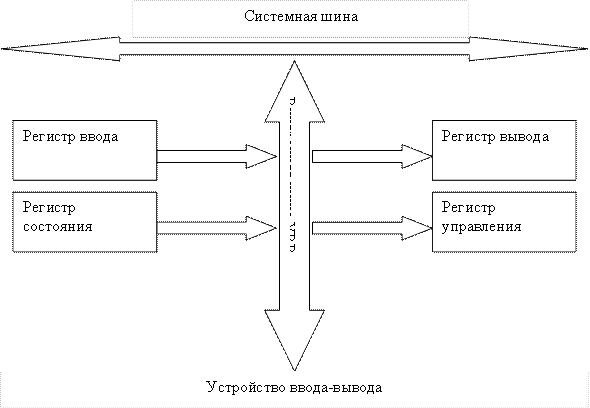

Управляющие данные от периферийных устройств называются словами состояния. Они содержат информацию об определенных признаках, например о готовности устройства к передаче данных, о наличии ошибок и т.п.. Состояние обычно представляется в декодированной форме – один бит для каждого признака. Группа бит, к которым МП обращается в операции ВВ, образует регистр (порт) ВВ. Наиболее общая программная модель периферийного устройства содержит четыре регистра: регистр выводимых данных (выходной порт), регистр вводимых данных (входной порт), регистр управления и регистр состояния. Каждый из этих регистров должен иметь однозначный адрес, который идентифицируется дешифратором адреса. На рисунке показана схема периферийного устройства

Рисунок - Общая программная модель периферийного устройства

Рисунок - Общая программная модель периферийного устройства

6.3.2. Программно-управляемая передача данных.

При данном методе передачи специальная программа реализуемая МП, управляет обменом данными. Отличительной особенностью этого способа обмена является использование одной или нескольких специальных команд, инициирующих этот обмен. Известны два типа программно управляемой передачи данных: синхронная и асинхронная.

Наиболее простой является синхронная передача данных. Такой вид обмена еще называется прямым или безусловным. Процедура ввода-вывода (ВВ) выполняется независимо от состояния периферийного устройства (ПУ). Синхронная передача данных возможна только при управлении всегда готовыми к обмену простейшими ПУ: светодиодными индикаторами, реле, датчиками случайных чисел и т.п.

При необходимости ВВ в нужном месте программы используются команды IN или OUT. При этом типе передачи устройство ВВ должно быть готово к приему или передаче данных за время, равное времени выполнения определенной команды МП. Синхронная передача производится при минимальных затратах технических и программных средств. Синхронный обмен используется редко. Синхронная передача данных является составной частью более сложных процедур программно-управляемого обмена к числу которых относится асинхронный ВВ.

Способность ПУ к скоростному ВВ данных не безгранична и, как правило, во много раз ниже скорости работы МП. Поэтому прежде чем приступить к чтению данных из порта ввода, необходимо удостовериться, что ПУ готово предоставить эти данные. В противном случае неразрешенный вывод со стороны МП может привести к потере нового или предыдущего элемента данных. Аналогичная ситуация складывается и при выводе данных, когда требуется проверка готовности ПУ к приему новых данных.

Способность ПУ к скоростному ВВ данных не безгранична и, как правило, во много раз ниже скорости работы МП. Поэтому прежде чем приступить к чтению данных из порта ввода, необходимо удостовериться, что ПУ готово предоставить эти данные. В противном случае неразрешенный вывод со стороны МП может привести к потере нового или предыдущего элемента данных. Аналогичная ситуация складывается и при выводе данных, когда требуется проверка готовности ПУ к приему новых данных.

Асинхронный обмен широко используется в микро-ЭВМ. Для большинства ВУ до выполнения операций ВВ нужно убедиться в их готовности к обмену, т.е. ВВ является асинхронным. Состояние ВУ характеризуется флагом готовности READY. Этот флаг представляет собой однобитовый регистр внешнего устройства. Если ВУ осуществило все подготовительные операции перед обменом, то оно устанавливает в состояние 1 свой флаг. Процессор проверяет флаг готовности с помощью одной или нескольких команд. Если флаг установлен, то МП приступает к обмену данными. Если флаг сброшен, то происходит возврат к команде проверки флага READY до тех пор, пока устройство не будет готово к операциям ВВ. Данный цикл ожидания готовности ВУ в различных МП реализуется по разному. Алгоритм работы микро-ЭВМ при асинхронной передаче данных показан на рисунке.

Для иллюстрации асинхронный передачи данных рассмотрим ввод данных с 8-разрядного порта, который подключен как устройство 1. Триггер состояния порта 1 рассматривается как устройство 2 и подсоединен к разрядной линии 4 шины данных.

Часть программы, реализующая асинхронный ввод, показана ниже.

IN 2; m1 Переслать в А информацию из порта 2

ANI 10H; Наложить маску для выделения 4-го разряда

JZ m1; Если Z=1, то перейти к m1

IN 1; Переслать данные в А (синхронная передача).

В данной программе по команде IN 2 информация из порта 2 (триггер состояния) записывается в аккумулятор. Если устройство готово, в ANI 10H маскируются все разряды, кроме 4, и устанавливается флажок «нуль», если устройство не готово. Команда JZ m1 организует цикл повторения рассмотренных операций до тех пор, пока устройство не будет готово. По команде IN 1 осуществляется синхронная передача данных из устройства 1 в аккумулятор.

Асинхронная передача является пригодной в случае согласования временных различий между ПУ и МП. Однако асинхронному обмену данными присущи существенные недостатки:

1. МП вынужден ожидать, пока ВУ не будет готово к обмену. Время ожидания может быть большим;

2. Если флаговый триггер по какой-либо причине не устанавливается в единичное состояние, то МП вообще не выйдет из режима ожидания;

3. Программно-управляемая передача данных не может быть начата по запросу от УВВ.

Эти факторы являются существенными недостатками программно-управляемой передачи данных. Они вызвали появление различных схем прерываний.

6.3.3. Передача данных с использованием системы прерываний.

Прерывание – непредусмотренное обращение к подпрограмме. Микро-ЭВМ имеет два вида прерываний: внутренние и внешние. Внутренние при возникновении в МП необычных ситуаций, а внешние прерывания – по требованию устройств ВВ, подсоединенных к общей магистрали.

Обслуживание ВУ по прерываниям является альтернативой программно-управляемому обмену. Если при программном управлении как начало процедуры обмена, так и ее исполнение находятся под управлением программы, то обслуживание по прерываниям инициируется аппаратными средствами УВВ. Совокупность этих средств, команд и программ их обслуживания называется системой прерываний. Обмен с прерыванием основной программы существенно экономит время МП, затрачиваемое на передачу данных в сравнении с асинхронным обменом. Это происходит за счет того, что исчезает необходимость в организации программных циклов ожидания готовности ВУ, на выполнение которых тратится значительное время, особенно при обмене с медленными ВУ.

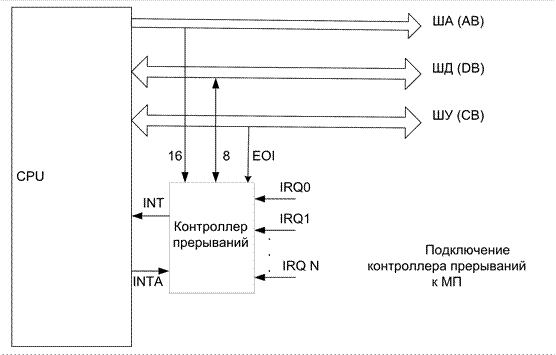

В микро-ЭВМ обычно используется одноуровневая система прерываний, т.е. запросы на прерывание от всех ВУ поступают на один вход МП, а именно на вход INT. Сигнал запроса прерывания устанавливает в 1 триггер прерывания INTE. Единичное состояние этого триггера разрешает обслуживание прерывания. Установка и сброс бита разрешения прерывания осуществляются программным способом. Команда EI МП 8080 разрешает прерывание, т.е. устанавливает триггер прерывания INTE в 1. Команда DI запрещает прерывания, т.е. сбрасывает INTE в состояние 0. При уровне 0 прием запросов прерывания МП невозможен.

EI (Enable interrupts) – разрешение прерываний

DI (Disable interrupts) – запрещение прерываний

В некоторых МП триггер INTE реализуется как один из разрядов регистра состояния МП. Поскольку запросы от всех ВУ поступают на один вход МП INT, то возникает необходимость идентификации ВУ, запросившего обслуживание, и реализации заданной очередности (приоритета) обслуживания ВУ при одновременном поступлении запросов на прерывание.

Общая последовательность реакции процессора на сигнал прерывания содержит следующие действия:

1) Периферийное устройство генерирует сигнал прерывания, который подается на вход INT процессора. На этой линии по схеме ИЛИ объединяются запросы всех устройств, работающих в режиме прерываний.

2) МП завершает текущую команду и, если прерывания разрешены, формирует сигнал INTA подтверждения прерывания. До получения этого сигнала устройство сохраняет активный уровень сигнала INT.

3) Осуществляется запоминание содержимого PC и некоторых других регистров МП в стеке, причем содержимое PC запоминается автоматически.

4) МП идентифицирует прерывающее устройство для перехода к соответствующей подпрограмме обслуживания.

5) Выполняется подпрограмма обслуживания прерывания.

6) Восстанавливается состояние прерванной программы, для чего запомненное содержимое регистров извлекается из стека.

7) Возобновляется выполнение прерванной программы

Любое прерывание можно рассматривать как аппаратный вызов подпрограммы. Так как команды ВВ в основной программе отсутствуют, МП после завершения каждой команды проверяет наличие сигнала прерывания до перехода к следующей команде. Например, в МП КР580 анализ состояния входной линии INT осуществляется в такте Т2 последнего машинного цикла каждой команды. Переход к подпрограмме обслуживания прерывания происходит, если только INT=1 и прерывания разрешены.

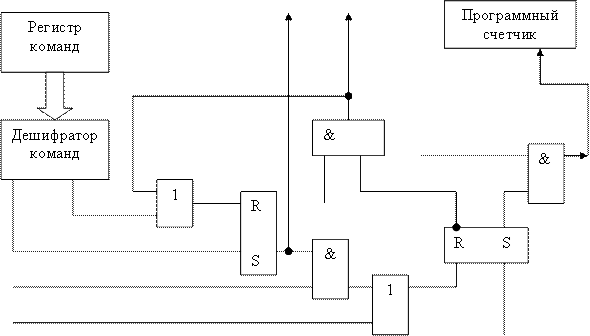

МП реагирует на запросы маскируемых прерываний по линии INT, если установлен внутренний триггер разрешения прерывания INTE. Состояние этого триггера определяет выходной сигнал разрешения прерывания с такой же мнемоникой INTE. Если INTE=0, прерывания запрещены (замаскированы) и МП не отвечает на сигнал INT=1. С помощью команд разрешения EI и запрещения DI прерываний можно программно управлять состоянием триггера INTE. При восприятии прерывания триггер прерываний IFF переводится в нулевое состояние, что приводит к запрещению инкремента программного счетчика (PC) и генерированию сигнала подтверждения прерывания INTA. Внутренняя для МП схема прерываний показана на рисунке.

INTE INTA

+1

сигнал

инкремента

INTE

EI DI

строб

IFF

INT

NMI

Рисунок. Внутренняя схема прерываний.

При появлении сигнала INTA сбрасывается триггер INTE и в дальнейшем разрешить прерывания можно только командой EI. После выполнения команды EI МП обязательно выполнит еще одну команду, даже если на входе INT действует сигнал прерывания INT=1. Для данной схемы прерываний каждая подпрограмма обработки прерываний должна последней содержать команду EI.

Подпрограмма обслуживания запроса прерывания должна быть оформлена таким образом:

DI - запрет прерывания;

Программа обслуживания;

POP PSW – восстановление содержимого регистров МП;

EI – разрешение прерывания;

RET – возврат к прерванной программе.

Запросы немаскируемых прерываний по входу NMI процессор воспринимает всегда, независимо от того, разрешены прерывания или нет. Однако до реакции на сигнал NMI МП все же завершает выполнение текущей команды. Обычно на вход NMI подается сигнал от схемы, фиксирующей уменьшение напряжения питания ниже минимального допустимого уровня. Быстродействия МП достаточно чтобы за время от момента восприятия сигнала NMI до уменьшения напряжения сети ниже критического уровня выполнить несколько команд. Этими командами содержимое всех внутренних регистров и другая важная информация записываются в энергонезависимую память с резервным аккумуляторным питанием.

Когда в ЭВМ имеется несколько периферийных УВВ, работающих в режиме прерываний, сигналы их запросов на обслуживание объединяются по схеме ИЛИ и подаются на вход INT МП. Поэтому при наличии сигнала INT=1 без дополнительных действий и аппаратных средств невозможно определить какое УВВ должен обслуживать МП, тем более, что запросы на обслуживание могут формироваться одновременно несколькими УВВ. Таким образом, возникает проблема идентификации прерывающего устройства, т.е. однозначного перехода к определенной подпрограмме обслуживания. Разработано несколько способов решения этой проблемы:

1. Программный полинг (опрос);

2. Аппаратный полинг;

3. Векторные и вложенные прерывания.

Прерывание подпрограмм обслуживания прерываний называется вложением прерываний.

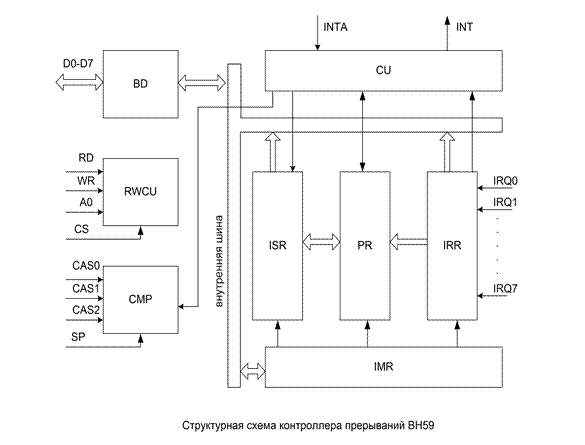

Большими возможностями обладает БИС КР580ВН59 программируемого контролера прерываний. Схема может быть запрограммирована на следующие режимы работы.

Вложенные прерывания. Каждому из 8 входов запросов прерываний IRQ0 – IRQ7 назначается фиксированный приоритет в порядке возрастания и запрос с большим приоритетом прерывает обслуживание прерываний с меньшими приоритетами.

Круговой (циклический) приоритет. Как и в предыдущем режиме, каждому входу IRQ0 – IRQ7 назначается приоритет, но теперь после запроса прерывания и выполнения соответствующей подпрограммы обслуживания приоритеты изменяются в круговом порядке таким образом, что последний обслуженный вход будет иметь низший приоритет. Этот режим характерен для таких применений, в которых периферийные устройства имеют одинаковый приоритет и ни одному из них нельзя отдать предпочтение.

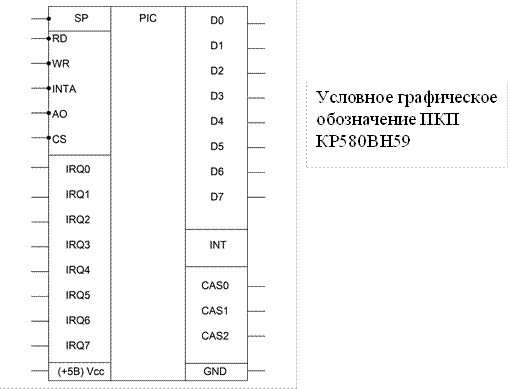

Контроллер имеет следующие управляющие сигналы:

1) CS (выбор кристалла) – L-активный входной сигнал разрешает связь ПКП с ШД.

2) WR (запись) – L-активный сигнал загрузки данных с ШД в адресуемый регистр ПКП.

3) RD (считывание) – L-активный вход инициирующий передачу на ШД информации о состоянии ПКП.

4) INT (прерывание) – выходной Н- активный сигнал, который подается на вход прерывания МП.

5) INTA (подтверждение прерывания) – входной L- активный сигнал от МП, на которой ПКП реагирует выдачей команды CALL.

6) АО (адрес) – входной сигнал, адресующий внутренний регистр ПКП при загрузке приказов и считывании состояния. Обычно подключается к младшей линии А0 шины адреса. Если А0=1, то происходит запись приказов инициализации. Если А0=0, то команда записывается в регистр рабочих приказов.

7) CAS2 – CASO – при наличии в системе нескольких ПКП образуют локальную шину и являются выходными линиями ведущего контроллера и входными для ведомых контроллеров.

8) SP – линия определения контроллера как ведущего (SP=1) или ведомого (SP=0).

Существуют два основных способа идентификации ВУ, запросивших обслуживания:

1. программный опрос (полинг) контроллеров ВУ;

2. использования векторов прерывания.

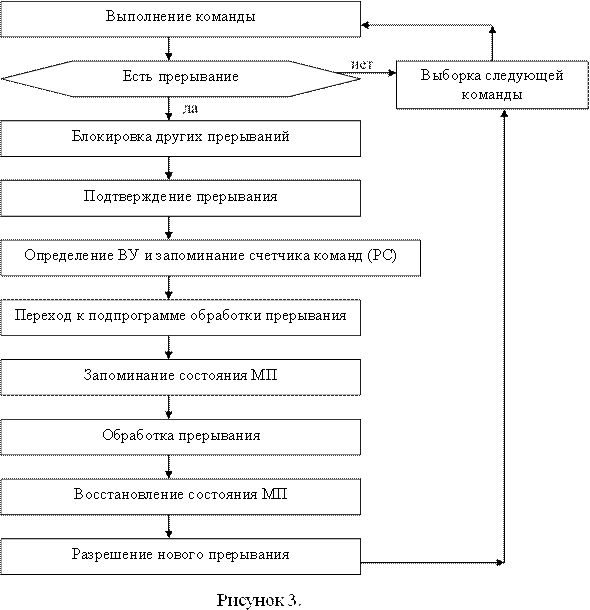

При осуществлении передачи данных с прерыванием программы реализуется следующая последовательность шагов:

1. Периферийное устройство запрашивает прерывание.

2. После завершения выполнения МП текущей команды он выдает сигнал подтверждения готовности к прерыванию на выход INTE.

3.

|

Запоминается содержимое счетчика команд (PC) и осуществляется переход по адресу подпрограммы обработки прерывания.

4. Запоминается содержимое внутренних регистров МП (РОН и регистра признаков) и выполняется передача данных под управлением специальной программы.

5. Осуществляется возврат к продолжению выполнения основной программы. На рисунке 3 представлена блок-схема передачи данных с использованием прерываний.

Запрос на прерывание инициируется путем подачи сигнала на вывод INT МП. В наборе команд многих МП имеется специальная команда блокирования этого вывода. При заблокированном выводе запрос игнорируется и продолжается выполнение обычной последовательности команд. В противном случае по завершении цикла текущей команды подается сигнал на вывод INTE и начинается цикл прерывания. Обычно после выполнения шага 2 прерывание блокируется, что позволяет завершить обработку текущего прерывания до поступления следующего. Далее определяется устройство, выдавшее запрос, и запоминается содержимое РС и т.д.

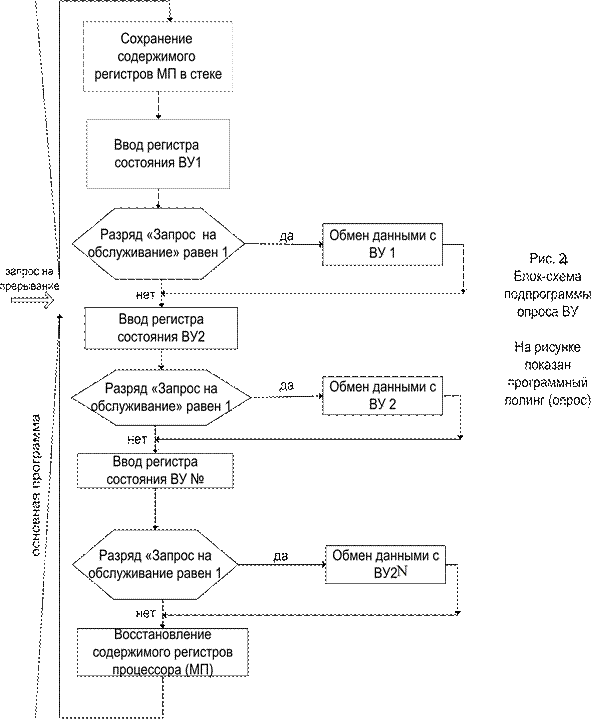

Организация прерываний с программным опросом готовности предполагает наличие в памяти микро-ЭВМ единой подпрограммы обслуживания прерываний от всех ВУ. Структура такой подпрограммы приведена ниже на рисунке 4.

Обслуживание ВУ с помощью единой подпрограммы обработки прерываний производится следующим образом. В конце последнего машинного цикла выполнения текущей команды основной программы процессор проверяет наличие требования прерывания от ВУ. Если сигнал прерывания есть и в МП прерывание разрешено, то МП переключается на выполнение подпрограммы обработки прерываний. После сохранения содержимого регистров МП, используемых в подпрограмме, начинается последовательный опрос регистров состояния контроллеров всех ВУ. Отдельно анализируется значение разряда «Запрос на обслуживание» этих регистров. Как только подпрограмма обнаружила готовое к обмену ВУ, сразу выполняются действия по его обслуживанию, т.е. вызывается программа обслуживания, соответствующая данному порту ВВ. Завершается подпрограмма обработки прерывания после опроса готовности всех ВУ и восстановления содержимого регистров МП.

Приоритет ВУ при программном опросе готовности однозначно определяется порядком их опроса в подпрограмме обработки прерываний. Чем раньше опрашивается ВУ, тем меньше время реакции на его запрос и выше приоритет. Необходимость проверки готовности всех ВУ существенно увеличивает время обслуживания тех ВУ, которые опрашиваются последними. Это является основным недостатком рассматриваемого способа организации прерываний. Поэтому обслуживание прерываний с опросом готовности ВУ используется только в тех случаях, когда отсутствуют жесткие требования на время обработки сигналов прерываний ВУ.

Использование векторов прерываний позволяет устранить указанный недостаток. В системах прерываний по вектору ВУ, запросившее обслуживания, само идентифицирует себя с помощью вектора прерывания.

Вектор прерывания – адрес ячейки памяти микро-ЭВМ, в которой хранится либо первая команда подпрограммы обслуживания прерывания данного ВУ, либо адрес начала такой подпрограммы. МП получив вектор прерывания, сразу переключается на выполнение требуемой подпрограммы обработки прерывания без процедуры опроса ВУ. В микро-ЭВМ с векторной системой прерываний каждое ВУ должно иметь собственную подпрограмму обработки прерывания. МП указывает на возможность прерываний по сигналу на выходе INTE. Если на этом выходе присутствует уровень 1, то запросы прерываний могут приниматься. Если уровень 0, то запросы восприниматься не будут. МП автоматически устанавливается в состояние запрета восприятия запросов прерывания после начала обслуживания запроса прерывания. Векторное (направленное) прерывание возникает тогда, когда УВВ, выставившее запрос на прерывание, посылает после удовлетворения запроса адрес A1-An ячейки памяти, где расположена программа прерывания данного УВВ.

Если запрос прерывания воспринят, то начинается цикл обслуживания прерывания. Сперва устанавливается уровень «0» на выходе INTE. Далее ВУ передает по ШД в МП код команды CALL <A1><A2>=CD. Получив команду CALL, МП автоматически переходит в режим ввода двух байт адреса A1 и A2, которые являются адресом подпрограммы обработки прерывания, т.е. его вектором. Команда CALL сама сохраняет содержимое PC в стеке.

Система векторных прерываний может быть построена различными способами. Наиболее эффективно система векторных прерываний реализуется с помощью специальной БИС, называемой программируемым контроллером прерываний (ПКП). Сам ПКП может рассматриваться как расширение МП. По этой причине его часто называют сопроцессором обработки прерываний. Например, ПКП КР580ВН59 является устройством, формирующим запрос на прерывание работы МП КР580ВМ80 и выдающим на ШД команду CALL <A1><A2>. В рассматриваемом случае вектор прерывания формирует БИС ПКП или контроллер ВУ. Упрощенная схема взаимодействия контроллера прерываний с МП показана ниже.

|

IRQ (Interrupt Request) – запрос (требование) прерывания

EOI (End of Interruption) – команда конца прерывания

INT – сигнал, поступающий на вход запроса прерывания МП БИС

INTA – строб подтверждения приема МП запроса INT. (Это есть потенциал разряда D0 слова состояния SW)

|

На основе ПКП ВН59 формируется 8-уровневая приоритетная система векторных прерываний для МП КР580ВМ80. Несколько контроллеров ВН59 могут соединяться каскадно для расширения числа уровней прерывания до 64. БИС ПКП представляет собой устройство, реализующее до восьми уровней запросов на прерывания с возможностью программного маскирования и изменения порядка обслуживания прерываний. За счет каскадного включения БИС ПКП число уровней прерывания может быть расширено до 64. Структурная схема ПКП приведена на рисунке.

IRR (Interrupt Request Register) – регистр запросов прерываний. Хранит все уровни, на которые поступают запросы IRQx;

PR (Priority Resulver) – шифратор приоритетов, схема принятия решений по приоритетам. Схема идентифицирует приоритет запросов и выбирает запрос с наивысшим приоритетом.

ISR (In Service Register) – регистр обслуживания прерываний. Содержит все запросы, которые в данное время находятся в стадии обработки

IMR (Interrupt Mask Register) – регистр маскирования прерываний. Хранит маски прерываний. Обеспечивает запрещение одной или некоторых линий запросов прерывания. Запрет некоторого уровня соответствует единице в этом разряде IMR.

BD – Буфер данных. Предназначен для сопряжения ПКП с системной шиной данных.

RWCU – блок управления записью/чтением. Принимает управляющие сигналы от МП и задает режим работы ПКП. Схема содержит программно-доступные регистры для записи слов начальной установки и управляющих слов. Блок позволяет слову состояния БИС поступать на внешнюю МД.

Входы блока:

CS (Chip Select) идентифицирует обращение к ПКП – уровень «0» на этом входе означает выборку схемы;

RD (Read) – уровень «0» на этом входе позволяет БИС передавать на внешнюю МД содержимое регистров IRR, ISR, IMR;

WR (Write) – уровень «0» на этом входе позволяет записывать слово управления в схему RWCU;

A0 – вход указания нулевого разряда адреса ПКП;

CMP – схема каскадного буфера–компаратора. Используется для включения в систему нескольких ПКП.

CU – схема управления. Вырабатывает сигналы прерывания и формирует команду CALL для выдачи на шину данных.

CAS0, CAS1, CAS2 (Cascade) – при каскадировании контроллеров служат для идентификации ведомого контролера.

Отличительной чертой схемы контроллера прерываний является ее программируемость. Поэтому БИС ВН59 относится к программируемому интерфейсу.

Программируемым называют такой интерфейс, функции которого могут быть изменены при помощи команд, выполняемых МП. Программирование осуществляется двумя типами управляющих слов: командами инициализации ICW и управления OCW.

Три команды инициализации ICW1 – ICW3 (Initialization Control Word) загружаются перед началом работы и служат для установки БИС в исходное состояние.

Команды управления OCW1 – OCW3 (Operation Control Word) могут быть переданы в ПКП в любое время после окончания инициализации. Они предназначены для оперативного управления работой контролера. Несколько КП используют для расширения числа входов запросов прерываний. При использовании в микро-ЭВМ нескольких КП необходимо определять управляющую и управляемые схемы. Для этой цели служит вход выборки ведомой схемы SP. Если SP=1, то схема определена как ведущая, при SP=0 БИС будет работать как ведомая. SP – Slave Program

Рассмотрим работу одной схемы ВН59. Один или несколько запросов на прерывания (переход от 0 к 1) подаются на входы IRQ0-IRQ7 и запоминаются в регистре запросов IRR. Логическая схема блока PR сравнивает приоритеты поступивших запросов с приоритетом запросов, находящихся на обслуживании. При превышении первых ПКП генерирует сигнал INT. МП подтверждает прием запроса INT генерацией строба INTA, под воздействием которого запрос с высшим приоритетом из IRR фиксируется в одном из разрядов регистра ISR. Далее ПКП генерирует код команды CALL, который принимается МП. Код операции CALL вызывает формирование двух дополнительных импульсов INTA. В ответ МП инициирует еще два следующих друг за другом INTA- цикла. Во время этих циклов ПКП передает в МП полный адрес программы обслуживания прерывания, принятого к обработке. Установленный в ISR бит остается в состоянии «1» до окончания процедуры обслуживания. конце подпрограммы в ПКП должна быть передана специальная команда окончания прерывания EOI, которая сбрасывает соответствующий ISR-бит. До тех пор, пока некоторый ISR-бит установлен, все запросы с равным или меньшим приоритетом

|

игнорируются. В тоже время запросы с более высоким приоритетом приводят к генерации сигнала INT, инициируя вложенные прерывания МП.

Режим полностью установленных приоритетов прерываний схема имеет сразу после окончания выполнения команд начальной установки, и он не требует дополнительных слов управления для его задания. Приоритеты прерывания в этом режиме последовательно уменьшаются от высшего на входе IRQ0 до низшего на входе IRQ7, и их порядок неизменен. Специальным словом управления в БИС КР580ВН59 можно задать режим перемещаемых приоритетов. В этом случае реализуется циклический сдвиг приоритетов с присвоением низшего только что обслуженному уровню.

6.3.4. Организация прямого доступа к памяти.

Программно управляемый обмен данными предполагает передачу данных из ВУ в аккумулятор, а затем в память или наоборот, из памяти в аккумулятор, а потом в выходной регистр. Однако, программно управляемая пересылка данных – это медленный процесс. При пересылке больших массивов данных это обстоятельство вызывает определенные проблемы. Ранее рассмотренные методы обмена данными относились к передачам между ВУ и МП.

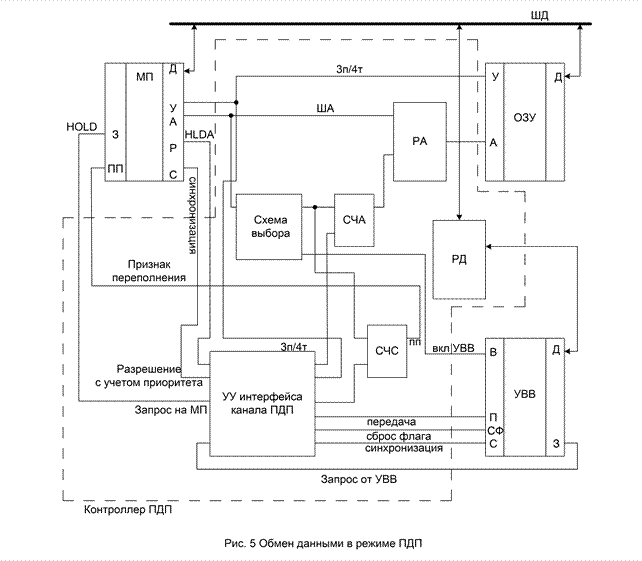

Прямой доступ к памяти (ПДП) – это способ организации быстрой пересылки данных при обмене информацией между памятью и ВУ (внешними устройствами).

Если требуется осуществить обмен между ВУ и памятью, то нет необходимости пересылать данные через МП. В этом режиме обмен данными между ВУ и ОЗУ происходит без участия МП. Обычно между памятью и ВУ обмен данными заключается в пересылке массивов информации. Построение канала ПДП является альтернативой программному обмену. Обменом в режиме ПДП управляет не программа, выполняемая МП, а электронная схема БИС, внешняя по отношению к МП.

Аппаратные средства реализации канала ПДП называются контроллером ПДП (КПДП). Схема, управляющая обменом в режиме ПДП, размещается в специальном контроллере, который называется контроллером прямого доступа к памяти.

Для реализации режима прямого доступа к памяти необходимо обеспечить непосредственную связь контроллера ПДП и памяти микро-ЭВМ. Для этой цели можно было бы использовать специально выделенные ША и ШД, связывающие контроллер ПДП и ОЗУ. Однако такое решение значительно усложнит микро-ЭВМ. В целях сокращения количества линий в шинах микро-ЭВМ контроллер ПДП подключается к ОЗУ посредством шин адреса и данных системного интерфейса. При этом возникает проблема совместного использования шин системного интерфейса МП и контроллером ПДП.

В МП с возможностью ПДП для их принудительного отключения от ША и ШД имеются специальные выводы HOLD и HLDA. Запрос на начало режима прямого доступа к памяти подается контроллером ПДП на вход HOLD (захват) МП БИС. МП, получив этот сигнал, приостанавливает выполнение текущей команды, не дожидаясь ее завершения, выставляет на свой выход HLDA управляющий сигнал предоставления ПДП и отключается от шин адреса и данных. С этого момента все шины микро-ЭВМ управляются контроллером ПДП. МП во время передачи информации по каналу ПДП переводит схемы управления магистралями в высокоомное состояние и тем самым изолируется от остальной части системы. Состояние внутренних регистров замораживается, т.е. МП в режиме ожидания сохраняет то информационное состояние, которое было в нем к моменту удовлетворения запроса канала ПДП.

Интерфейс канала ПДП по сложности превосходит другие типы интерфейсов. Хотя его структура может быть упрощена за счет программной реализации части функций, это не представляется целесообразным, так как основная цель использование режима ПДП – обеспечение высокой скорости передачи данных. Передача данных в режиме ПДП имеет приоритет перед другими видами обмена. Режим ПДП всегда требует предварительной подготовки: для каждого ВУ необходимо выделить область памяти, используемую при обмене, и указать ее размер (количество записываемых в память или читаемых из памяти байт информации). Поэтому любой КПДП имеет в своем составе регистр адреса и счетчик байт. На рисунке 5 представлена схема реализации канала ПДП. Перед переходом в режим ПДП МП загружает в регистры его контроллера следующую информацию: в счетчик байт – количество принимаемых байт данных, в регистр адреса – начальный адрес области памяти для вводимых или выводимых данных.

УВВ вырабатывает сигнал запроса на цикл обращения к ОЗУ, который через УУ интерфейса канала ПДП поступает на МП (вход HOLD). МП отвечает сигналом разрешения на захват цикла с учетом приоритета УВВ (выход HLDA). УУ сигналом CФ (сброс флага) сбрасывает в нуль триггер ВУ, тем самым сообщая ему о начале цикла ПДП. После этого в УУ устанавливается единичное состояние триггер активности, что приводит к передаче из МП в регистр адреса РА адреса первой ячейки памяти ОЗУ передаваемого массива данных. Далее сигналом П (Передача) инициируется передача данных между УВВ и ОЗУ. Обмен между ОЗУ и УВВ происходит через буферный регистр данных РД. УВВ предоставляется только один цикл работы микро-ЭВМ. Поэтому после записи в ОЗУ или чтения одного байта данных триггер активности УУ сбрасывается в «0», а МП возобновляет выполнение основной программы. Когда УВВ подготовится к следующему обмену, оно вновь установит в «1» свой флаговый триггер, что приведет к посылке в УУ нового запроса на доступ к памяти. Предварительно в РА должен быть установлен новый адрес ячейки ОЗУ и посчитано число уже переданных байт данных. Для выполнения этих функций в контроллер ПДП введены два счетчика: счетчик слов (СЧС) и счетчик адреса (СЧА). СЧС изначально загружается числом передаваемых байт (кодом длины массива), а СУА – начальным адресом ОЗУ. В процессе обмена после каждого обращения к ОЗУ производится инкремент адреса в СЧА и декремент счетчика байт СЧС. Переполнение счетчика слов СЧС является признаком конца массива. Поэтому признак переполнения (ПП) останавливает передачу данных, КПДП прекращает формирование сигналов запроса ПДП и этот режим заканчивается .

В МПК серии К580 входит программируемый контроллер прямого доступа к памяти КР580ВТ57. Этот КПДП позволяет осуществлять двунаправленный обмен массивами данных емкостью до 16 Кбайт между ОЗУ и любым из четырех ВУ без участия МП. При одновременном поступлении запросов от ВУ программируемая логика схемы позволяет выбирать наивысший по приоритету канал ПДП.

Очень часто обмен в режиме ПДП происходит между устройствами внешней памяти и ОЗУ. В ЭВМ используется временное разделение (мультиплексирование) общей системной шины между МП и КПДП. В обычных условиях системной шиной распоряжается МП. Когда инициируется режим ПДП, шиной «распоряжается» КПДП, управляя передачами данных между ОЗУ и внешней памятью (или УВВ). При этом действия МП приостанавливаются и он отключается от системной шины. Электрическое отключение достигается переводом тристабильных буферов на шине адреса, шине данных и некоторых линиях управления в состояние высокого выходного сопротивления.

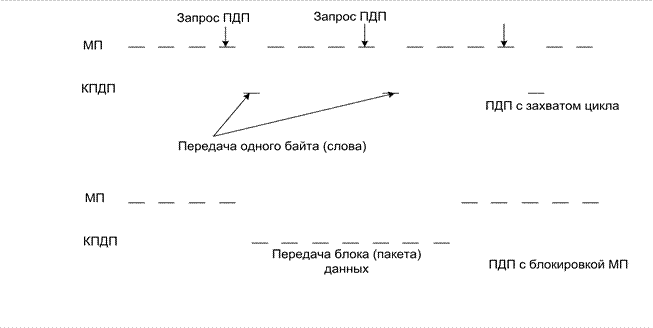

Существует ПДП с «захватом цикла» и ПДП с блокировкой микропроцессора. При ПДП с «захватом цикла» КПДП формирует сигнал HOLD, посылаемый в МП, и заставляет его отключаться от системной шины на несколько тактов. После принятия запроса ПДП микропроцессор выдает в системный интерфейс управляющий сигнал HLDA и приостанавливает свои действия. В случае ПДП с захватом цикла МП освобождает системную шину на время тактов Т4 и Т5 текущего машинного цикла. В течение тактов Т4 и Т5 системной шиной управляет КПДП и между ОЗУ и ВУ передается один байт данных (байт или слово). Тем самым выполнение программы замедляется, но в меньшей степени, чем при обмене в режиме прерывания.

При выполнении передач ПДП содержимое регистров МП не изменяется, поэтому его не нужно запоминать в стеке, а затем восстанавливать, как при обработке прерываний. Выполнение основной программы возобновляется сразу после снятия сигнала запроса ПДП HOLD. Иллюстрация разновидностей ПДП приведена на рисунке.

ПДП с блокировкой МП отличается от ПДП с «захватом цикла» тем, что управление системным интерфейсом передается КПДП не на время обмена одним байтом, а на время обмена блоком данных. Такой режим ПДП необходим в тех случаях, когда время обмена одним байтом с ВУ сопоставимо с циклом микропроцессора. В этом случае МП не успевает выполнить хотя бы одну команду между очередными операциями обмена в режиме ПДП.

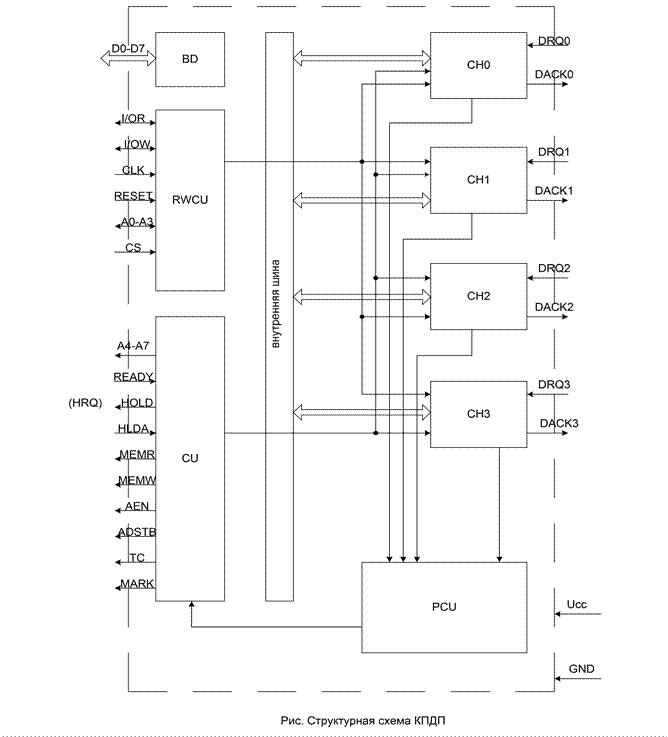

Программируемый контроллер прямого доступа к памяти КР 580ВТ57.

Структурная схема контроллера показана на рисунке ниже. КПДП предназначен для управления обменом данными между ВУ и ОЗУ ЭВМ. Контроллер управляет процессом предоставления прямого доступа к памяти, формирует в процессе обмена последовательность адресов ячеек памяти и сигналы управления обменом.

Эта схема имеет следующие блоки:

1) Двунаправленный двустабильный буфер данных BD, предназначенный для обмена информацией между МП и КПДП.

2) Схема управления чтением /записью RWCU, которая адресует внутренние регистры КПДП и управляет обменом по шине D0-D7.

3) Блок управления CU содержит регистры режима и состояния КПДП и задает режим работы КПДП.

4) Блок управления приоритетами PCU обеспечивает порядок обслуживания запросов ВУ.

5) Четыре канала прямого доступа CH0-CH3.

Рассмотрим назначение выводов БИС КПДП.

CLK (Clock) - сигнал синхронизации (вход тактовых импульсов);

(D0-D7) – шина данных;

IOR – считывание ввода-вывода. Input/Output Read ;

IOW – запись ввода-вывода. Input/Output Write;

RESET – сброс. Загрузка нулевого байта в регистр режима;

(A0-A3) – младшие разряды шины адреса;

CS – выбор кристалла (разрешение обмена с БИС);

(A4-A7) – старшие разряды шины адреса;

READY – готовность памяти (ОЗУ) к обмену;

HOLD (HRQ) (Hold Request) – запрос прямого доступа к памяти (захват шин);

HLDA (Hold Acknowledge) – подтверждение прямого доступа к памяти;

MEMR (Memory Read) – чтение из памяти;

(MEMW) (Memory Write) – запись в память;

AEN (Address Enable) – разрешение адреса. Управление работой шинных формирователей;

ADSTB (Address Strobe) – строб адреса. Запись старшего байта адреса во внешний регистр;

TC – окончание счета. Последний цикл прямого доступа в память;

MARK – маркер. Указывает на то, что до конца передачи блока данных необходимо выполнить количество циклов обмена кратное 128;

(DRQ0-DRQ3) (DMA Request); DMA – Direct Memory Access – прямой доступ к памяти. Запрос прямого доступа к памяти со стороны ВУ по каналам CH0-CH3. H-уровень указывает на запрос от УВВ.

|

(DACK0-DACK3) (DMA Acknowledge) – разрешение ПДП. L-уровень указывает на разрешение обмена.

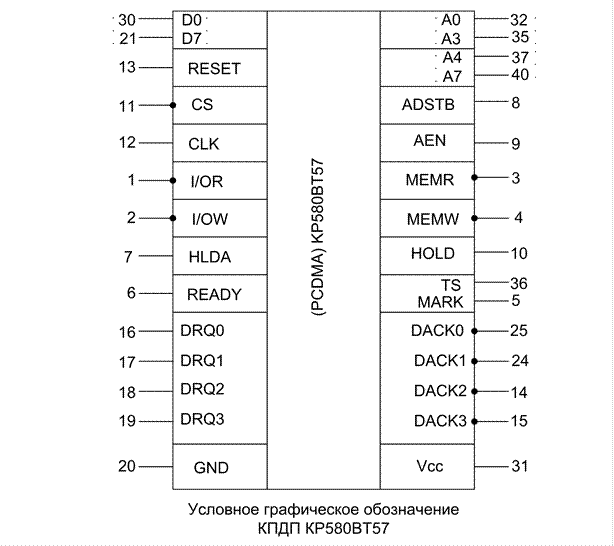

БИС программируемого контроллера прямого доступа к памяти КР580ВТ57 показана на рисунке ниже.

Управление работой каждого канала ПДП (CH0-CH3) осуществляется с помощью двух 16-разрядных регистров; регистра начального адреса и регистра управления. В регистр начального адреса при программировании БИС заносится начальный адрес передаваемого массива данных. В 14 младших разрядах регистра управления размещается счетчик, в который заносится число на единицу меньше длины передаваемого массива данных, т.е. размер массива не может превышать 16 Кбайт. 15-й и 14-й разряды регистра управления определяют тип операции обмена: 00-контроль, 01-запись в память, 10-чтение из памяти, 11-запрещенное состояние.

Связь КПДП с системным интерфейсом ЭВМ осуществляется по шине данных D0-D7 через буфер BD. Запись информации в регистры начального адреса и управления каналов контроллера производится программным путем. Адресуются регистры КПДП по линиям A0-A3. В состав контроллера также входят регистр состояния и регистр приказов.

Регистр состояния по сигналу ТС отображает окончание передачи массивов данных по каналам ПДП. Приоритеты входных запросов на предоставление прямого доступа устанавливаются программно записью информации в регистр приказов, либо фиксированные (DRQ0 – высший, DRQ3 - низший), либо циклические, т.е. последнему обслуженному запросу присваивается низший приоритет, а приоритеты остальных запросов изменяются в круговой последовательности. Для формирования 16-разрядного адреса ячейки памяти КПДП использует внешний 8-разрядный регистр. В этот регистр в начале цикла ПДП контроллер с использованием строба ADSTB по ШД D0-D7 записывает восемь старших разрядов адреса A8-A15. Выходы внешнего регистра подключаются к линиям А8-А15 ША ЭВМ. Младшие разряды адреса формируются на выходах A0-A7 контроллера (КПДП).

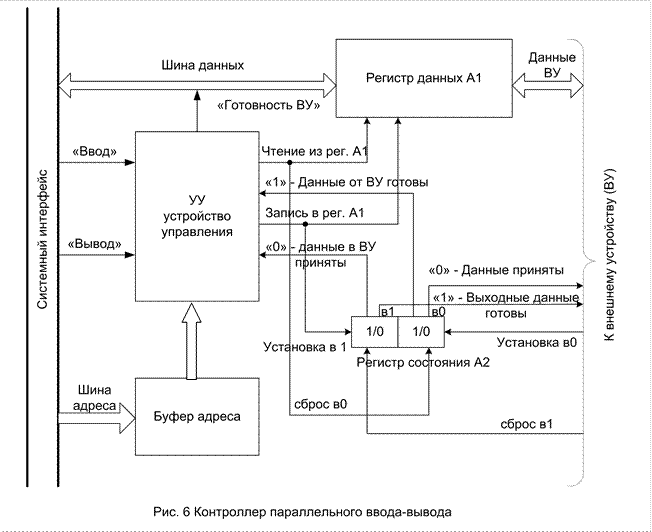

6.3.5. Параллельная передача данных.

Существуют два способа передачи слов информации по линиям данных: параллельный, когда одновременно пересылаются все биты слова, и последовательный, когда биты слова пересылаются поочередно.

Параллельный ВВ наиболее простой и широко распространенный способ обмена информацией с ВУ, при котором не требуется промежуточного преобразования данных. Поэтому параллельный обмен информацией производится непосредственно портами ввода-вывода (ВВ). При использовании параллельного интерфейса 8-разрядный МП за каждую операцию обмена обеспечивает передачу 8 бит информации. Для организации параллельной передачи данных помимо ШД используется минимальное количество управляющих сигналов. На рисунке 6 представлена схема обеспечения параллельного 8-битового ввода-вывода данных. Это есть схема контролера ВУ, который обеспечивает побайтную передачу данных.

В рассматриваемой схеме обеспечения ВВ данных имеется регистр состояния А2, с помощью которого МП может проверить готовность данных к передаче. Таким образом, устраняется возможность потери данных и обеспечивается их корректная передача. Регистр состояния А2 имеет только два разряда в0 и в1. Рассмотрим процесс ввода данных. ВУ записывает в регистр данных контроллера А1 очередной байт данных и управляющим сигналом «Данные от ВУ готовы» устанавливает в единицу разряд в0 регистра состояния А2. Единица в в0 служит для МП признаком готовности данных к обмену. При этом в УУ формируется сигнал «Готовность ВУ», передаваемый в МП по одной из линий ШД посредством операций ввода при реализации программы асинхронного обмена. Тем самым контроллер извещает МП о том, что передаваемые данные находятся в регистре А1. МП, выполняя программу асинхронного обмена, читает байт данных из А1 и обнуляет бит в0. Далее формируется управляющий сигнал «Данные приняты» для ВУ.

Рассмотрим как контроллер ВУ обеспечивает параллельную передачу данных из ВУ под управлением программы асинхронного обмена. Алгоритм асинхронного ввода следующий:

1. МП проверяет наличие данных в регистре данных контроллера А1;

2. Если данные готовы (в0=1), то они передаются из регистра А1 на ШД и далее в аккумулятор или ячейку памяти микро-ЭВМ. Иначе повторяется пункт 1.

Запишем фрагмент программы приема байта данных в асинхронном режиме с использованием параллельного интерфейса

MOV D, A2 ; адрес порта А2 помещаем в регистр D.

m1: IN A, D ; чтение байта из порта А2.

ANI 01Н ; наложить маску для выделения разряда в0 регистра А2.

JZ m1 ; переход на метку m1 если разряд Z не нулевой, т.е. Z=1

MOV D, A1 ; адрес порта А1 записывается в регистр D.

IN A, D ; передать данные регистра А1 в аккумулятор.

В третьей строке выполняется проверка содержимого регистра А2, точнее признака наличия данных в регистре данных А1. Единица в нулевом разряде (в0=1) подтверждает, что данные от ВУ записаны в А1 и их необходимо переслать в МП. Нуль в разряде в0 указывает на неготовность данных от ВУ и на необходимость вернуться к проверке готовности.

Рассмотрим процесс вывода данных. Байт данных записывается в порт вывода А1. Одновременно в разряд в1 регистра состояния А2 записывается логическая единица. При этом формируется управляющий сигнал «Выходные данные готовы» в шине связи с ВУ. Затем, ВУ, приняв байт данных, управляющим сигналом «Данные приняты» обнуляет (сбрасывает) разряд в1 регистра А2. Далее формируется управляющий сигнал «Готовность ВУ» передаваемый в МП по одной из линий ШД посредством операции ввода при реализации программы асинхронного обмена.

1. МП проверяет готовность ВУ к приему данных.

2. Если ВУ готово к приему данных (в1=0), то данные передаются с ШД в регистр А1 и далее во ВУ. Иначе повторяется пункт 1.

Как видно из рассмотренных примеров, для приема или передачи байта данных МП требуется выполнить всего несколько команд, время выполнения которых и определяет максимально достижимую скорость обмена данными при параллельной передаче. Таким образом, при параллельной передаче обеспечивается высокая скорость обмена данными, которая ограничивается только быстродействием ВУ.

|

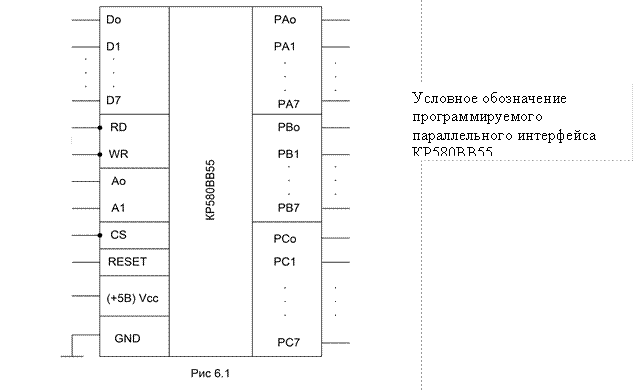

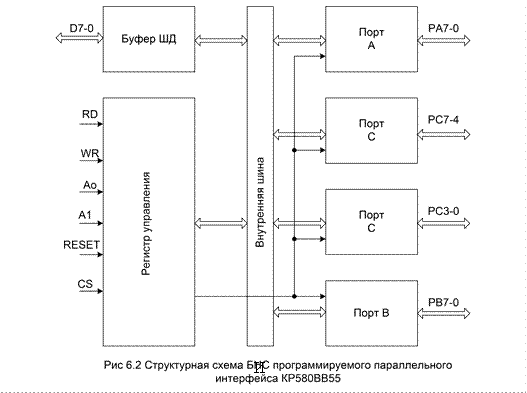

Обмен данными с ВУ в параллельном формате исключительно широко используется в микро-ЭВМ. Поэтому создание БИС, управляющей параллельным обменом данными, явилось естественным шагом в развитии средств МП техники. БИС КР580ВВ55 обеспечивает подключение ВУ к ШД микро-ЭВМ через три независимых двунаправленных канала (порта) ввода-вывода: A,B,C. Схема выводов микросхемы параллельного интерфейса КР580ВВ55 показана на рисунке 6.1. Структурная схема программируемого параллельного интерфейса КР580ВВ55 показана на рисунке 6.2.

D0-D7 –двунаправленная шина данных для передачи данных, управляющих слов и информации состояния.

PA0-PA7, PC0-PC7, PB0-PB7 – двунаправленные магистрали данных каналов А, С и В соответственно.

RD – чтение данных из адресуемого регистра БИС.

WR – запись данных в адресуемый регистр БИС.

Для адресации внутренних регистров БИС, коммутируемых на шину данных, используются линии А0 и А1 шины адреса системного интерфейса: 00 – порт А, 01 – порт В, 10 – порт С, 11 – регистр управления.

CS – сигнал разрешения обмена с БИС (Сигнал управления третьим состоянием шины данных). Высокий уровень запрещает, а низкий разрешает связь прибора с системной шиной данных.

|

RESET – сигнал устанавливает БИС в начальное состояние, в котором регистр управления обнуляется, а все три порта переводятся в режим ввода. Программирование БИС (настройка на требуемый режим обмена) производится с помощью команд IN и OUT. Считывание из регистра управления (RD=0, A0=A1=1) не допускается, а одновременная запись и считывание (RD=0 и WR=0) приводят к непредсказуемым результатам.

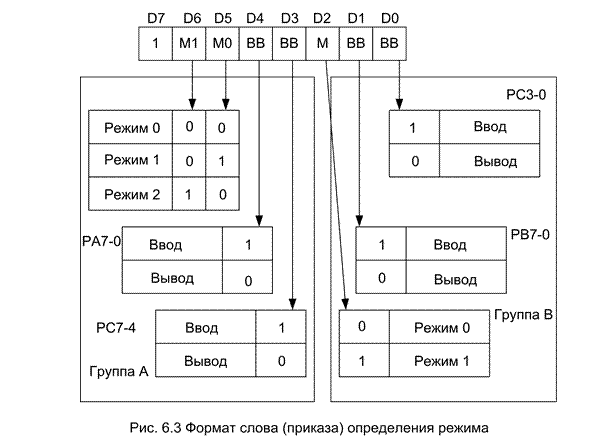

При программировании БИС в регистр управления командой OUT записывается управляющее слово, которое определяет один из трех режимов работы параллельного интерфейса. Режим 0 – программно-управляемый ВВ данных в синхронном режиме по трем 8-разрядным каналам А,В,С. Каждый канал может быть использован только для ввода или вывода информации, а канал С дополнительно может быть разделен на два 4-разрядных канала.

Режим 1 – обмен данными с ВУ по каналам А и В в асинхронном режиме и режиме прерывания программы. Управляющие сигналы при этом передаются по каналу С.

Режим 2 – двунаправленный обмен данными с ВУ по каналу А в режиме прерывания программы. Канал С используется для передачи управляющих сигналов. В регистр управления можно только записывать управляющие слова. Чтение данных из регистра управления невозможно. Так как БИС не имеет внутреннего регистра состояния схемы, то для его определения считывают содержимое регистра канала С и интерпретируют отдельные его разряды.

Программирование адаптера параллельного интерфейса заключается в загрузке управляющего слова в регистр управления. Формат слова управления показан ниже.

|

Данный режим (приказ) идентифицируется условием D7=1. Например, приказ конфигурации порта А на ввод в режим 0, порта В на вывод в режим 1, бита 3 порта С на ввод и бита 7 порта С на вывод имеет код 10010101. Этот код загружается в аккумулятор командой MVI и выводится в регистр управления контроллера (БИС программируемого параллельного интерфейса) командой OUT.

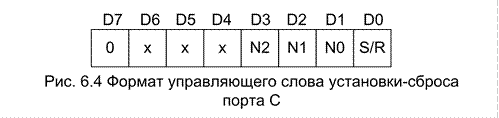

Управляющее слово может устанавливать разные режимы работы для каждого из портов. Порт А может работать в любом из трех режимов, порт В – в режимах 0 и 1. Порт С можно использовать для передачи данных только в режиме 0. В остальных режимах его используют для передачи управляющих сигналов, которые сопровождают процесс обмена в портах А и В. Отдельные разряды порта С можно устанавливать или сбрасывать программно с помощью управляющего слова формат которого показан на рисунке ниже.

Биты N2, N1, N0 задают номер разряда, который требуется установить или сбросить в регистре С. 000-С0; 001-С1; 010-С2; 011-С3; … 111-С7; х – любое значение (0 или 1). Бит S/R задает режим установки или сброса разряда порта С выбранный значениями N2-N0. Если S/R=1, то в разряд записывается единица, при S/R=0 происходит сброс. БИС программируемого параллельного интерфейса используют для соединения МП со стандартными периферийными устройствами: дисплеем, телетайпом, накопителем.

|

Технология БИС позволяет создавать универсальные многофункциональные интерфейсные устройства ввода-вывода параллельной информации. Такие устройства как правило программируемы и применяются для двунаправленной передачи данных и сигналов управления. Примером может служить программируемый периферийный адаптер КР580ВВ55. Эта БИС есть программируемое устройство, используемое для ВВ параллельной информации. Схема позволяет осуществлять обмен 8-разрядными данными по трем каналам – А,В,С. Направление обмена и режим работы для каждого канала задаются программно.

6.3.6. Последовательная передача данных.

Так как между отдельными проводниками шины для параллельной передачи данных существует электрическая емкость, то при изменении сигнала, передаваемого по одному из проводников, возникает помеха (короткий выброс напряжения) на других проводниках. С увеличением длины шины, а, следовательно, увеличением емкости проводника помехи возрастают и могут восприниматься приемником как сигналы. Поэтому рабочее расстояние для шины параллельной передачи данных ограничивается длинной 1-2м. Только за счет снижения скорости передачи и существенного удорожания шины ее длину можно увеличить до 10-20м. Поэтому широкое распространение получил последовательный способ обмена данными между ВУ и ЭВМ, а также между несколькими ЭВМ.

Возможны два режима последовательной передачи данных: синхронный и асинхронный. При синхронной последовательной передаче каждый передаваемый бит данных сопровождается импульсом синхронизации, информирующим приемник о наличии на линии бита данных. Следовательно, между передатчиком и приемником должны быть протянуты три провода: два для передачи импульсов синхронизации и бит данных, а также общий заземленный провод. Это обстоятельство и необходимость использования для обмена дорогих линий связи помешало широкому распространению синхронной передачи.

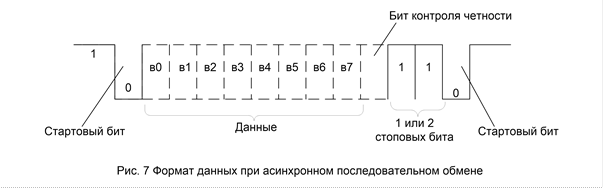

Асинхронная последовательная передача данных означает, что у передатчика и приемника нет общего генератора синхроимпульсов и сигнал синхронизации не посылается вместе с данными. Как в таком случае приемник будет узнавать о моментах начала и завершения передачи слова данных. Для решения указанной проблемы существует специальный формат асинхронной последовательной передачи данных.

|

При передаче символов меньше 8 неиспользованные биты заполняют нулями. Стандартный формат данных содержит n пересылаемых бит информации, (n=5÷8). Имеется также 3-4 бита служебной информации: стартовый бит, бит контроля четности или нечетности и 1-2 стоповых бита. Бит четности (нечетности) может отсутствовать. Полученная совокупность бит носит название кадра.

До начала передачи информации на линии связи сохраняется уровень логической «1». Перед началом передачи каждого слова данных располагается стартовый бит «0». Затем следует посылка битов данных, начиная с младшего бита. Данные могут сопровождаться контрольным битом, соответствующим четности/нечетности в передаваемом коде. Завершается посылка стоповыми битами, всегда имеющими значение «1». Интервалы времени между передаваемыми кадрами могут быть любыми. Приемник следит за уровнем сигнала в линии связи и фиксирует переход от «1» к «0» как новый стартовый бит и начало передачи. Следовательно, введение стартовых и стоповых разрядов в кодовую посылку позволяет осуществить синхронизацию приемника и передатчика и правильно интерпретировать сигналы данных.

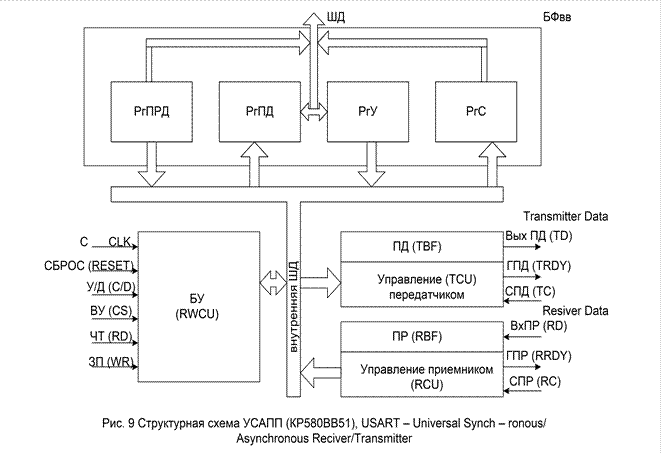

Устройство, преобразующее данные из параллельной формы в последовательную и обратно, называют универсальным синхронно-асинхронным приемопередатчиком (УСАПП). Такие устройства реализуют в виде БИС с программируемым режимами работы. УСАПП используют для реализации протокола передачи данных RS232.

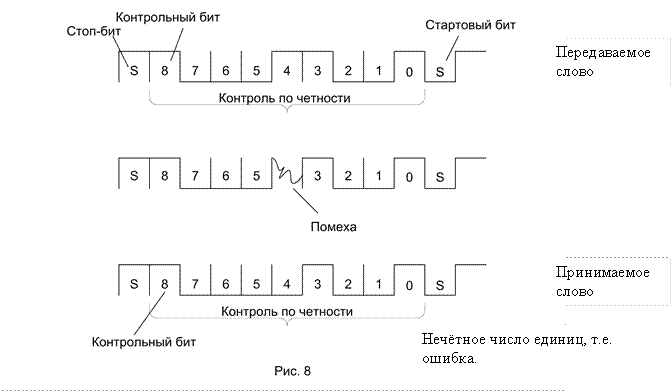

Большинство универсальных асинхронных приемопередатчиков (УАПП) осуществляют формирование и проверку бита четности. При данном виде проверки контрольному разряду придается значение логического «0» или «1» так, чтобы в передаваемом слове данных было четные количество единиц. Если применяется проверка на нечетность, то значение контрольного бита должно быть таким, чтобы общее количество единиц в слове было нечетным. Проверкой на четность удается выявить 50% возможных ошибок. Очевидно, будет обнаруживаться только нечетное число ошибочных битов. Если ошибка возникает сразу в двух битах, то обнаружить ее контролем на четность не удается. На рисунке 8 показано, как при последовательной передаче данных вследствие шумов может возникнуть ошибка, которую можно выявить контролем на четность. Шумы изменили 4 бит таким образом, что вместо «1» он принял значение «0». Сообщение, при передаче которого произошло такое искажение, будет

содержать ошибку.

С помощью УСАПП обмен данными может быть как полудуплексным (однонаправленным) так и дуплексным (двунаправленным). Дуплексный асинхронный режим применяется для связи с терминалами, компьютерами. Полудуплексный синхронный режим используют для связи с микросхемами ЦАП, АЦП, последовательными EEPROM.

В состав микропроцессорных комплектов (МПК) входит БИС УСАПП. Например, в МПК серии К580 входит БИС программируемого УСАПП КР580ВВ51. Рассмотрим структуру контроллера КР580ВВ51. Она изображена на рисунке 9.

В схеме можно выделить четыре основные части: передатчик ПД, приемник ПР, буфер ввода-вывода БФвв и блок управления БУ. БФвв включает в себя регистр передачи данных РгПРД, регистр команд управления РгУ, регистр принимаемых данных РгПД, регистр состояния схемы РгС.

Передатчик получает данные в параллельном коде от микро-ЭВМ, преобразует их в последовательный код, добавляет служебную информацию и выдает их на свой выход TD.

На вход ТС (синхронизация передатчика) подаются синхросигналы от приемника данных. При синхронном режиме данные выдаются на выход TD при каждом срезе (отрицательном фронте) сигнала на входе ТС. Таким образом, частота выдачи информации равна частоте синхросигнала ТС. Для асинхронного режима частота выдачи данных может программно устанавливаются в 16 или 64 раза меньше частоты синхросигнала на входе ТС. На выходе TRDY (готовность передатчика) будет уровень «1», если регистр передачи данных РгПРД пуст. Выход TRDY является выводом разряда готовности передатчика D0 регистра состояния схемы. Сигнал с выхода TRDY используется как сигнал на запрос прерывания МП.

Приемник получает последовательность символов по каналу RD (вход приемника), выделяет данные, преобразует их в параллельный код и записывает в регистр принимаемых данных РгПД. На вход RC (синхронизация приема) подаются тактовые сигналы от передатчика. При синхронном приеме данных, частота приема равна тактовой частоте на входе RC.

На выходе RRDY (флажок готовности приемника RRDY, готовность приемника) устанавливается уровень «1» если данные записаны в РгПД и готовы к вводу в микро-ЭВМ. Выход RRDY является выводом разряда готовности приемника D1 регистра состояния схемы. Сигнал RRDY используется для запроса прерывания МП.

Рассмотрим входные сигналы БУ.

CLK – вход синхросигнала. Обычно в качестве синхросигнала используются сигналы от ГТИ МП. Входные сигналы RD и WR определяют направление потока информации, передаваемой по ШД из МП в УСАПП и обратно. По стробу ЗП (WR) МП записывает в УСАПП данные или управляющую информацию. Строб ЧТ (RD) обеспечивает чтение данных или состояния из УСАПП. При отсутствии сигналов RD и WR обмена информацией с УСАПП не производится. Одновременная подача обоих сигналов запрещена. Логический уровень на входе C/D определяет вид информации при обмене, которая может быть либо словом управления/состояния (CD=1) либо байтом данных (C/D=0). Все операции по обмену информацией возможны только при низком уровне напряжения на линии выбора устройства ВУ=0 (CS=0).

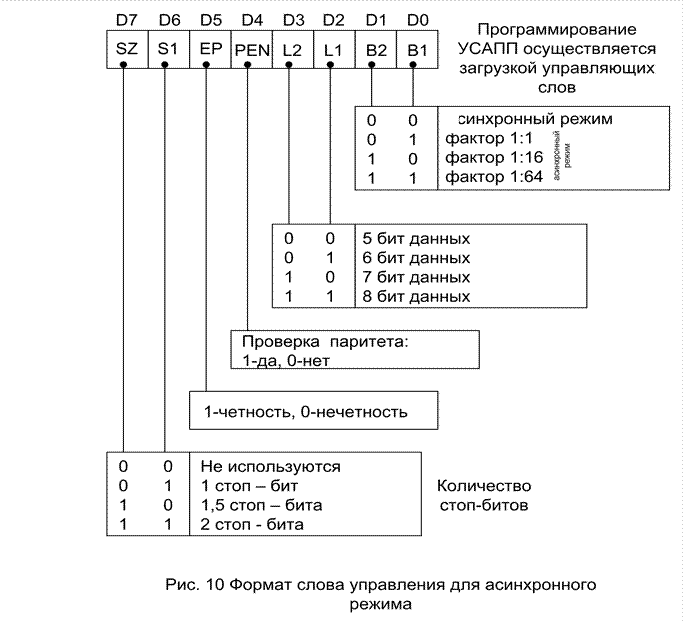

Перед началом работы УСАПП должен быть установлен в исходное состояние с помощью сигнала сброса «СБРОС» (RESET). Сразу после начальной установки в РгУ должно быть записано управляющее слово, которое задает режимы работы УСАПП. Формат слова управления показан ниже.

При синхронной передаче данные передаются по каналу связи в виде массива без служебной информации между кадрами. В начале массива передаются один или два синхросигнала. Количество синхросигналов задается схеме программно. Формат слова управления для синхронного режима показан ниже.

В результате записи управляющего слова в регистр команд управления РгУ схеме (БИС) сообщаются скорость приема-передачи данных, количество разрядов в каждом данном, число разрядов останова, режим работы (синхронный или асинхронный), наличие или отсутствие разряда четности каждого данного. При синхронном режиме указывается тип синхронизации (внутренняя, внешняя) и количество импульсов синхронизации. Контроль состояния УСАПП в процессе обмена данными МП производит с помощью считывания содержимого регистра состояния РгС.

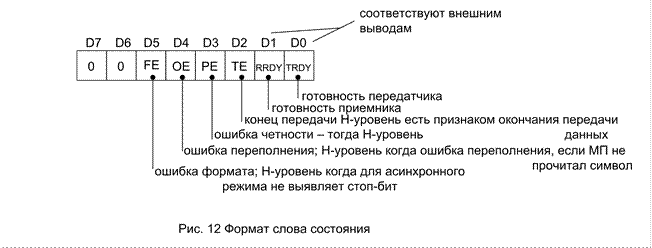

МП может контролировать состояние схемы УСАПП в процессе обмена данными. Для этой цели существует регистр состояния РгС, в разрядах которого отображаются сбои, ошибки и наличие сигналов на управляющих выводах схемы УСАПП. Формат слова состояния приведен на рисунке 12.

Логическая 1 в разряде TRDY означает, что буфер передатчика РгПРД пуст и в него может быть загружено следующее слово данных.

Логическая 1 в разряде RRDY означает, что в буфере приемника РгПД содержатся новые данные и они могут быть переданы в микро-ЭВМ.

1 в разряде РЕ свидетельствует о том, что УСАПП обнаружил ошибку, выявленную контролем по четности. Наличие ошибок при обмене информацией по каналам связи фиксируется в разрядах ошибок регистра состояния РгС.

1 в разряде ОЕ означает, что текущее слово данных не было передано в выходной буфер приемника РгПД до начала поступления следующего слова данных. При этом ранее записанные данные теряются.

1 в разряде FE указывает на то, что УСАПП не смог обнаружить стоп-бита, следующего за битами данных. Возможно приёмопередатчик пропустил фактический стартовый бит и в качестве такового принял один из битов слова данных.

Запись 1 в любой из разрядов ошибок РгС не нарушает динамику работы схемы УСАПП. Скорость передачи данных измеряют в бодах. Один бод равен одному биту в секунду. Поэтому скорость в бодах выражает, сколько бит в секунду может быть передано по каналу связи.

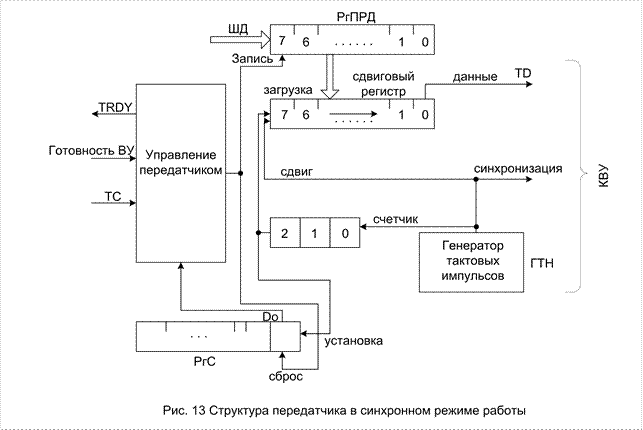

Структура передатчика ПД для синхронной передачи данных во ВУ по последовательной линии связи показана ниже.

Буферный регистр РгПРД служит для временного хранения байта данных до его загрузки в сдвиговый регистр. Синхронизация УСАПП не зависит от синхронизации МП. Следовательно, после того как МП поместил передаваемое слово данных в РгПРД, он не может знать, когда ему удастся загрузить в РгПРД следующее слово данных. МП должен ждать до тех пор, пока УСАПП не установит определенное значение бита состояния. Анализ бита состояния позволяет МП определить готовность УСАПП к загрузке в него нового слова.

Вместе с этой лекцией читают "4.3. Принципы и методы создания ИС".

Запись данных в РгПРД с ШД производится только при наличии единицы в разряде D0 РгС. Бит D0 передается в МП с выхода TRDY по одной из линий ШУ. МП формирует сигнал «Готовность ВУ», после чего следующий байт записывается в буфер РгПРД. При этом обнуляется разряд D0 РгС.

Преобразование данных из параллельного формата в последовательный и передача их на линию связи производится в сдвиговом регистре с помощью генератора тактовых импульсов (ГТИ) и двоичного трехразрядного счетчика импульсов. Последовательная линия связи подключается к выходу младшего разряда сдвигового регистра. По очерёдному тактовому импульсу ГТИ содержимое сдвигового регистра сдвигается на один разряд вправо и в линию связи выдается значение очередного разряда. Одновременно со сдвигом в ВУ передается по отдельной линии «синхронизация» тактовый импульс. Таким образом, каждый передаваемый по линии TD бит информации сопровождается синхронизирующим сигналом по линии «синхронизация». Количество переданных в линию тактовых сигналов, а, следовательно, и бит информации подсчитывается счетчиком тактовых импульсов. Как только содержимое счетчика становится равным 7, т.е. в линию переданы 8 бит данных, формируется управляющий сигнал «Загрузка», обеспечивающий запись в сдвиговый регистр очередного байта из буферного регистра РгПРД. Этим же сигналом устанавливается в «1» бит D0 регистра состояния РгС. Следующим импульсом ГТИ счетчик будет сброшен в «0» и начнется новый цикл выдачи восьми битов данных из сдвигового регистра в линию связи.

Синхронная последовательная передача отдельных битов должна производиться без перерыва и следующий байт данных должен быть загружен в буферный регистр за время, не превышающее времени передачи байта в последовательную линию связи. При записи байта данных в буфер обнуляется регистр состояния РгС. Нуль в Do указывает, что в линию связи передается байт данных из сдвигового регистра, а следующий передаваемый байт загружен в буферный регистр. Контроллер для последовательного синхронного приема данных из ВУ состоит из тех же компонентов, что и контроллер для синхронной передачи, за исключением ГТИ.

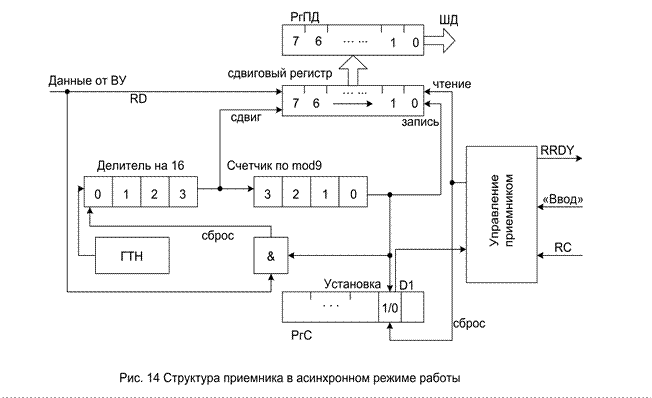

При асинхронном обмене данными общая синхронизация отсутствует. Структура приемника ПР при асинхронном приеме данных показана на рисунке 14. Уровень логической единицы поступает по линии RD в приемник при асинхронном режиме работы до начала передачи данных. Этот уровень запрещает работу делителя частоты ГТИ. Действительно, после приема предыдущего байта данных счетчик импульсов сдвига находится в нулевом состоянии и на логику & поступают два единичных сигнала: со счетчика сдвигов и из линии RD. На выходе элемента & вырабатывается сигнал сброса делителя частоты сигналов ГТИ, запрещающий формирование импульсов сдвига. Для работы УСАПП в асинхронном режиме требуется обеспечить время передачи 1 бит данных в 16 раз больше, чем период следования сигналов ГТИ.

В момент появления стартового бита на линии RD появится логический нуль и тем самым будет снят сигнал сброса с делителя частоты. Когда на счетчике по mod 16 накопится значение 16, он выдаст сигнал, поступающий на входы сдвигового регистра и счетчика импульсов сдвига. Следующий сдвиг произойдет после прохождения 16 тактовых импульсов. При приёме в сдвиговый регистр девятого бита кадра (8-мого информационного бита) из него выдвигается стартовый бит и в регистре сдвига будет размещён весь принятый байт информации. В этот может счетчик импульсов сдвига придет в нулевое состояние и на его выходе будет выработан единичный сигнал, по которому содержимое сдвигового регистра перепишется в буфер РгПД, в разряд D1 РгС запишется «1» и он будет информировать МП об окончании приема очередного байта. Логика & подготовится к выработке сигнала «сброс», который сформируется после прихода первого стопового бита. Получив сигнал готовности приемника RRDY, МП вырабатывает управляющий сигнал «Ввод», по которому производятся пересылка принятого байта данных из буфера РгПД в МП и сброс разряда D1 регистра состояния РгС.

Для простоты изложения на рисунке 14 не показаны схемы контроля стоповых бит и бита четности. В реальных УСАПП такие схемы имеются. Если УСАПП не принимает из линии связи нужного количества стоповых бит или вырабатывается сигнал ошибки паритета, то принятые в текущем кадре биты данных игнорируются и УСАПП ожидает поступления нового стартового бита. В современных микро-ЭВМ применяют универсальные контроллеры для последовательного ВВ, обеспечивающие как синхронный, так и асинхронный режим обмена данными с ВУ.