Интерфейс 8-разрядного МП

6.1 Интерфейс 8-разрядного МП

В качестве примера рассмотрим МП КР580ВМ80.

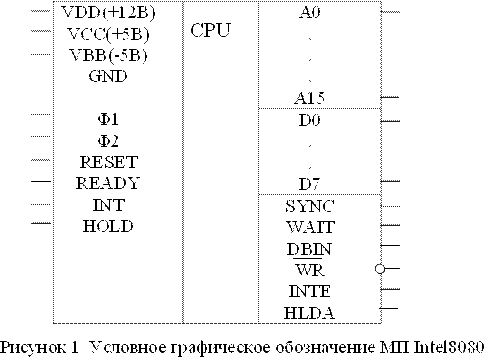

В состав интерфейса МП входят трехстабильная 16-разрядная шина адреса А15-А0, трехстабильная двунаправленная 8-разрядная шина данных D7 – D0, две линии двухфазной синхронизации φ1, φ2 и шина управления, состоящая из десяти линий, из которых четыре входных и шесть выходных.

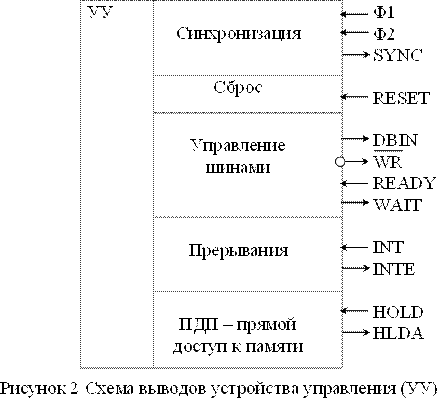

Реализация шины управления возлагается на устройство управления УУ входящее в состав МП.

|

Условное графическое обозначение МП КР580ВМ80 показано на рисунке 1.

|

Схема выводов устройства управления УУ показана на рисунке 2.

МП имеет 40 выводов. Каждая линия управления имеет свое функциональное назначение.

RESET (сброс) – вход, по которому осуществляется сброс содержимого программного счетчика РС, в результате чего выполнение программы начинается с нулевой ячейки памяти.

SYNC (синхронизация) – выход синхросигнала, указывающего начало каждого машинного цикла.

Рекомендуемые материалы

DBIN (DATA BUS INPUT – прием с шины данных) – выход сигнала, указывающего, что шина данных находится в режиме приема, т.е. МП ожидает поступления данных по шине.

(WRITE – запись) – выход сигнала, указывающего, что на шине данных находятся данные, поступающие из МП. Сигнал используется для управления вводом-выводом или для записи данных в память (строб вывода данных).

(WRITE – запись) – выход сигнала, указывающего, что на шине данных находятся данные, поступающие из МП. Сигнал используется для управления вводом-выводом или для записи данных в память (строб вывода данных).

READY (готовность) – вход сигнала, поступающего на МП от ВУ и указывающего о готовности данных к вводу, т.е., сигнал готовности периферийных модулей к обмену. Используется для синхронизации обмена между МП и внешними устройствами. При отсутствии сигнала после обращения к ВУ МП переходит в состояние ожидания.

WAIT (ожидание) – выход сигнала подтверждения что МП находится в состоянии ожидания.

INT (INTERRUPT – запрос прерывания) – входной сигнал от ВУ на прерывание работы МП и обслуживание ВУ. Запрос воспринимается в конце цикла выполнения текущей команды. Если триггер разрешения прерывания установлен, то МП переходит к выполнению программы прерывания.

INTE (INTERRUPT ENABLE – разрешение прерывания) – выходной сигнал, указывающий, что триггер разрешения прерывания установлен.

HOLD (захват шин) – вход сигнала запроса внешних адресной шины и шины данных. Запрос удовлетворяется после завершения МП текущего цикла. Если запрос удовлетворяется, то шины переводятся в состояние высокого сопротивления. Это позволяет ВУ получить управление обеими шинами, например, для ПДП.

HLDA (HOLD ACKNOWLEDGE – подтверждение захвата) – выход, сигнал на котором является признаком нахождения МП в режиме "ЗАХВАТ", т.е., МП передает управление шинами ВУ.

Команды в зависимости от типа требуют для своего выполнения от 1 до 5 машинных циклов (М1-М5). Каждый машинный цикл включает от 3 до 5 тактов (Т1-Т5).

Время, равное периоду следования синхроимпульсов называется тактом.

Цикл М1– это всегда цикл выборки команды. Длится он 4,5 тактов. Циклы М2-М5 содержат по 3 такта. Выполнение каждой команды начинается с цикла М1. Во время такта Т1 цикла М1 содержимое РС посылается на шину адреса, а на шине данных выставляется 8-разрядное слово состояния, характеризующее начинающийся машинный цикл. В такте Т2 анализируются сигналы на входах READY и HOLD. В такте Т3 цикла М1 по шине данных поступает код операции из памяти в регистр команд. В соответствии с этим кодом УУ генерирует необходимые управляющие сигналы. В тактах Т4 и Т5 в МП производятся внутренние пересылки и преобразования, поэтому МП в каждом машинном цикле переходит к тактам Т4 и Т5 только если это необходимо для выполнения текущей команды.

В последнем такте последнего машинного цикла выполнения каждой команды проверяется наличие запроса прерывания на входе INT, и если таковой имеется, то МП переходит к выполнению цикла М1 специального вида, в течение которого содержимое программного счетчика РС не увеличивается на 1, а выдается сигнал подтверждения прерывания на выход INTE. В этом случае прерывающее устройство посылает в МП адрес программы обработки прерывания.

Для эффективной работы микро-ЭВМ недостаточно описанных управляющих сигналов. Так, в данном наборе сигналов нельзя отличить циклы обращения к памяти от циклов ВВ. Расширение числа управляющих сигналов выполнено с помощью специального 8-разрядного слова состояния SW (Status Word), которое выдается МП на шину данных в первом такте Т1 каждого машинного цикла. В состав SW входят следующие сигналы.

D0 (INTA) – признак, выделяющий машинные циклы обслуживания системы прерываний;

D1 (WO) – запись/вывод. Свидетельствует о выдаче в цикле данных из МП;

D2 (STACK) – стек. Указывает на то, что адресная шина содержит адрес одной из ячеек ОЗУ, используемой в качестве стека;

Рекомендация для Вас - 4.5. Особенности защиты территорий.

D3 (HLTA) – признак останова по команде HALT;

D4 (OUT) – признак, указывающий на то, что адресная шина содержит адрес устройства вывода, а шина данных – выводимую информацию;

D5 (М1) – цикл М1. Обозначает первый машинный цикл каждой команды;

D6 (INP) – ввод, указывающий на то, что адресная шина содержит адрес устройства ввода, а шина данных – вводимую информацию;

D7 (MEMR) – чтение памяти. Выделяет циклы чтения данных из памяти.

Если сигналы управления используются для управления исполнением машинного цикла, то сигналы байта состояния SW кодируют тип машинного цикла. SW определяет вид информации и направление её движения через шину данных. Всего возможно 11 наборов сигналов SW, разбивающих множество машинных циклов на 11 типов. Так как информация о состоянии выдаётся из МП на шину данных в течении коротких интервалов времени, то необходимо её сохранять. Для хранения байта состояния и его дешифрации используется специальный системный контроллер, например БИС КР580ВК38.