Характеристика МП In 8086

Характеристика МП In 8086: разрядность, шина АД, адресация памяти и портов В/В. Функциональная структура МП In 8086. Сегментная адресация памяти. Программная модель МП In 8086. Обобщенный формат команды МП In 8086. Система команд МП In 8086.

Все регистры и двунаправленная мультиплексная шина AD адреса и данных 16-битные. Старшие 4 бита адреса мультиплексируются с сигналами состояния. Следовательно, длина физического адреса памяти составляет 20 бит, что обеспечивает адресное пространство 1М байт. Микропроцессор прямо адресует 256 портов ввода и 256 портов вывода и косвенно — 64К 8-битных портов ввода-вывода.

Функционально микропроцессор состоит из двух функционально автономных устройств: шинного интерфейса и операционного (исполнительного) устройства. Шинный интерфейс содержит секцию управления, 6-байтную очередь команд (эквивалент регистра команд), 4 сегментных регистра и программный счетчик (называемый указателем команд IP). Это устройство обеспечивает взаимодействие с остальными компонентами ЭВМ и нахождение в очереди команд достаточного числа байт.

Память представляет собой массив 1М байт, причем любые два смежных байта образуют слово, т. е. слово может начинаться с четного или нечетного адреса. В первом случае слово передается за один цикл шины, а во втором требуется два цикла шины, поэтому целесообразно размещать слова данных по четным адресам. Длина команд составляет 1—6 байт, и их размещение в памяти на производительность не влияет. Микропроцессор оперирует 16-битными операндами, поэтому все адресные объекты должны иметь длину 16 бит. Следовательно, для формирования 20-битных адресов необходим дополнительный механизм. Таким механизмом в микропроцессоре 8086 является сегментация памяти.

Можно считать, что память состоит из произвольного числа сегментов емкостью по 64К байт.

Микропроцессор управляет 4 сегментами (программы (кода), данных, стека и дополнительного сегмента данных), начальные адреса которых без младших нулей хранятся в 16-битных сегментных регистрах CS, DS SS и ES. Команды с обращением к памяти формируют 16-битный исполнительный (эффективный) адрес ЕА, представляющий собой смещение в сегменте. Физический 20-битный адрес памяти равен сумме содержимого ЕА и сегментного

Регистры общего назначения представлены 16-битными регистрами АХ, ВХ, СХ и DX, допускающими раздельную адресацию старших (Н) и младших (L) 8-битных регистров. Двойственный характер РОН обеспечивает простую обработку 8- и 16-битных данных. Остальные регистры можно адресовать только как 16-битные. В основном все РОН в арифметических и логических операциях используются одинаково. Но имеется значительное число команд, которые специализируют некоторые РОН, что отражено в их названиях. Регистр АХ выполняет функции аккумулятора, он является источником и получателем в операциях ввода-вывода, с ним связаны операции преобразования, десятичной коррекции, умножения и деления.

Регистр ВХ в некоторых командах участвует как регистр базового адреса.. Регистр СХ используется как счетчик в операциях сдвигов, командах зацикливания и в операциях с цепочками байт и слов. DX неявно адресуется в операциях умножения и деления, а также содержит адрес портов ввода или вывода в режиме косвенной адресации.

Группа указательных и индексных регистров включает в себя 16-битные регистры SP, BP, SI и DI. Они обычно содержат внутрисегментные смещения и обеспечивают косвенную адресацию и динамическое вычисление исполнительных адресов. Гибкость таких вычислений достигается тем, что рассматриваемые регистры могут участвовать в арифметических и логических операциях как регистры общего назначения. Регистры SP (указатель стека) и BP (указатель базы) адресуют данные в текущем сегменте стека, а не в сегменте данных. Поэтому, если сегмент специально не определен, смещения в SP и BP относятся к текущему сегменту стека. Индексные регистры SI (источника) и DI (получателя) содержат смещения, которые обычно относятся к текущему сегменту данных.

Рекомендуемые материалы

Четыре 16-битных сегментных регистра CS, DS, SS и ES используются для задания текущих сегментов по 64К байт, адресуемых при выполнении программы. Каждый регистр адресует конкретный текущий сегмент, что отражено в их названиях: код, данные, стек, дополнительные данные.

Основное назначение сегментных регистров — динамическое перемещение программ в памяти, которое необходимо в мультипрограммной среде. По существу, для такого перемещения достаточно модифицировать содержимое сегментного регистра CS при условии, что программа сама не изменяет его содержимого. Кроме того, модифицируя содержимое DS, прикладная программа может манипулировать данными такого объема, который превышает емкость сегмента.

16-битный регистр состояния (регистр флажков) FLAGS разделен на две половины, младшая из которых FLAGSL полностью соответствует регистру флажков микропроцессора 8080. В старшей половине введены 4 новых флажка: OF — арифметического переполнения; DF — направления (определяет направление сканирования массива в операциях с цепочками); IF — прерывания (выполняет функцию маскирования внешних прерываний);

TF — прослеживания (обеспечивает выполнение программы по командам).

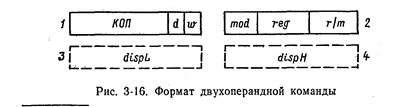

Общий формат двухоперандной команды, когда вторым операндом является регистр, показан на рис. 3-16. Первый байт содержит код операции и два однобитных поля: d (направление) и w (слово). Поле d определяет направление передачи, относящееся ко второму операнду — регистру, идентифицируемому 3-битным полем reg второго байта команды. Если d = 1, то направление передачи—в регистр, а если d=0, то направление—из регистра. Поле w определяет тип операнда: слово (w == 1) или байт (w = 0).

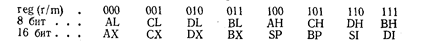

Второй байт команды, называемый постбайтом, имеет три поля. Поле reg определяет второй операнд, обязательно находящийся в регистре. В этом поле кодируются следующие 8- или 16-битные регистры:

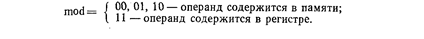

Поле режима mod определяет используемый режим адресации. В частности, оно влияет на интерпретацию содержимого поля r/т (регистр/память) при нахождении первого операнда. Поле mod имеет следующий общий смысл

Когда mod =11, поле r/m определяет 8- или 16-битный регистр в соответствии с приведенным выше кодированием.

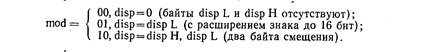

Если mod=00(01,10), это поле определяет, каким образом используется необязательное смещение disp:

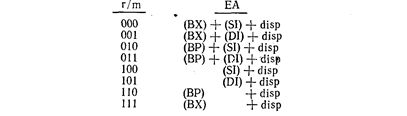

В этом же случае поле r/m определяет, как формируется исполнительный адрес ЕА команды:

Приведенные правила имеют только одно исключение:

если mod = 00 и r/m = 110, то ЕА = disp H, disp L. Такой способ формирования ЕА называется прямой адресацией, т. е. адрес содержится в команде.

. Всего получается 24 режима адресации: 3 способа интерпретации поля mod и 8 способов интерпретации поля r/m.

Система команд насчитывает 113 базовых команд, объединяемых в следующие группы:

Команды передачи данных. Команды данной группы подразделяются на четыре разновидности:

а) команды передачи данных между регистрами и памятью, включения в стек и извлечения из стека (адресуемого SP), а также команда обмена содержимым источника и приемника;

б) команды ввода, вывода, табличного преобразования;

Люди также интересуются этой лекцией: 4. Фазы жизненного цикла.

в) команды загрузки исполнительного адреса в регистры общего назначения, а также загрузки 4-байтного адресного объекта в регистры-указатели (начальный адрес сегмента и смещение в сегменте);

г) команды передачи содержимого регистра флажков (запоминание в памяти и загрузка из памяти регистра FLAGSL, включение в стек и извлечение из стека всего регистра FLAGS).

Арифметические команды. Микропроцессор имеет команды сложения, вычитания, умножения и деления двоичных знаковых и беззнаковых чисел. Логические команды и команды сдвига. В эту группу входят поразрядные операции инверсии, конъюнкции, дизъюнкции и исключающего ИЛИ

Команды передачи управления (переходы, вызовы, возвраты) имеют две разновидности: внутрисегментные («близкие»), целевой адрес которых, загружаемый в указатель команд IP, находится в текущем сегменте кода, и междусегментные («далекие»), Имеются 4 команды управления циклами, которые рассчитаны на передачу числа повторений цикла в регистре СХ (счетчик).

Команды обработки цепочек данных. Команды этой группы манипулируют цепочками данных, т. е. последовательностями байт или слов в памяти.

Микропроцессор имеет двухуровневую систему прерываний: Вход NMI немаскируемого прерывания имеет больший приоритет, чем вход INTR маскируемых прерываний.