Обобщенные характеристики МП 8080

19. Обобщенные характеристики МП 8080, методы адресации, особенности структуры. Организация в МП In 8080: - прерываний; - захвата шин; - асинхронного взаимодействия с памятью. Мультиплексирование ШД и 10 типов машинных циклов. Формирование системных управляющих сигналов. Система команд In 8080.

Организация МП КР580 (аналог Intel 8080). Данный МП содержит примерно 5000 элементов и реализован в 40-выводном корпусе. Число базовых команд МП КР580 составляет 78, время выполнения команд для тактовой частоты 2 МГц лежит в диапазоне 2—9 мкс. Команды МП могут быть одно-, двух- и трехбайтными. Двух- и трехбайтные команды хранятся в соседних ячейках памяти. МП КР580 имеет четыре режима адресации:

1. Прямая адресация. В этом режиме второй и третий байты команды содержат исполнительный адрес команды, причем во втором байте — младшие разряды, а в третьем — старшие.

2. Регистровая адресация — для обращения к внутренним регистрам МП.

3. Непосредственная адресация, при которой в команде указывается 8- или 16-битный операнд.

4. Косвенная регистровая адресация.

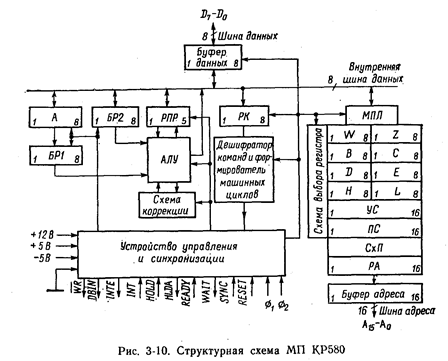

Структурная схема МП КР580 приведена на рис. 3-10. функциональное назначение выводов МП следующее:

A15—ао —шина адреса с тремя состояниями, обеспечивает адресацию памяти емкостью до 64К байт, адресацию 256 портов ввода и 256 портов вывода информации;

Рекомендуемые материалы

D7—Do — двунаправленная шина данных с тремя состояниями, обеспечивает обмен информацией между МП, памятью и периферийными устройствами;

DBIN — выходной сигнал приема, указывает памяти и периферийным устройствам, что шина данных находится в режиме приема информации в МП;

WR — выходной сигнал выдачи, используется для управления выдачей информации из МП в память и периферийные устройства, активным является сигнал WR=0;

INT — входной сигнал прерывания, воспринимаемый МП после выполнения текущей команды или в режиме останова; прерывание не воспринимается МП, если он находится в режиме захвата или в режиме запрещенных прерываний, что обеспечивается установкой триггера разрешения прерываний в состояние 0 командой DI;

INTE — выходной сигнал разрешения прерываний, индицирует состояние триггера разрешения прерывания;

данный триггер сбрасывается в 0 после команды DI, a также после приема сигнала прерывания INT или сигнала сброса RESET;

HOLD — входной сигнал захвата, переводит МП в состояние захвата после завершения обмена данными между МП, памятью или периферийными устройствами в текущем машинном цикле; после захвата МП шины данных и адреса переходят в состояние высокого выходного сопротивления;

HLDA — выходной сигнал подтверждения состояния захвата МП;

READY — входной сигнал готовности, информирует МП, что данные из внешнего источника переданы на шину данных, синхронизирует работу МП с более медленнодействующими памятью или периферийными устройствами; при нулевом значении этого сигнала МП переходит в состояние ожидания Tw;

WAIT — выходной сигнал ожидания, подтверждающий, что МП находится в состоянии ожидания Tw;

RESET — входной сигнал сброса, обеспечивает установку в состояние 0 регистра команд, программного счетчика, триггеров разрешения прерывания и подтверждения захвата; при этом состояние остальных регистров не изменяется;

SYNC — выходной сигнал синхронизации, определяет начало машинного цикла;

01, 02—тактовые сигналы.

МП КР580 содержит шесть 8-битных РОН, которые обозначаются В, С, D, Е, Н, L и могут объединяться в 16-битные пары В и С; D и Е; Н и L. Регистры W, Z являются программно-недоступными и выполняют вспомогательные функции, например используются для временного хранения адресов. Содержимое программного счетчика (ПС) автоматически увеличивается на 1 при выборке каждого байта команды, при этом первый байт, определяющий код операции, всегда передается в регистр команд (РК). Указатель стека (УС) хранит адрес последней занятой ячейки в стековой памяти. Содержимое УС уменьшается перед записью кода в стек и увеличивается после чтения.

Обмен данными внутри МП осуществляется по внутренней 8-битной шине данных через двунаправленный мультиплексор (МПЛ). Арифметические операции выполняются в дополнительных кодах. Аккумулятор А является источником одного из операндов при выполнении бинарных операций и приемником результата. Буферные регистры БР1 и БР2 выполняют вспомогательные функции.

АЛУ после выполнения команды формирует признаки результатов, которые фиксируются в 5-битном регистре признаков РПР. АЛУ формирует следующие признаки: нулевого результата Z, знака S, переноса С из старшего бита, переноса АС из третьего бита аккумулятора, четности Р. Признаки АС и С при выполнении операций над числами в десятичной системе счисления используются для коррекции результата.

В МП КР580 имеется десять типов машинных циклов, которые могут быть при выполнении команды: выборка байта команды, чтение из памяти, запись в память, чтение из стековой памяти, запись в стековую память, ввод, вывод, обработка прерывания, останов, обработка прерывания при останове. При этом первым машинным циклом всегда является выборка команды.

INTA (Do) — признак подтверждения прерывания

STACK (D2) — признак указывает, что на шину адреса передается адрес из указателя стека, используемый для адресации области стековой памяти;

HLTA (D3) — признак подтверждает выполнение команды останова HLT;

OUT(D4) — признак вывода, указывает, что шина адреса содержит адрес порта вывода, а шина данных будет содержать данные при сигнале WR == 0;

Ml (D5) — признак указывает, что МП находится в цикле выборки первого байта команды;

INP(D6) — признак ввода, указывает, что шина адреса содержит адрес порта ввода и входные данные передаются по шине данных при сигнале DBIN = 1;

MEMR(D7) — признак указывает, что шина данных будет использована для приема данных из памяти.

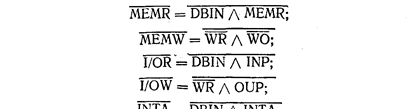

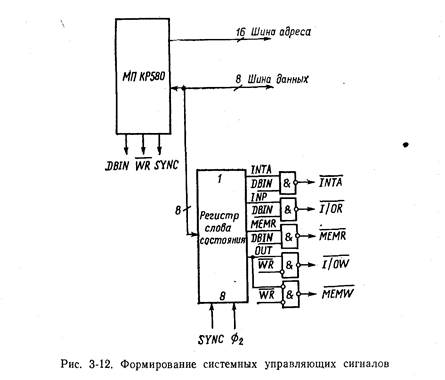

формирование системных управляющих сигналов. Набор управляющих сигналов, таких как чтение из памяти (MEMR), запись в память (MEMW), ввод информации (I/OR), вывод информации (I/OW), подтверждение прерывания (INTA] обеспечивает прием и передачу кодов между МП, памятью и периферийными устройствами в определенные интервалы времени в соответствии с диаграммой переходов машинного цикла. Данные сигналы непосредственно не формируются микропроцессором КР580, для их формирования используются сигналы приема (DBIN) и записи (WR) из МП и необходимые признаки из слова состояния:

Обработке запросов прерывания. Устройство, обслуживаемое МП в режиме прерывания, инициирует прерывание путем формирования на входе INT МП сигнала 1, который может возникнуть в любом машинном цикле команды. Однако, как видно из диаграммы переходов, текущая команда должна завершиться и только после этого МП переходит к машинному циклу подтверждения прерывания, который имеет ряд отличий от цикла выборки команды. Во-первых, в слове состояния дополнительно к признаку машинного цикла выборки команды Ml содержится признак INTA, подтверждающий, что сигнал прерывания воспринят МП. Во-вторых, ПС не увеличивается на 1 в данном цикле, так как, увеличенный после выборки предыдущей команды, он должен быть запомнен в стековой памяти без изменения. В-третьих, вместо команды из программной памяти на шину данных передается код, представляющий собой однобайтную команду RST. Команда RST обеспечивает запоминание содержимого программного счетчика в стеке, и в ПС формируется один из восьми начальных адресов, в которых хранятся первые команды подпрограмм обслуживания прерываний.

Если область памяти в 8 байт недостаточна для размещения подпрограммы, что, как правило, имеет место, то путем использования команд перехода ее можно расширить. Таким образом, первые 64 ячейки памяти (ООООН — 003FH) зарезервированы для подпрограмм обработки прерываний.

Рекомендация для Вас - 15 - Основные структурные области коры.

Система команд МП КР580. Все множество команд данного МП можно подразделить на следующие 5 групп:

1. Команды пересылки кодов, обеспечивающие пересылку данных между регистрами или памятью и регистрами.

2. Арифметические команды, обеспечивающие выполнение операций сложения и вычитания, изменения кодов на 1. Один операнд для бинарных операций хранится в аккумуляторе А, другой — в регистре или ячейке памяти, а результат помещается в аккумулятор. Умножение и деление, выполняются программным путем с использованием подпрограмм.

3. Логические команды реализуют операции логического сложения и умножения, исключающего ИЛИ, инвертирования, левого и правого сдвигов и некоторые другие. Исходные операнды хранятся в регистрах или ячейках памяти, а результат помещается в аккумулятор.

4. Команды передачи управления, в число которых входят команды безусловной и условной передачи управления, обращения и выхода из подпрограмм.

5. Команды ввода и вывода информации, обращения к стековой памяти.