Параллельные порты ввода и вывода

ПАРАЛЛЕЛЬНЫЕ ПОРТЫ ВВОДА/ВЫВОДА

Микроконтроллеры РIС16F87Х имеет в своем составе от 3-х до 5-ти параллельных двунаправленных портов ввода/вывода: ‘873/876 – A,B,C, а ‘874/877 – A,B,C,D,E.

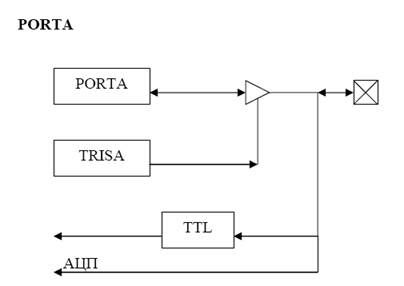

• Порт А - 6-разрядный. Может быть настроен как аналоговые входы АЦП источника опорного напряжения, выбора -СS в режиме SРI. Вывод RА4 - выход с открытым стоком (основная функция).

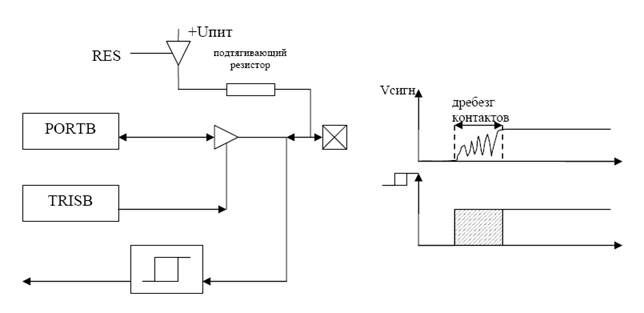

• Порт В - 8-разрядный. Имеет программно подтягивающие резисторы pull-Up. Может быть настроен как входы внешних прерываний, внутрисхемного программирования и эмуляции.

• Порт С - 8-разрядный. Альтернативные функции: ТМR1, ССР2, ССР1, SPI, I2С, USART.

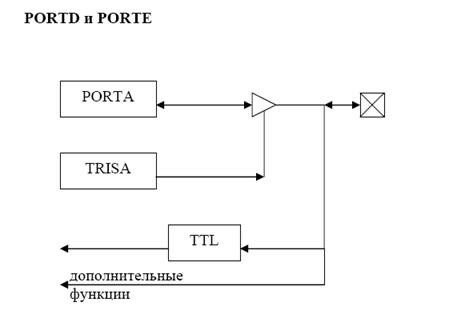

• Порт D - 8-разрядный. Альтернативная функция: РSР (нет у ‘873/6).

• Порт Е - 3-разрядный. Альтернативная функция: управление РSР (-WR, -RD, -CS).

Каждый вывод порта может индивидуально настраиваться на ввод или вывод установкой соответствующего бита в регистре направления данных ТRISх, где х - имя порта А...Е. Если бит имеет значение 1. то соответствующая линия порта настроена на ввод, если 0 - на вывод. Для вывода/чтения бита достаточно записать, считать соответствую шее значение регистра РОRТх.

Многие линии портов совмещены с периферийными устройствами, такими как АЦП, ШИМ, SSР, USART и для нормальной работы периферии линии должны находится в соответствующем состоянии. Так для обеспечения преобразования аналогового сигнала с помощью АЦП соответствующие линии должны находится в режиме ввода, а для работы модуля ШИМ в режиме вывода.

Рекомендуемые материалы

Структурные схемы портов

ТТL буфер для входящих сигналов.

РОRТА - цифровое значение входного/выходного сигнала.

Бесплатная лекция: "2.1. Основные принципы инженерной защиты населения" также доступна.

ТRISА - разрешает или запрещает биты на вывод из порта

РОRТB и РОRТC

Триггер Шмита - модуль, устраняющий дребезг контактов.

Программный триггер Шмита: обеспечивает задержку на входе при обработке клавиатуры. При получении первого импульса на время t отключает прием сигнала.