Лекция 14. Система проектирования MAX-PLUS II

Лекция 14 – Система проектирования MAX+PLUS II для ПЛИС фирмы Altera

Общие сведения. Лекции 14-17 посвящены системе MAX+PLUS II для ПЛИС фирмы Altera. Все пакеты работают на платформе IBM PC. Для нормальной инсталляции и работы САПР MAX+PLUS II (версия 9.4 вышла в декабре 1999 года) необходима IBM PC-совместимая ЭВМ с процессором не хуже Pentium, объёмом ОЗУ не хуже 16 Мб и свободным местом на жёстком диске порядка 150-400 Мб.

Каталоги системы MAX+PLUS II. Во время инсталляции системы MAX+PLUS II создаются два каталога: maxplus2 и max2work. Каталог maxplus2 содержит системное ПО и файлы данных, и разбит на подкаталоги, перечисленные в таблице 14.1. Каталог max2work содержит файлы обучающей программы и примеры, и подразделяется на подкаталоги, описанные в таблице 14.2.

Таблица 14.1 – Структура системного каталога maxplus2

| Подкаталог | Описание |

| .drivers | содержит драйверы устройств только для инсталляции на платформе WINDOWSNT |

| .edс | Рекомендуемые материалыЛР № 1 - Определение номенклатуры средств автоматизации проектирования и управления на этапах жизненного цикла FREE Методы решения задач оптимального проектирования ВС (Силаева Т.А.) FREE Методичка для лабораторной работы № 14 по автоматизации FREE Методичка для лабораторной работы № 14 Построение модели изделия в PDM системе Отчет по лабораторной работе №1 "Построение модели изделия в PDM системе" содержит командные файлы (.edc), которые генерируют выходные файлы по заказу пользователя для заданных условий тестирования |

| .lmf | содержит файлы макробиблиотек, которые устанавливают соответствие между логическими функциями пользователя и эквивалентными логическими функциями MAX+PLUS II |

| .max2inc | содержит include-файлы (файлы «заголовков») с прототипами функций для макрофункций |

| .max2libedif | содержит примитивы и макрофункции, используемые для пользовательских интерфейсов EDIF |

| .max2libme-ga_ipm | содержит мегафункции, в том числе библиотеку функций параметризованных модулей |

| .max2libmf | содержит макрофункции пользовательские и устаревшие (74-series) |

| .max2libprim | содержит поставляемые фирмой Altera примитивы |

| .vhdlnnaltera | содержит библиотеку с программным пакетом maxplus2 |

| vhdlnnieee | содержит библиотеку ieee пакетов VHDL |

| .vhdlnnstd | содержит библиотеку std с пакетами стандартов и средств ввода/вывода текста, описанными в справочнике по стандартам IEEE |

Таблица 14.2 – Структура рабочего каталога max2work

| Подкаталог | Описание |

| .ahdl | содержит файлы примеров, иллюстрирующих тему «Как использовать язык AHDL” (Hou to Use AHDL) в электронном справочнике (MAX+PLUS II Help) и в руководстве MAX+PLUS II AHDL |

| .chiptrip | содержит все файлы обучающего проекта chiptrip, описанного в руководстве |

| .edif | содержит все файлы примеров, иллюстрирующих особенности EDIF в электронном справочнике |

| .tutorial | содержит информационный файл read.me обучающего проекта chiptrip |

Продолжение таблицы 14.2

| Подкаталог | Описание |

| .vhdl | содержит файлы примеров, иллюстрирующих тему «Как использовать язык VHDL» в электронном справочнике и в руководстве |

| .verilog | содержит файлы примеров, иллюстрирующих тему «Как использовать язык верификационного протокола HDL» в электронном справочнике и в руководстве |

Название системы MAX+PLUS II является аббревиатурой от Multiple Array MatriX Programmable Logic User System (Пользовательская система программирования логики упорядочных структур). Система MAX+PLUS II разработана фирмой Altera и обеспечивает многоплатформенную архитектурно-независимую среду создания дизайна, легко приспосабливаемую для конкретных требований пользователя. Система MAX+PLUS II имеет средства удобного ввода дизайна, быстрого прогона и непосредственного программирования устройства.

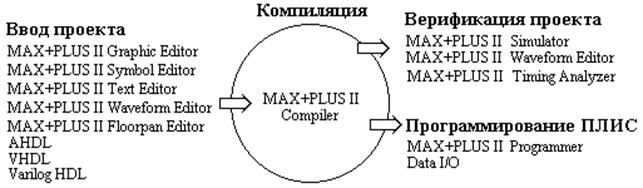

Состав ПО системы MAX+PLUS II. Представленный на рисунке 14.1 состав ПО системы MAX+PLUS II является полным комплектом, обеспечивающих создание логических дизайнов для устройств фирмы Altera с программируемой логикой, в том числе семейства устройства Classic, MAX 5000, MAX 7000, MAX 9000, FLEX 6000, FLEX 8000, и FLEX 10K. Информация о других поддерживаемых семействах устройств фирмы Altera приведена в файле read.me в системе MAX+PLUS II.

Рисунок 14.1 – Среда проектирования в системе MAX+PLUS II

Система MAX+PLUS II предлагает полный спектр возможностей логического дизайна:

1. разнообразные средства описания проектов с иерархической структурой,

2. мощный логический синтез,

3. компиляцию с заданными временными параметрами,

4. разделение на части,

5. функциональное и временное тестирование (симуляцию),

6. тестирование нескольких связанных устройств,

7. анализ временных параметров системы,

8. автоматическую локализацию ошибок,

9. программирование,

10. верификация устройств.

В системе MAX+PLUS II можно как читать, так и записывать файлы на

языке AHDL и файлы трассировки в формате EDIF, файлы на языках описания аппаратуры Verilog HDL и VHDL, а также схемные файлы OrCAD. Кроме того, система MAX+PLUS II читает файлы трассировки, созданные с помощью ПО Xilinx, и записывает файлы задержек в формате SDF для удобства взаимодействия с пакетами, работающими с другими промышленными стандартами.

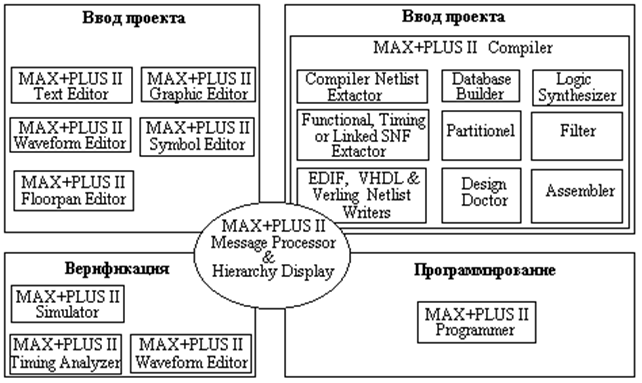

Приложения в системе MAX+PLUS II. Система предлагает пользователю богатый графический интерфейс, дополненный иллюстрированной оперативной справочной системой. В полную систему MAX+PLUS II входят несколько внедрённых в систему приложений (см. рисунок 14.2). Совокупность иерархически связанных файлов проекта Design file называется проектом (project).

Рисунок 14.2 – Приложения в системе MAX+PLUS II

Возможно описание проекта Design Entry в виде файла на языке описания аппаратуры, созданного либо во внешнем редакторе, либо в текстовом редакторе MAX+PLUS II (Text Editor), в виде схемы электрической принципиальной c помощью графического редактора Graphic Editor, в виде временной диаграммы, созданной в сигнальном редакторе Waveform Editor. Для удобства работы со сложными иерархическими проектами каждому поддизайну может быть сопоставлен символ, редактирование которого производится с помощью графического редактора Symbol Editor. Размещение узлов по логическим блокам и выводам ПЛИС выполняют с помощью поуровневого планировщика Floorplan Editor.

Верификация проекта (Project verification) выполняется с помощью симулятора (simulator), результаты работы которого удобно просмотреть в сигнальном редакторе Waveform Editor. Тестовые воздействия создаются также в сигнальном редакторе.

Компиляция проекта, включая извлечение списка соединений (Netlist Extractor), построение базы данных проекта (Data Base Builder), логический синтез (logic synthesis), извлечение временных, функциональных параметров проекта (SNF Extractor), разбиение на части (Partioner), трассировка (Filter) и формирование файла программирования или загрузки (Assembler), выполняются с помощью компилятора системы (Compiler). Непосредственно программирование или загрузка конфигурации устройств с использованием соответствующего аппаратного обеспечения выполняется с использованием модуля программатора (Programmer).

Многие команды – такие, как открытие файлов, ввод назначений устройств, выводов и логических элементов, компиляция текущего проекта – похожи для многих приложений системы MAX+PLUS II. Редакторы для разработки проекта (графический, текстовый и сигнальный) имеют много общего со вспомогательными редакторами (поуровневого планирования и символьный). Каждый редактор разработки проекта позволяет выполнять похожие задачи (например, поиск сигнала или символа) похожим способом. Можно легко комбинировать разные типы файлов проекта в иерархическом проекте, выбирая для каждого функционального блока тот формат описания проекта, который больше подходит. Поставляемая фирмой Altera большая библиотека мега- и макрофункций, в том числе функции из библиотеки параметризованных моделей (LPM), обеспечивает широкие возможности ввода дизайна.

Можно одновременно работать с разными приложениями MAX+PLUS II. Например, можно открыть несколько файлов проекта и переносить информацию из одного в другой в процессе компиляции или тестирования другого проекта. Или, например, просматривать всё дерево проекта и в окне просмотра перемещаться с одного уровня на другой, а в окне редактора будет появляться выбранный вами файл, причём вызывается автоматически соответствующий редактор для каждого файла.

Разработка проекта в системе MAX+PLUS II. Этапы проектирования. Процедура разработки нового проекта состоит из следующих этапов:

· создание нового файла (design file) проекта или иерархической структуры нескольких файлов проекта с использованием различных редакторов;

· задание имени файла проекта верхнего уровня (Top of hierarchy);

· назначение семейства ПЛИС для реализации проекта;

· открытие окна компилятора (Compiler) и его запуск. Можно подключить модуль извлечения временных задержек Timing SNF Extractor для создания файла разводки, используемого при тестировании временных параметров;

· при успешной компиляции возможно тестирование и временной анализ;

· программирование выполняется путём загрузки модуля программатора (Programmer) с последующей вставкой устройства в программирующий адаптер программатора MPU (Master Programming Unit) или с помощью подключения устройства Master Blaster или кабеля загрузки к устройству, программируемому в системе:

· выбор кнопки Program для программирования устройств с памятью типа EPROM или EEPROM либо выбор кнопки Configure для загрузки конфигурации устройства с памятью типа SRAM.

MAX+PLUS II запускается двумя способами: щелкнув дважды левой кнопкой мыши на пиктограмме MAX+PLUS II или набрав maxplus2 в командной строке. При этом автоматически открывается Главное окно, охватывающее все приложения системы. В верхней части окна отображается имя проекта и те-

|

Рисунок 14.3 – Окно меню MAX+PLUS II | кущего файла. Затем следует строка меню, под ней панель основных инструментов системы, обеспечивающая быстрый вызов её компонентов. В нижней части экрана располагается строка подсказки. Вызов компонентов системы удобно производить через окно меню MAX+PLUS II, представленном на рисунке 14.3. Программное обеспечение (ПО) системы MAX+PLUS II содержит 11 приложений и главную управляющую оболочку. Различные приложения могут быть активизированы мгновенно, что позволяет пользователю переключаться между ними щелчком мыши или с помощью команд меню. Приложения системы MAX+PLUS II. В таблице 14.3 приведено описание приложений. Следует понять разницу между файлами проекта и вспомогательными файлами. Файл проекта – это графический, текстовой |

или сигнальный файл. Этот файл содержит логику для проекта MAX+PLUS II и обрабатывается компилятором. Вспомогательные файлы – это файлы, связанные с проектом MAX+PLUS II, но не являющиеся частью иерархического дерева проекта. Примерами вспомогательных файлов являются файлы назначений и конфигурации, символьные файлы, файлы отчётов и файлы тестовых векторов.

Проект состоит из всех файлов иерархической структуры дизайна, в том числе вспомогательных и выходных файлов. В системе MAX+PLUS II легко доступны все инструменты для создания логического проекта. Разработка проекта ускоряется за счёт имеющихся стандартных логических функций, в том числе примитивов, мегафункций, библиотеки параметризированных модулей LPM. Крайне вредно использовать устаревшие библиотеки и переносить на ПЛИС схемотехнику стандартных ТТЛ серий. Следует разработать проект именно под архитектуру ПЛИС для получения более или менее разумных результатов.

Таблица 14.3 – Приложения системы MAX+PLUS II

| Прил-ние | Выполняемая функция |

| Hierarchy Display | Обзор иерархии - отображает иерархическую структуру файлов в виде дерева с ветвями |

| Graphic Editor | Графический редактор –разрабатывает схемный логический дизайн. Примитивы, мегафункции фирмы Altera используются в качестве основных блоков |

| Symbol Editor | Символьный редактор –редактирует существующие символы и создаёт новые |

| Text Editor | Текстовый редактор –создаёт и редактирует текстовые файлы, написанные на языках описания AHDL, VHDL и Verilog HDL |

| Waveform Editor | Сигнальный редактор – выполняет двойную функцию; это инструмент для разработки дизайна и инструмент для ввода тестовых сигналов и наблюдения результатов тестирования. |

| Floorplan Editor | Поуровневый планировщик –графическими средствами даёт назначения выводам устройства и ресурсам логических элементов и блоков. |

| Compiler | Компилятор – обрабатывает логические проекты, разработанные для семейств устройств Altera |

| Simulator | Симулятор – тестирует логические операции и внутреннюю синхронизацию проектируемой логической схемы. Возможны три режима тестирования: функциональное, временное и тестирование нескольких соединённых между собой устройств |

| Timing Analyzer | Анализатор временных параметров – анализирует работу проектируемой логической цепи после того, как она была синтезирована и оптимизирована компилятором, позволяет оценить возникающие задержки |

| Program-mer | Программатор –программирует, конфигурирует, проводит верификацию и испытывает устройства фирмы Altera |

| Message Processor | Генератор сообщений – выдаёт на экран сообщения об ошибках, предупреждающие и информационные сообщения о состоянии проекта |

Схемные файлы проекта создаются в графическом редакторе MAX+PLUS II. Можно также открыть, редактировать и сохранять схемы, созданные схемным редактором OrCAD.

Проекты на языках AHDL, VHDL и Verilog HDL создаются в текстовом редакторе MAX+PLUS II или любом другом текстовом редакторе.

|

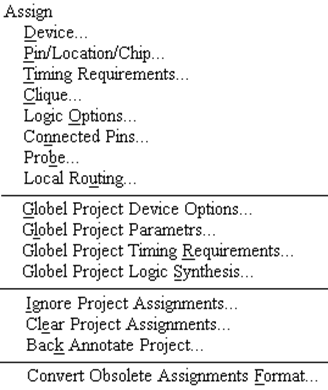

Рисунок 14.4 – Меню назначений проекта Assign | Сигнальные проекты создаются в сигнальном редакторе MAX+PLUS II. Файлы формата Xilinx, разработанные другими стандартными инструментами системы EDA, могут быть импортированы в среду MAX+PLUS II. Назначения параметров проекта. Во всех приложениях MAX+ PLUS II есть возможность с помощью команд из меню Assign (Назначить) вводить, редактировать и удалять типы назначений ресурсов, устройств и параметров, которые управляют компиляцией проекта, в том числе логическим синтезом, разделением на части и подгонкой. На рисунке 14.4 представлены команды меню Assign. Следующие функции являются |

общими для всех приложений MAX+PLUS II: назначения устройства, ресурсов и зондов; сохранение предыдущей версии; глобальные опции устройства в проекте; глобальные параметры проекта; глобальные требования к временным параметрам проекта; глобальный логический синтез проекта.

Ресурс является частью устройства фирмы Altera, как, например, контакт или логический элемент, который выполняет конкретные, определённое пользователем задание. Управление компиляцией проекта и его временными параметрами осуществляется с помощью различных назначений (Assign). Существуют следующие типы назначений.

Clique assignment (назначение клики) задаёт, какие логические функции должны оставаться вместе. Группировка логических функций в клики гарантирует, что они реализуются в одном и том же блоке логической структуры, блоке ячеек памяти, в одном ряду или устройстве. Узлы, объединённые в клики, при компиляции будут размещаться в пределах одного ЛБ.

Chip assignment (назначение чипа) задаёт, какие логические функции должны быть реализованы в одном и том же устройстве в случае разделения проекта на части (на несколько устройств).

Pin assignment (назначение вывода) назначает вход или выход одной логической функции, такой, как примитив или мегафункция, конкретному контакту или вертикальному (горизонтальному) ряду выводу ПЛИС.

Location assignment (назначение ячейки) задаёт расположение логической функции (узла). Назначения вывода, чипа и ячейки выполняется с помощью команды Assign/Pin/Location/Chip.. В поле данного окна можно выдать номер вывода (Pin), логическую ячейку или блок, а также, используя кнопки Change и Delete, изменить назначения.

Probe assignment (назначение зонда) присваивает легко запоминаемое уникальное имя входу или выходу логической функции. Данное назначение весьма полезно при моделировании системы. Для назначения зонда используют команду Assign /Probe.

Connected pin assignment (назначение соединённых выводов) задаёт внешнее соединение двух или более выводов. Эта информация также полезна в режиме тестирования временных параметров и при тестировании нескольких скомпонованных проектов. Для выполнения назначения соединённых выводов используют команду Assign/Connected/Pins.

Local routing assignment (назначение местной трассировки) присваивает коэффициент разветвлению по выходу узла логического элемента, находящегося в том же блоке или же в соседнем, смежным с выбранным узлом, с использованием общих местных связей. Местная трассировка так же производится между узлом, помещённым в блок на периферии устройства, и выходным контактом, с которым он соединён. Назначение местной трассировки производится с помощью команды Assign/local routing.

Device assignment (назначение устройства) назначает тип ПЛИС, в которой будет воплощён проект. Если проект состоит из нескольких устройств, данная функция осуществляет назначения чипов конкретным устройствам. Можно также выбрать опцию AUTO и предоставить компилятору выбрать устройство из заданного семейства устройств. Процессом автоматического выбора устройства можно управлять, задавая диапазон и число устройств в семействе. Если проект оказался слишком большим для реализации в одном устройстве, можно задать тип и число дополнительных устройств. Для выбора устройства используется команда Assign/Device.

Logicoption assignment (назначение логической опции) управляет синтезом отдельных логических функций во время компиляции с применением стиля логического синтеза и/или отдельных опций логического синтеза. Фирма Altera обеспечивает большое количество логических опций, а так же готовых стилей, каждый из которых представляет собой собрание установок для логических опций, объединённое одним именем стиля синтеза (Synthesis style). Пользователь может применять готовые стили или создавать новые, которые позволяют настраивать опции синтеза на определённое семейство устройств, учитывая при этом архитектуру семейства. Для настройки стилей синтеза применяется команда Assign/Logic Options.

Timing assignment (назначение временных параметров) управляет логическим синтезом и подгонкой отдельных логических функций для получения требуемых значений времени задержки Пользователь может также вырезать соединения между путями распространения для конкретного сигнала и другими ячейками (блоками) проекта. Назначение временных параметров блока производится по команде Assign/Timing Requirements.

Кроме использования команд меню Assign, назначения можно выполнять щелчком правой кнопки мыши по выбранному узлу проекта и выбирая соответствующее назначение во всплывающем меню.

Можно определить глобальные опции устройства для компилятора, для того чтобы он их использовал для всех устройств при обработке проекта. Для резервирования дополнительных возможностей логики на будущее можно задать процентное соотношение выводов и логических элементов, которые должны оставаться неиспользованными во время текущей компиляции. Можно также задать установки для битов опций устройств и выводов в конфигурации устройств, используемой для нескольких целей. Например, можно задать бит защиты от несанкционированного считывания (Security Bit) по умолчанию глобальным, что предотвратит пиратское копирование топологии устройств, базирующихся на памяти EPROM или EEPROM.

Помимо задания локальных назначений, возможно, задать назначения для всего проекта, используя так называемые глобальные назначения (Global Assignments). Можно ввести глобальные временные требования для проекта, задавая общие характеристики для времени задержки. Можно также удалять соединения между любыми двунаправленными контурами обратной связи, цепями прохождения сигналов Present (установка 1) и Clear (установка 0) и другими цепями синхронизации в проекте. Для этих целей используется команда Assign/Global Project Timing Requirements.

Можно сделать глобальные установки для компилятора в части логического синтеза проекта. Можно задать используемый по умолчанию стиль логического синтеза, определить критерий оптимизации либо быстродействие (Speed), либо занимаемым местом на кристалле (Area), дать указания компилятору по выбору автоматических глобальных сигналов управления, таких, как Clock (тактовый), Clear (установка 0), Preset (установка 1) и Output Enable (разрешение выхода). Для назначения глобальных параметров логического синтеза используют команду Assign/Global Project Logic Synthesis.

Вопросы для проверки усвоения материала

1. Какие два каталога имеет система MAX+PLUS II?

2. Из каких подкаталогов состоит каталог maxplus2?

3. Из каких подкаталогов состоит каталог max2work?

4. Какое полное название имеет система MAX+PLUS II?

5. Перечислите состав программного обеспечения системы MAX+PLUS II.

6. Процедура разработки нового проекта в системе MAX+PLUS II.

Вместе с этой лекцией читают "Лекция 2".

7. Приложения системы MAX+PLUS II.

8. Способы описания файлов проекта в системе MAX+PLUS II.

9. Общие функции для всех приложений MAX+PLUS II.

10. Типы назначений при управлении компиляцией проекта и его временных параметров в системе MAX+PLUS II.

Литература

1. Стешенко Б.В. ПЛИС фирмы АLTERA: проектирование устройств обработки сигналов. –М.: ДОДЭКА, 2000. –128 с. (38-50 с.)