Арифметико-логические устройства (АЛУ)

8. Арифметико-логические устройства (АЛУ).

8.1 Назначение и классификация АЛУ.

Арифметико-логическим устройством называется функционально законченный узел, предназначенный для реализации логических и арифметических операций по обработке информации.

Для выполнения арифметических и логических операций над входными переменными они должны быть введены в АЛУ, поэтому его дополняют вспомогательными устройствами, предназначенными для промежуточного хранения как исходных данных, так и результатов выполнения той или иной операции. Функции этих устройств возлагают на дополнительные регистры.

Основным элементом АЛУ являются сумматоры

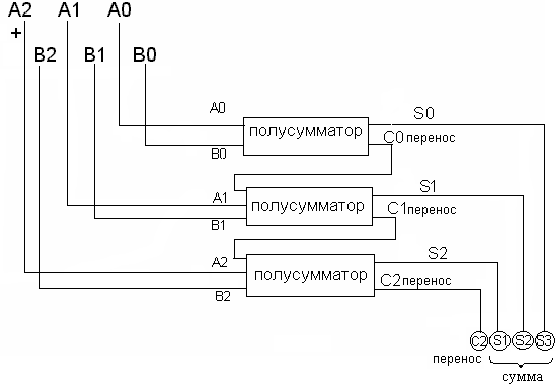

По числу выводов различают: полусумматоры, одноразрядные сумматоры, многоразрядные сумматоры.

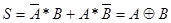

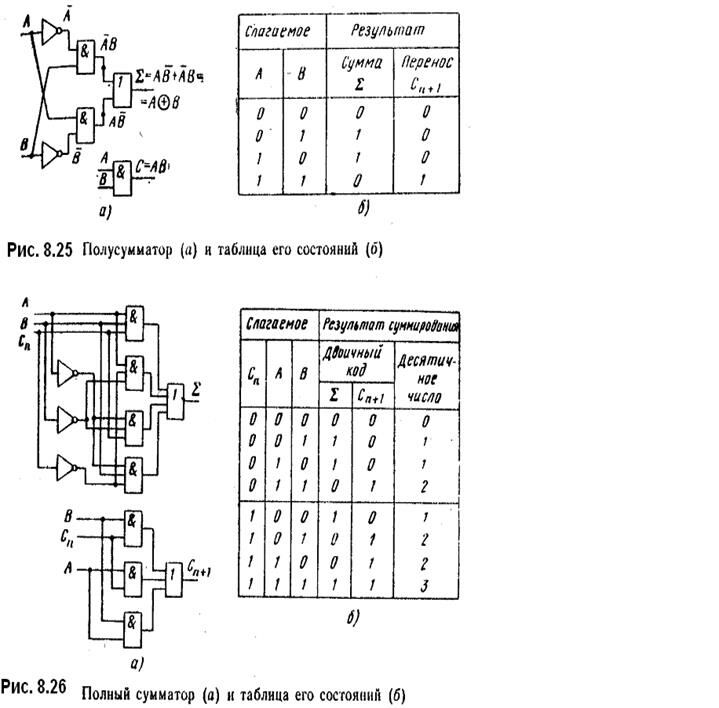

Полусумматором называется устройство , предназначенное для сложения двух одноразрядных кодов имеющие два входа и два выхода и формирующие из сигналов входных слагаемых и сигналы суммы и переноса в старший разряд.

Одноразрядным сумматором называется устройство, предназначенное для сложения двух одноразрядных кодов, имеющее три входа и два выхода и формирующие из сигналов входных слагаемых и сигнала переноса из младших разрядов сигналы суммы и переноса в старший разряд.

Рекомендуемые материалы

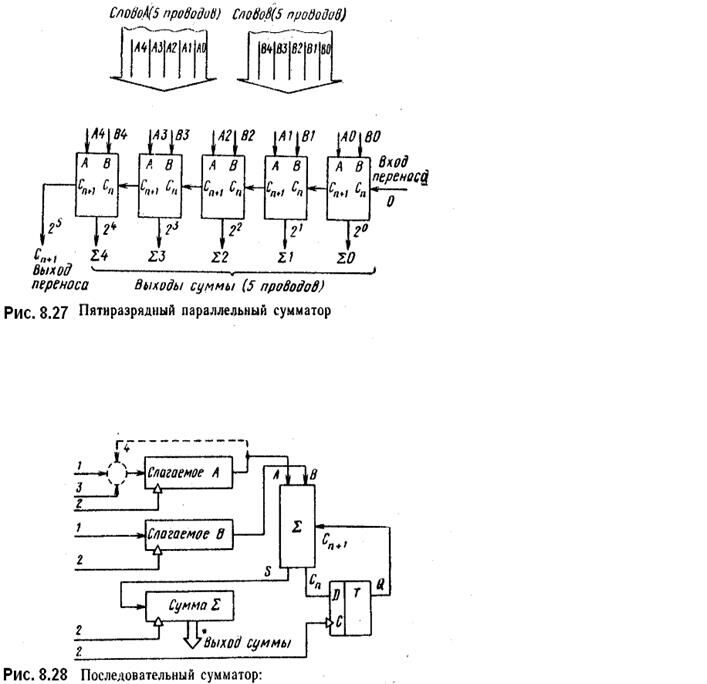

Многоразрядным сумматором называется устройство, предназначенное для сложения двух многоразрядных кодов, формирующее на выходе код суммы и сигнал переноса в случае, если результат сложения не может быть представлен кодом, разрядность которого совпадает с разрядностью кодов слагаемых.

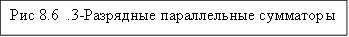

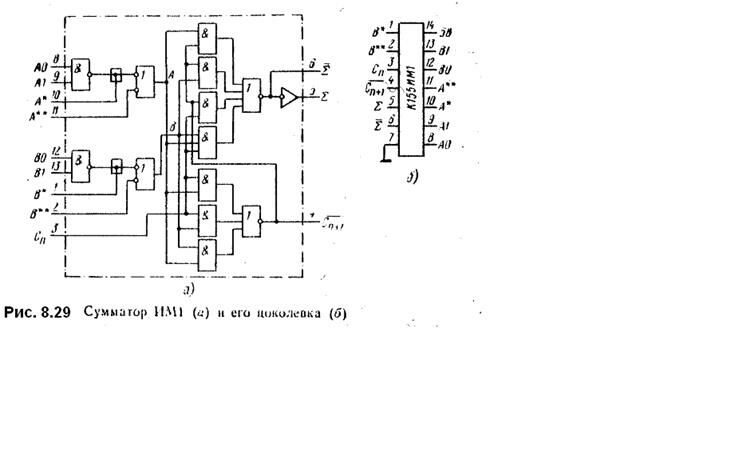

В свою очередь многоразрядные сумматоры подразделяются на последо-ватеные и параллельные. В последовательных сумматорах операция сложения выполняется последовательно разряд за разрядом, начиная с младшего. В параллельных все разряды входных кодов суммируются одновременно.

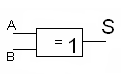

8.1 Полусумматоры.

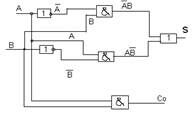

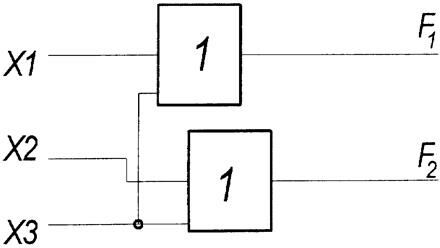

Рис. 8.1

|

Таблицы истинности.

| Входы | Выходы | ||

| В | А | S | С0 |

| 0 | 0 | 0 | 0 |

| 0 | 1 | 1 | 0 |

| 1 | 0 | 1 | 0 |

| 1 | 1 | 0 | 1 |

| Двоичные числа-слагаемые | Сумма | перенос |

|

Рис.8.2

Рис 8.3 Полусумматор

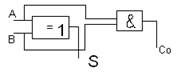

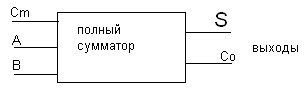

8.3 Полные сумматоры.

|

| входы | Выходы | |||

| Сm | B | A | S | Сo |

| 0 | 0 | 0 | 0 | 0 |

| 0 | 0 | 1 | 1 | 0 |

| 0 | 1 | 0 | 1 | 0 |

| 0 | 1 | 1 | 0 | 1 |

| 1 | 0 | 0 | 1 | 0 |

| 1 | 0 | 1 | 0 | 1 |

| 1 | 1 | 0 | 0 | 1 |

| 1 | 1 | 1 | 1 | 1 |

| Сумма | Перенос |

Рис. 8.4

Рис 8.5 Полный сумматор

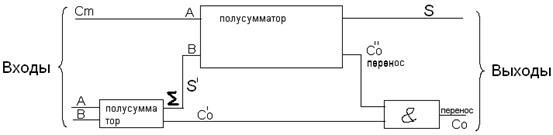

8.4 3-разрядные параллельные сумматоры.

Числа-слагамые.

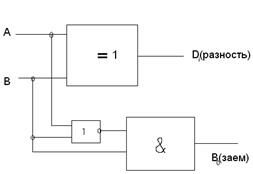

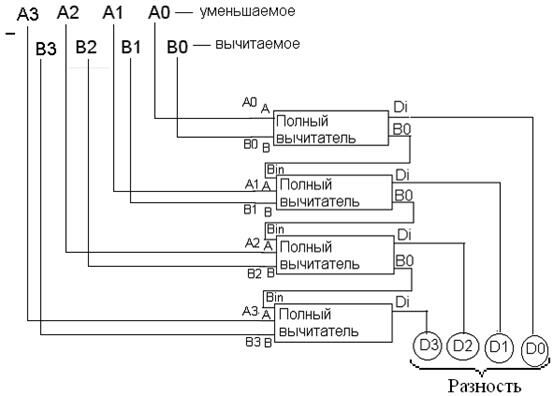

8.5 Двоичное вычитание, полувычитатель, полный вычитатель, 4-разрядный параллельный вычитатель.

Рис 8.7. Полувычитатель.

| Входы | Выходы | ||

| А | В | Di | B0 |

| 0 | 0 | 0 | 0 |

| 0 | 1 | 1 | 1 |

| 1 | 0 | 1 | 0 |

| 1 | 1 | 0 | 0 |

| Разность | Заем |

Рис. 8.8

Рис 8.9 . 4-разрядный параллельный вычитатель.

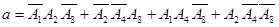

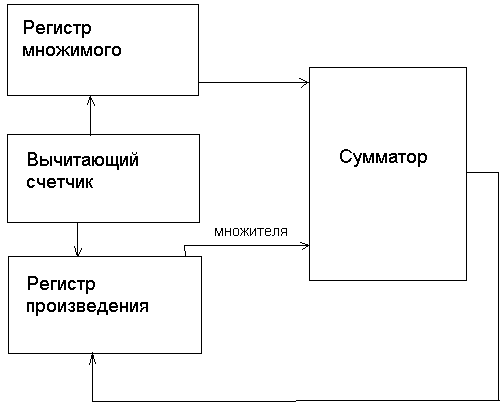

8.6 Двоичное умножение.

Операция умножение базируется на суммировании частотных произведений разрядов сомножителей.

a1 a0

´

b1 b0

|

a1*b1 a0*b0

+

a1*b1 a0*b1

|

M3 M2 M1 M0

Рис.8.10

Рис.8.10

7 1 1 1 – множимое

7 1 1 1 – множимое

´ ´

5 1 0 1 - множитель

5 1 0 1 - множитель

35 1 1 1 - первое частное произведение

35 1 1 1 - первое частное произведение

+

0 0 0 - второе частное произведение

+

1 1 1 - третье частное произведение

1 1 1 - третье частное произведение

1 0 0 0 1 1 – полное произведение

7+7+7+7+7=35

Рис 8.11 Структурная схема умножителя с использованием многократного сложения.

| Загрузка двоичного числа | После 1-го счета | После 2-го счета | После 3-го счета | После 4-го счета | После 5-го счета | |

| Регистр множимого | 111 | 111 | 111 | 111 | 111 | 111 |

| Счетчик множителя | 101 | 100 | 011 | 010 | 001 | 000 |

| Регистр произведения | 00000 | 00111 | 01110 | 10101 | 11100 | 100011 |

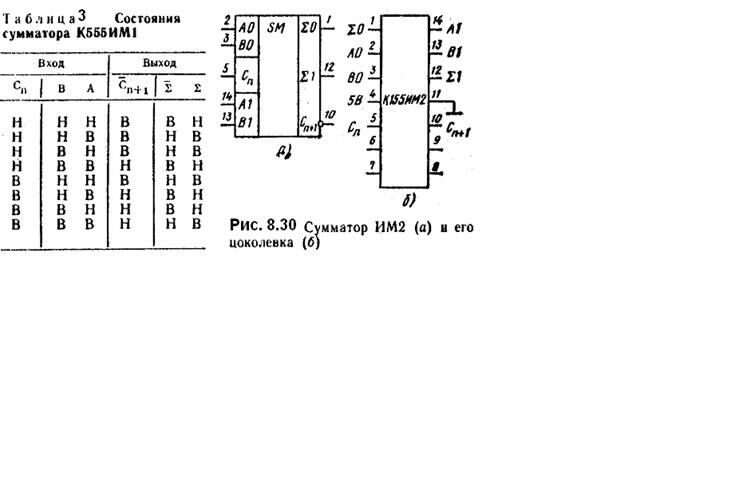

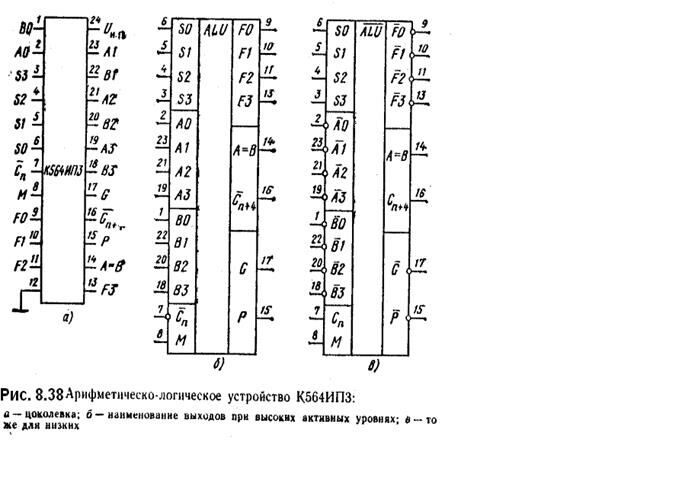

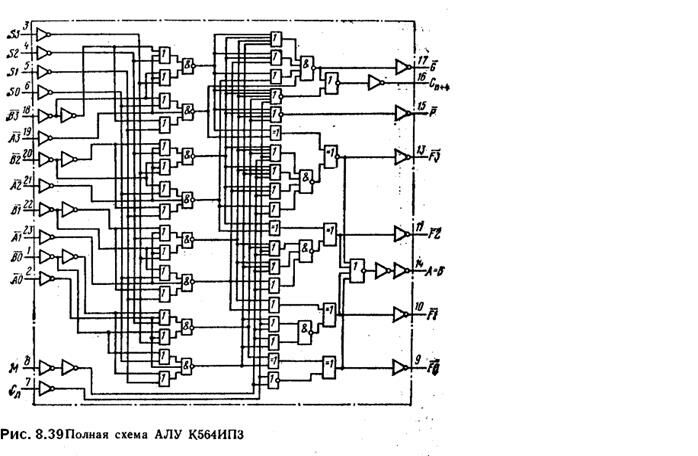

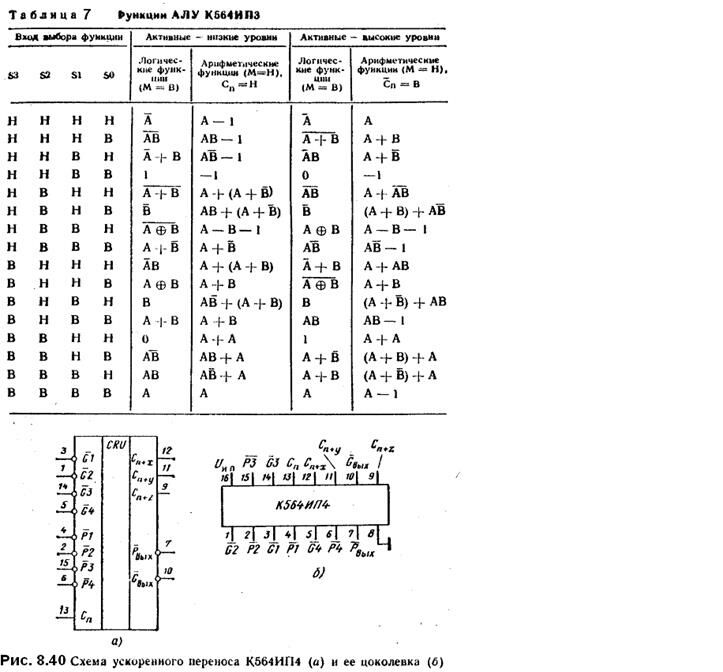

8.7 АЛУ на базе интегральной микросхемы К555ИП3.

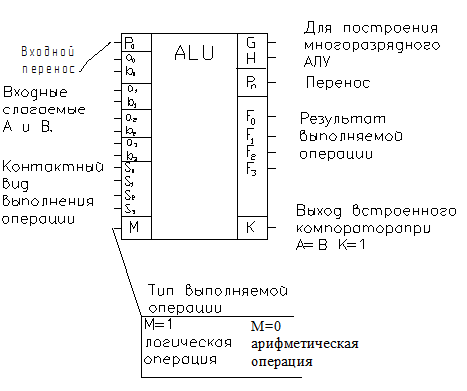

Рассмотрим функциональные возможности интегральной микросхемы К555ИП3.

Рис 8.12 АЛУ на базе интегральной микросхемы К555ИП3.

| Управляющие сигналы S3S2S1S0 | Логические операции M=1 | Арифметические операции M=0 |

| 0000 0001 0010 0011 |

0 | А

-1 |

| 0100 0101 0110 0111 |

А+В

| А+ ( А-В-1

|

| 1000 1001 1010 1011 |

В | А+ А+В (

|

| 1100 1101 1110 1111 | 1

А | А+А ( ( А-1 |

8.8 Семинар №5 "Двоичная арифметика"

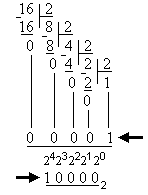

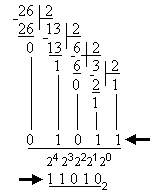

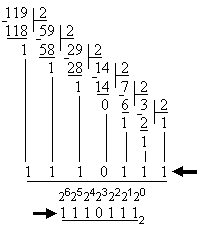

Задача №5.1

Перевести числа 1610, 2610, 11910, 25510, 102410 в двоичную систему счета.

Преобразование десятичных чисел в двоичные

| X10 | Y2 | Z8 | α16 | β4 |

| 0 | 0000 | 00 | 0 | 0 |

| 1 | 0001 | 01 | 1 | 1 |

| 2 | 0010 | 02 | 2 | 2 |

| 3 | 0011 | 03 | 3 | 3 |

| 4 | 0100 | 04 | 4 | 10 |

| 5 | 0101 | 05 | 5 | 11 |

| 6 | 0110 | 06 | 6 | 12 |

| 7 | 0111 | 07 | 7 | 13 |

| 8 | 1000 | 10 | 8 | 20 |

| 9 | 1001 | 11 | 9 | 21 |

| 10 | 1010 | 12 | A | 22 |

| 11 | 1011 | 13 | B | 23 |

| 12 | 1100 | 14 | C | 30 |

| 13 | 1101 | 15 | D | 31 |

| 14 | 1110 | 16 | E | 32 |

| 15 | 1111 | 17 | F | 33 |

| 16 | 10000 | 20 | 10 | 100 |

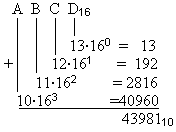

Задача №5.2

Записать значения чисел в десятичной и в двоичной системе счета

Записать значения чисел в десятичной и в двоичной системе счета

OFFF16 ABCD16 6416 1016 816

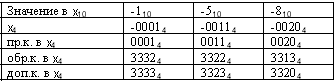

Задача №5.3

Выполнить суммирование чисел. Указать наличие переноса из старшего значащего разряда (С3Р) при выполнении суммирования в восьмиразрядной цифровой системе

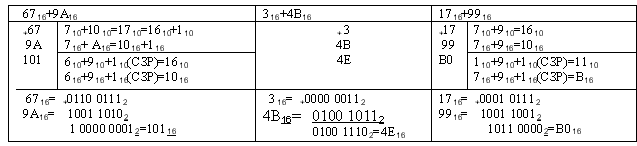

Задача №5.4

Выполнить вычитание чисел A16-616, 616-A16 в четверичной цифровой системе, применяя обычное правило вычитания

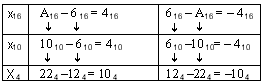

Задача №5.5

Вычислить дополнительный код чисел -110, -510, -810 в четверичной системе счета для четырехразрядной цифровой системы. Примечания: дополнительный код (доп.к.) = обратный код (обр.к.) + 1 обр.к. + прямой код (пр.к.) = максимальное значение в данной системе пр.к. - это положительное значение числа.

Задача №5.6

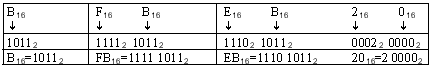

Вычислить двоичные значения шестнадцатеричных кодов B16, FB16, EB16, 2016.(используем таблицу 1)

8.9 Лабораторная работа "Цифровые многоразрядные регистры и сумматоры." Авторы Буянкин В.М., Васюков С.А. ,Шамгулов Р.О.

ОПИСАНИЕ ЛАБОРАТОРНОЙ УСТАНОВКИ

Лабораторная установка состоит из стандартной кассеты со схемой исследуемого устройства и универсального стенда ЛОЭ-2 (рис.8.13). Кассета содержит сумматор SM, регистры RG1, RG2, кодопреобразователь на схемах "исключающее ИЛИ" и светодиоды на выходе сумматора.

Слагаемые А и В набирают поочередно ключами SA1 - SA4, разряды входного числа индицируются светодиодами HL1...HL4, а суммы и переноса - светодиодами HL5-HL9.

Для выполнения операций сложения чисел А и В необходимо:

1. Выставить галетные переключатели в исходное положение: ГП1 - в положение 9 и ГПЗ - в положение 16; установить на управляющем входе кодопреобразователя код операции сложения, для этого галетный переключатель ГП2 перевести в положение 12.

2. Набрать ключами SA1 -SA4 четырехразрядное число А. Положение ключа SA4 определяет знак числа: если число А отрицательное, то его набирают в дополнительном коде.

3. Записать число А в регистр RG1. Для этого на вход разрешения записи С регистра RG1 подается сигнал высокого логического уровня путем перевода галетного переключателя ГП2 из исходного положения 9 в положение 10. При этом число А сразу же из регистра RG1 попадает на входы А1 - А4 сумматора, а на его выходах формируется промежуточная сумма S = А.

4. Набрать ключами SA1 - SA4 четырехразрядное число В.

5. Записать число В в регистр RG2, переводя ГП1 из положения 10 в положение 11. При этом число В сразу же появляется на входах сумматора В1 - В4, а на входах S1 - S4 появляется сумма S = А + В и сигнал переноса Р4.

Для выполнения операций вычитания чисел А и В необходимо:

1. Выставить галетные переключатели в исходное положение: ГП1 - 9, ГП2 - 13, ГП3 - 16.

2. Набрать число А и переводом ГП1 в положение 10 записать его в RG1 и SM.

3. Набрать число В. Так как на управляющем входе колопреобразователя установлена единица, на его выходе формируется обратный код числа  .

.

4. Сформировать на входах сумматора дополнительный код  , переведя переключатель ГП1 в положение 11.

, переведя переключатель ГП1 в положение 11.

Проделав вышеперечисленные операции, в сумматоре SM мы сформировали сумму чисел А, обратного кода числа  логической единицы переноса РО : S = А +

логической единицы переноса РО : S = А +  + РО, но

+ РО, но  + 1 =

+ 1 =  , т.е. S = А +

, т.е. S = А +  = А - В.

= А - В.

Рис.8.13

Рис.8.13

ЗАДАНИЕ И ПОРЯДОК ВЫПОЛНЕНИЯ РАБОТЫ

Ознакомиться с лабораторной установкой. Выяснить назначение управляющих ключей игалетных переключателей.

Получить разрешение преподавателя на проведение работы.

А. Исследовать операцию суммирования цифровых сигналов.

Подготовить таблицу 1 для записи слагаемых и их суммы. Слагаемые представляйте в четырехразрядной сетке со знаком.

Таблица 1.

| № П/П | Слагаемое | Слагаемое | P0 | Сумма | P4 | Примечания | |||

| A10 | A2 | B10 | B2 | S10 | S2 | ||||

| 1 | A10 >0, B10 >0, S10 ≤710 | ||||||||

| 2 | A10 >0, B10 <0, |A10|>|B10|, |S10|<710 | ||||||||

| 3 | A10 <0, B10 >0, |A10|>|B10|, |S10|<710 | ||||||||

| 4 | A10 <0, B10 <0, |S10|≤710 | ||||||||

| 5 | 710 | 110 | A10 =710, B10 =110 |

- Предложите для суммирования два положительных числа: А10 и В10, такие, чтобы их сумма находилась в диапазоне представления чисел в четырехразрядной сетке со знаком. Так как под значащие разряды числа отведено всего три разряда, максимально возможная сумма равна 1112=710.

1. Выполните суммирование чисел А10 и В10 вручную и с помощью сумматора, сравните результаты; коды и суммы отобразите в табл.2

2. Выполните суммирование чисел А10 и В10, A10 >0, B10 <0, |A10|>|B10|, S10<710.

3. Выполните суммирование чисел А10 и В10, A10 <0, B10 >0, |A10|>|B10|, S10<710.

4. Выполните суммирование чисел А10 и В10, A10 <0, B10 <0, S10≤710.

5. Выполните суммирование положительного числа А10 - максимально возможного для указанного диапазона представления (в нашем случае А10 = 7) и числа 110.

При выполнении действий, описанных в п. п. 2 - 5, суммирование чисел сначала произведите вручную и затем сравните результаты с содержимым выходных разрядов сумматора; коды слагаемых и сумм отобразите в табл.2

Б. Исследование операции вычитания цифровых сигналов.

Подготовьте табл.2 для записи вычитаемого, уменьшаемого и разности чисел А и B.

Таблица 2

| № П/П | Слагаемое | Слагаемое | P0 | Сумма | P4 | Примечания | |||

| A10 | A2 | B10 | B2 | S10 | S2 | ||||

| 1 | A10 >0, B10 >0, S10 ≤710, A10 >B10 | ||||||||

| 2 | A10 >0, B10 >0, A10<B10, |S10|<710 | ||||||||

| 3 | A10 >0, B10 <0, S10≤710 | ||||||||

| 4 | A10 =B10 | ||||||||

| 5 | A10 <0, B10 >0, S10>710 |

Проделайте пять раз операцию вычитания чисел в соответствии с условиями, указанными в графе "Прмечания" табл.2

Сделайте выводы по результатам сложения и вычитания.

ОПИСАНИЕ ЛАБОРАТОРНОЙ УСТАНОВКИ 2

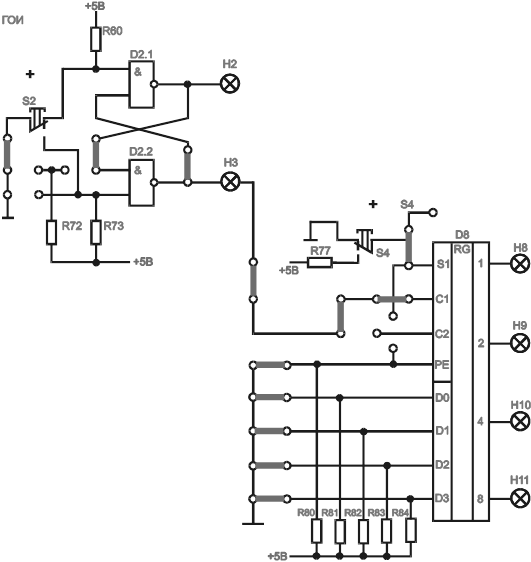

Лабораторная установка 2 представлена на рис. 8.14 и состоит из регистра К155ИР1

.Задание 1. Изучить таблицу состояний регистра К155ИР1. Определить возможные режимы работы и комбинации управляющих сигналов задающие их. На рис.7 представлен лабораторный стенд.

Рис.8.14. Лабораторный стенд.

Рис.8.14. Лабораторный стенд.

Таблица 2. Таблица состояния регистра К155ИР1

| Вход | Выход | ||

| ___ __ __ PE C2 C1 | Посл. S1 | Параллельные D0 D1 D2 D3 | Q0 Q1 Q2 Q3 |

| B B × × × × × × Q0 Q1 Q2 Q3 B ↓ × × a b c d a b c d B ↓ × × Q1 Q2 Q3 d Q1 Q2 Q3 d H H B × × × × × Q0 Q1 Q2 Q3 H × ↓ B × × × × B Q0 Q1 Q2 H × ↓ H × × × × H B Q0 Q1 ↑ H H × × × × × Q0 Q1 Q2 Q3 ↓ H H × × × × × Q0 Q1 Q2 Q3 ↓ H B × × × × × Q0 Q1 Q2 Q3 ↑ B H × × × × × Q0 Q1 Q2 Q3 ↑ B B × × × × × Q0 Q1 Q2 Q3 | |||

Уровень логической «1» соответствует обозначению «В», уровень логического «0» соответствует обозначению «Н». Обозначения Q0-Q3 соответствуют состоянию выходов регистра до подачи тактовых импульсов. Обозначение: ↓ - срабатывание по срезу тактового импульса, ↑- срабатывание по фронту тактового импульса, a,b,c,d- обозначают вводимую информацию.

Задание 2. Исследовать работу регистра в режиме очистки.

2.1. Собрать схему, представленную на рис.1. Определить какому режиму работы она соответствует. Включить стенд и определить состояние регистра по индикаторам Н8-Н11. Подать на тактовый вход С1 четыре импульса с помощью кнопки S2 фиксируя состояние выходов регистра после каждого импульса. Результат наблюдений свести в таблицу 1.

2.2. Отключить стенд и переставить перемычку с входа С1 на вход С2, а перемычку соединяющую вход РЕ с общим проводом убрать. Включить стенд

и зафиксировать состояние выходных сигналов регистра. Подать тактовый импульс на вход С2. Определить состояние регистра. Результаты наблюдений свести в таблицу 3. (Стенд отключить, схему не разбирать.).

Таблица 3 Состояния входов и выходов регистра

| № Так. | PE | C2 | C1 | S1 | D0 | D1 | D2 | D3 | Q0 | Q1 | Q2 | Q3 |

|

| ||||||||||||

| ↓ |

| |||||||||||

| ↓ | ||||||||||||

| ↓ | ||||||||||||

| ↓ |

Рис.8.15. Схема регистра

Таблица 4.

| № Так. | РЕ | C2 | C1 | S1 | D0 | D1 | D2 | D3 | Q0 | Q1 | Q2 | Q3 | |

| . | |||||||||||||

| ↓ |

Задание 3. Исследовать работу регистра в режиме параллельной записи информации.

3.1. Установить на входах D0-D3 двоичный код, десятичного числа заданного преподавателем.

Уровень логической «1» на соответствующем входе задается отключением перемычки от общего провода. Включить стенд и зафиксировать состояние выходов регистра. Подать тактовый импульс на вход С2 и зафиксировать состояние выходов. Повторить опыт с другим двоичным числом на входах D. Результаты занести в таблицу 3.

Таблица 5.

| № Так. | PE | C2 | C1 | S1 | D0 | D1 | D2 | D3 | Q0 | Q1 | Q2 | Q3 | |

| . | |||||||||||||

| ↓ | |||||||||||||

| ↓ |

Задание 4. Исследовать работу регистра в режиме последовательной записи информации.

4.1.Очистить регистр (одним из выше исследованных способов) и установить режим последовательной записи информации, используя необходимые перемычки. Получить у преподавателя число, двоичный код которого требуется ввести. Для задания логических уровней на последовательном входе S1 используется переключатель S4.

Вводимое число ………............. Двоичный код ……………………

4.2. Введите заданное число в регистр, подав необходимое число тактовых импульсов (S2). Обратить внимание на то, в каком порядке вводятся разряды двоичного числа. Результаты записи занести в таблицу 4. Стенд не отключать.

Задание5. Исследовать работу регистра в режиме сдвига.

5.1. Установить на входе S1 уровень логического «0»(переключатель S4). Подайте четыре тактовых импульса.

5.2 .Установите на последовательном входе уровень логической «1». Подайте четыре тактовых импульса. Результаты занести в таблицу 4. Определите, направление сдвига информации по состоянию выходов регистра (таб.4) и по заполнению разрядов двоичного числа.

Таблица 6.

| № Так. | PE | C2 | C1 | S1 | D0 | D1 | D2 | D3 | Q0 | Q1 | Q2 | Q3 | Прим. | |

| Зад.4 | ||||||||||||||

| Зад.5 | ||||||||||||||

Задание 6. Изобразите схему устройства на регистре К155ИР1, позволяющего выполнять операцию сдвига вправо (в сторону младшего разряда).

Схема устройства. ( Подсказка: составляя схему, используйте третью строчку таблицы состояний регистра).

СОДЕРЖАНИЕ ОТЧЕТА

В отчете должны быть указаны фамилия и инициалы исполнителя, номер группы и дата выполнения. В соответствии с заданием должны быть приведены:

-схема исследуемого устройства;

-таблицы результатов сложения и вычитания;

-выводы;

Отчет необходимо выполнять аккуратно, схемы и таблицы - с использованием чертежных инструментов.

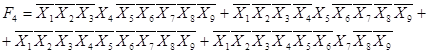

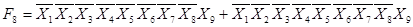

8.10 Семинар №6. Комбинационные устройства двоичной арифметики.

Задача №6.1

Составить логическую схему шифратора одноразрядных десятичных цифр. Составить таблицу истинности, уравнения выходных сигналов.

Рис 8.14

Рис 8.14

Таблица

истинности

| X1 | Х2 | Х3 | Х4 | Х5 | Х6 | Х7 | Х8 | Х9 | f1 | F2 | F4 | F8 | F10 |

| *1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 0 | 0 | 1 |

| 0 | *1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 0 | 2 |

| 0 | 0 | 0 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 4 |

| 0 | 0 | *1 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 1 | 0 | 0 | 3 |

| 0 | 0 | 0 | 0 | 1 | 0 | 0 | 0 | 0 | 1 | 0 | 1 | 0 | 5 |

| 0 | 0 | 0 | 0 | 0 | 1 | 0 | 0 | 0 | 0 | 1 | 1 | 0 | 6 |

| 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 0 | 0 | 0 | 1 | 8 |

| 0 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 0 | 1 | 1 | 1 | 0 | 7 |

| 0 | 0 | 0 | 0 | о | 0 | 0 | 0 | 1 | 1 | 0 | 0 | 1 | 9 |

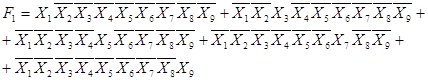

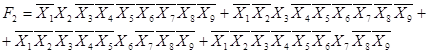

Уравнения выходных сигналов

Рис. 8.15

Рис. 8.15

| X | X | X | 1 |

| 1 | X | X | X |

| X | 1 | X | X |

| 1 | X | X | X |

Рис.8.16

Задача № 6.2.

Составить логическую схему преобразования чисел от 0 до 9910 из двоично-десятичного кода (BCD) в двоичный (B)с использованием стандартной интегральной схемы кодопреобразователя.

К155РП Рис.8.17

ВСД-> В

К155РП7

В-> ВСД

| Счет | Входные: (BCD) - код | Выходные: (B) код | |||||||||||||

| 80 | 40 | 20 | 10 | 8 | 4 | 2 | 1 | 64 | 32 | 16 | 8 | 4 | 2 | 1 | |

| 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 1 |

| . . . | |||||||||||||||

| 39 | 0 | 0 | 1 | 1 | 1 | 0 | 0 | 1 | 0 | 1 | 0 | 0 | 1 | 1 | 1 |

| . . . | |||||||||||||||

| 99 | 1 | 0 | 0 | 1 | 1 | 0 | 1 | 0 | 1 | 1 | 0 | 0 | 0 | 1 | 1 |

Задача №6.3.

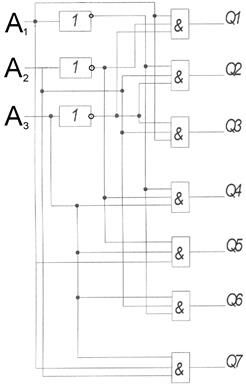

Составить логическую схему дешифратора трехразрядных чисел, представленных в B коде, в сигналы десятичной системы счета.

Рис.8.18

Рис.8.18

| Счет | Входной код В | Выходной код BCD | ||||||||

| A1 | A2 | A4 | Q1 | Q2 | Q3 | Q4 | Q5 | Q6 | Q7 | |

| 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| 1 | 1 | 0 | 0 | 1 | 0 | 0 | 0 | 0 | 0 | 0 |

| 2 | 0 | 1 | 0 | 0 | 1 | 0 | 0 | 0 | 0 | 0 |

| 3 | 1 | 1 | 0 | 0 | 0 | 1 | 0 | 0 | 0 | 0 |

| 4 | 0 | 0 | 1 | 0 | 0 | 0 | 1 | 0 | 0 | 0 |

| 5 | 1 | 0 | 1 | 0 | 0 | 0 | 0 | 1 | 0 | 0 |

| 6 | 0 | 1 | 1 | 0 | 0 | 0 | 0 | 0 | 1 | 0 |

| 7 | 1 | 1 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 1 |

Рис. 8.19

Задача 6.4.

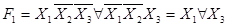

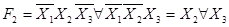

Составить таблицу истинности дешифратора для сегментного индикатора (К155ПП5). Составить карту Карно для минимизации логического уравнения одного из сегментов. Записать логическое уравнение.

Рис.8.20

Рис.8.20

| Счет | Входной код B | Выходной код | |||||||||

| A1 | A2 | A4 | A8 | a | b | c | d | e | f | g | |

| 0 | 0 | 0 | 0 | 0 | 1 | 1 | 1 | 1 | 1 | 1 | 1 |

| 1 | 1 | 0 | 0 | 0 | 0 | 1 | 1 | 0 | 0 | 0 | 0 |

| 2 | 0 | 1 | 0 | 0 | 1 | 1 | 0 | 1 | 1 | 0 | 1 |

| 3 | 1 | 1 | 0 | 0 | 1 | 1 | 1 | 1 | 0 | 0 | 1 |

| 4 | 0 | 0 | 1 | 0 | 0 | 1 | 1 | 0 | 0 | 1 | 1 |

| 5 | 1 | 0 | 1 | 0 | 1 | 0 | 1 | 1 | 0 | 1 | 1 |

| 6 | 0 | 1 | 1 | 0 | 1 | 0 | 1 | 1 | 1 | 1 | 1 |

| 7 | 1 | 1 | 1 | 0 | 1 | 1 | 1 | 0 | 0 | 0 | 0 |

| 8 | 0 | 0 | 0 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 |

| 9 | 1 | 0 | 0 | 1 | 1 | 1 | 1 | 1 | 0 | 0 | 0 |

-неминимизированное уравнение

-неминимизированное уравнение

карта Карно

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

-минимизированное уравнение

Задача №6.5

Составить логическую схему блока перемножения двух двухразрядных положительных двоичных чисел.

Рис.8.21

Рис.8.21

Структурная схема умножителя с использованием способа многократного сложения:

(7*4=7+7+7+7=28)

Рис.8.21

Рис.8.21

710 х 410

1110 х 1002

| Загрузка Двоичных чисел | После 1-го счета | После 2-го счета | После 3-го счета | После 4-го счета | |

| Регистр множимого | 111 | 111 | 111 | 111 | 111 |

| Счетчик множителя | 100 | 011 | 010 | 001 | 000 |

| Регистр произ- ведения | 0000 | 111 + 0000 111 | 111 + 111 01110 | 1110 + 111 10101 | 10101 + 111 11100 |

| Загрузка | Остановка |

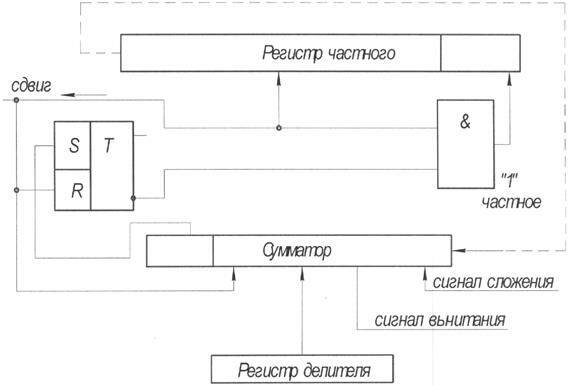

Задача №6.6

Составить таблицу истинности блока деления двухразрядных положительных чисел: трехразрядное X на двухразрядное Y.

Рис.8.22

Рис.8.22

| 0.11 0.10 | 0.10 делимое 0.10 делитель | Разряды частного |

| 0 + 0 0 | Определение кода знака частного | |

| 110 + 110 Если Вам понравилась эта лекция, то понравится и эта - 37.Формула шагреневой кожи как ключ к судьбе личности в Человеческой комедии Бальзака.. 1100 | Сдвиг делимого влево на один разряд Делитель (дополнительный код) |

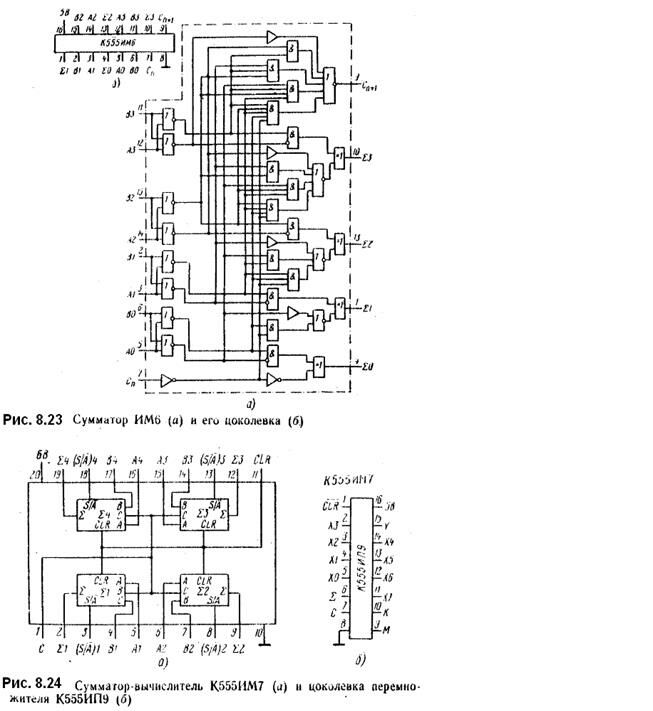

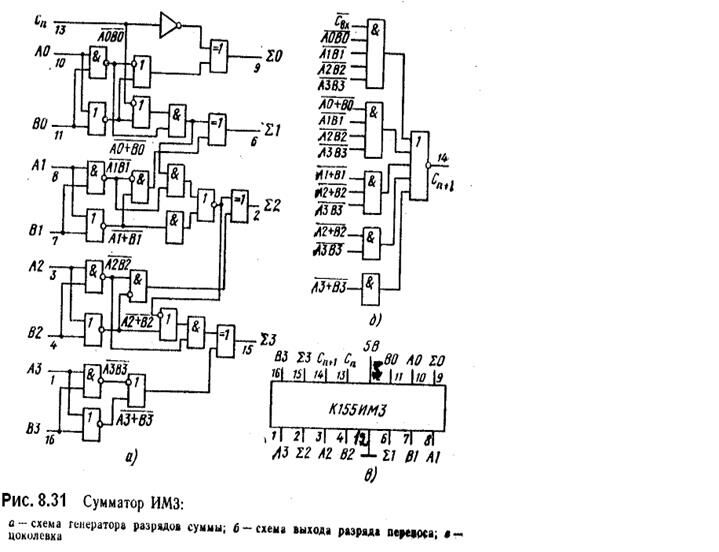

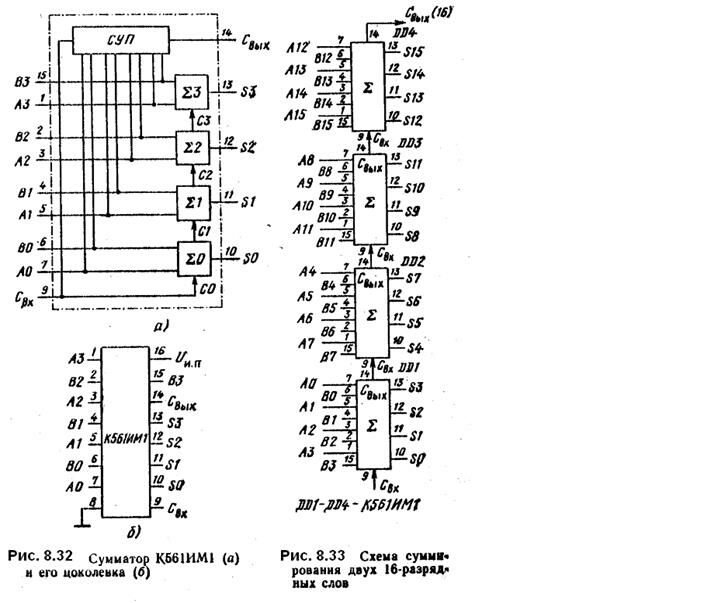

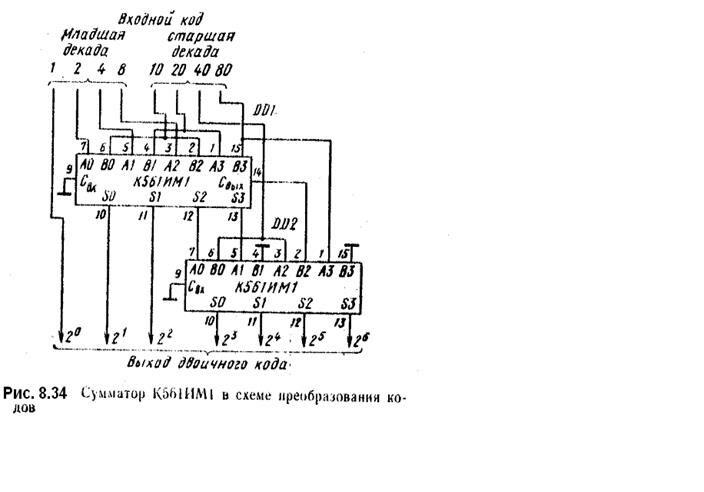

8.11 Арифметические схемы ТТЛ

.

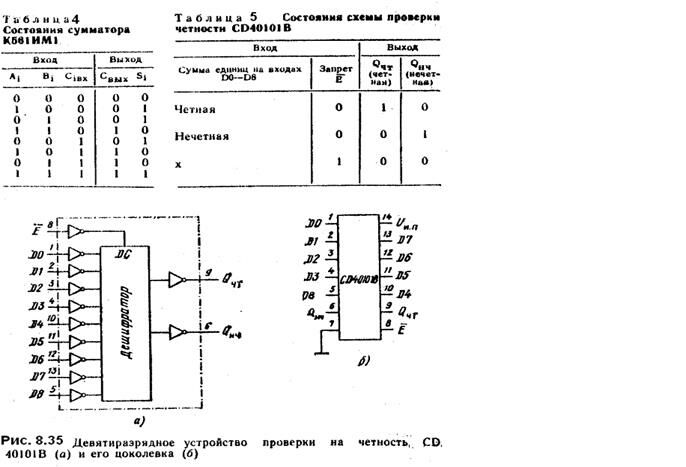

8.12 Арифметические схемы КМОП

Рекомендуемые лекции

- 4 Методы определения собственных частот и собственных форм упругих систем

- 8 Структурные схемы и передаточные функции тягового электродвигателя как линеаризованного объекта регулирования

- 33 Финансовая статистика железнодорожного транспорта

- 37.Формула шагреневой кожи как ключ к судьбе личности в Человеческой комедии Бальзака.

- 41 Проведение проверок и корректирующие действия

1

1 1

1 1

1

1

1

1

1

1

1 1

1