Последовательностные схемы

1. Последовательностные схемы

Последовательностные схемы или цифровые автоматы (ЦА) с памятью составляют другой, более сложный класс преобразователей дискретной информации. В отличие от КС они имеют некоторое конечное число различных внутренних состояний. Выходные сигналы ЦА в данном такте определяются в общем случае входными сигналами, поступившими на вход ЦА в этом такте, и внутренним состоянием автомата, которое явилось результатом воздействия на автомат входных сигналов в предыдущие такты.

Комбинация входных сигналов и текущего состояния ЦА в данном такте определяет не только выходные сигналы, но и то состояние, в которое автомат перейдет к началу следующего такта.

Функции перехода и выходов могут задаваться в форме таблиц или с помощью графов. При задании в виде графов состояния автомата представляют вершинами, а переходы из состояния в состояние – дугами. На дугах указываются значения входных сигналов, вызывающих соответствующие переходы.

Примерами простейших конечных ЦА являются триггеры .

1.1. Триггеры

4.1.1 RS-триггер

Триггером (Т) называют логическую схему с положительной обратной связью, имеющую два устойчивых состояния, которые называются единичным и нулевым и обозначаются 1 и 0. Перевод триггера в единичное состояние путем воздействия на его входы называют установкой (set) триггера, а устанавливающий сигнал и вход, на который он воздействует, обозначают S (от set). Перевод триггера в нулевое состояние называют сбросом (reset), а соответствующий сигнал и вход обозначают R.

Схема простейшего триггера (рис.4.1,а) получается, если включить кольцом два элемента И-НЕ. Такой триггер имеет два входа R и S, два выхода Q и называется RS-триггером. Его обозначение на функциональных схемах показано на рис. 4.1, б.

а) б) в)

а) б) в)

Рис.4.1. RS-триггер на элементах И-НЕ

Пока на обоих управляющих входах R и S уровни сигналов не активны, в данном случае R=S=1, триггер находится в каком-либо одном из двух устойчивых состояний. Если значение сигнала на выходе Q равно 1, то, как видно из схемы, этот единичный сигнал, поступая по цепи обратной связи на вход элемента 2, вызывает появление на выходе сигнала с нулевым уровнем. В свою очередь нулевой уровень выхода , поступая на вход элемента 1, поддерживает Q в состоянии 1. Иначе говоря, при входных сигналах R и S, равных 1, появившаяся по любой причине на выходе Q единица по цепи обратной связи будет сама себя поддерживать сколь угодно долго. Когда на прямом выходе Q сигнал равен 1, говорят, что триггер находится в состоянии 1 или что он установлен.

Рекомендуемые материалы

В силу симметрии схемы она будет столь же устойчива в своем противоположном - нулевом состоянии, когда Q =0, а =1. В этом случае говорят, что триггер сброшен. Режим RS-триггера, когда оба управляющих сигнала R и S неактивны, называют режимом хранения.

На рис. 4.1,в показана временная диаграмма переходных процессов в схеме при подаче на нее управляющих сигналов. Исходное состояние триггера - нулевое, на его входы поступают по очереди сначала сигнал S, затем, после его окончания - сигнал R.

Из диаграммы видно, что после окончания входного сигнала триггер способен сохранять свое новое состояние также сколь угодно долго. Говорят, что триггер запоминает входной сигнал. Это специфическое и очень важное свойство триггера, отличающее его от всех рассмотренных ранее схем, не имевших обратных связей: после исчезновения входного сигнала выходной сигнал в тех схемах также исчезал.

Если на входы R и S подать одновременно нулевые сигналы, то на обоих выходах Q и появятся единицы . Если теперь одновременно снять нули со входов R и S, то оба элемента начнут переключаться в нулевое состояние, каждый стремясь при этом оставить своего партнера в состоянии 1. Какой элемент одержит в этом поединке победу, будет зависеть от скоростей переходных процессов и ряда других неизвестных заранее факторов. Для разработчика схемы результирующее состояние триггера оказывается неопределенным, неуправляемым. Поэтому комбинация R=S=0 считается запрещенной, и в обычных условиях ее не используют. Такую комбинацию допустимо применять, лишь когда обеспечено не одновременное, а строго поочередное снятие R и S-сигналов.

Основное назначение триггеров в цифровых схемах - хранить выработанные логическими схемами результаты. Для отсечения еще не установившихся, искаженных переходными процессами результатов между выходом логической схемы и входом триггера можно включить конъюнкторы, управляемые синхросигналом . Это решение оказалось очень эффективным, быстро стало типовым и побудило изготовителей триггеров ввести конъюнкторы в состав триггера. Так появились синхронные триггеры, которые переключаются в состояние, предписываемое управляющими входами, лишь по сигналу синхронизации, поступающему на вход С триггера.

а) б)

а) б)

Рис. 4.2. Синхронный RS-триггер

Схема простейшего синхронного RS-триггера показана на рис.4.2,а. При С=0 триггер 3-4 отключен от управляющих S и R входов и находится в режиме хранения ранее полученной информации. При С=1 схема функционирует как обычный RS-триггер. Условное изображение синхронного RS-триггера показано на рис.4.2,б. Синхровход С может в принципе иметь и активный низкий уровень; в этом случае он, как обычно, помечается кружочком. Характерной особенностью схемы является то, что в течение всего отрезка времени, когда синхросигнал равен 1, как сами потенциалы на управляющих S и R входах, так и любые их изменения тут же передаются на выход.

О такой схеме можно сказать, что она прозрачна по S - и R - входам при C=1. Не все схемы синхронных триггеров обладают этим свойством.

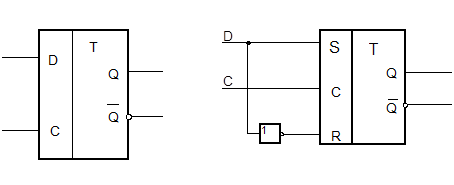

4.1.2. D - триггер типа «защелка»

D-триггером называют синхронный триггер, имеющий два входа: вход данных D и вход синхронизации С. Этот тип триггера исключительно широко используется в цифровых устройствах. Другие его названия: прозрачная защелка (transparent latch), D-триггер, управляемый уровнем синхросигнала. D-триггер переключается только по сигналу на С-входе и притом в состояние, предписываемое D-входом. Условное обозначение D-триггера показано на рис. 4.3, а.

а) б)

Рис.4.3. D – триггер

На рис. 4.3, б показан универсальный способ построения D-триггера из синхронного RS-триггера: с помощью инвертора 1 однофазный вход данных D превращается в парафазный и подается на S- и R -входы.

Изменения D-входа при С= 0 никак не влияют на состояние выхода Q: триггер заперт по С-входу и находится в режиме хранения. Фронт С-сигнала вызывает переключение триггера в то состояние, которое было к этому моменту на входе D. При С=1 защелка прозрачна: любое изменение D-входа вызывает изменение выхода Q. По спаду синхросигнала триггер – защелка фиксирует на выходе то состояние, которое было на D-входе непосредственно перед этим моментом. Следующее изменение Q будет возможно только по фронту следующего синхроимпульса. Если на С-вход подать постоянный единичный уровень, то свойство запоминания у защелки проявляться никак не будет и она будет выполнять функции обычного буферного усилителя мощности в тракте передачи данных.

Чтобы процесс фиксации состояния D-входа прошел без сбоев, т. е. был бы однозначно предсказуемым, переходной процесс в схеме защелки, вызванный срезом С-сигнала, не должен накладываться на переходной процесс, вызванный переключением D-входа. Это значит, что всякие изменения состояния D-входа должны прекратиться за некоторое время до среза С-сигнала, называемое временем подготовки (setup time), и могут снова начинаться после среза С-сигнала не ранее чем через время выдержки (удержания) (hold time).

Необходимость введения и нормирования интервалов подготовки и выдержки характерна не только для защелки, но и для всех функциональных узлов, имеющих вход синхронизации. Кроме того, для защелки, как и для любого синхронного узла, существует минимально допустимая длительность синхроимпульса, обеспечивающая отсутствие сбоев из-за наложения переходных процессов от фронта и среза этого импульса.

Для триггеров-защелок, выпускаемых в виде микросхем, временные характеристики приводятся в справочниках. Примерами выпускаемых промышленностью D-триггеров-защелок могут служить интегральные микросхемы (ИМС) К155ТМ5, К155ТМ7, К561ТМЗ, которые содержат по четыре триггера с объединенными С-входами.

4.1.3. Двухступенчатые триггеры

На рис. 4.4, а показана схема, состоящая из двух последовательно включенных синхронных RS-триггеров, первый из которых называется ведущим или М-триггером (от master - хозяин), а второй—ведомым или S-триггером (от slave - раб). Благодаря общему синхросигналу С вся схема функционирует как единое целое и называется двухступенчатым или MS-триггером . Из временной диаграммы (рис. 4.4, б) видно, что информация, задаваемая уровнями на входах S и R, по фронту С-сигнала принимается в М-триггер, но в течение всего •времени, пока С-сигнал равен 1, не проходит в S-триггер, поскольку его входные конъюнкторы 5 и 6 в это время перекрыты инверсией С-сигнала. Они откроются лишь при С==1, т.е. на спаде С-сигнала, и только тогда S-триггер примет состояние М-триггера. Сказанное иллюстрирует очень важное отличие MS-триггера от триггера-защелки: MS-триггер, собранный по схеме рис.4.4,а, непрозрачен по управляющим R и S входам ни при С=0, ни при С=1. Каждая ступень его сама по себе прозрачна, но включены ступени последовательно, и какая-нибудь одна из них всегда оказывается запертой - или синхросигналом, или его отсутствием. Таким образом, в этом MS-триггере при С=1 (и тем более при С=0) никакое изменение на управляющем входе не может само по себе, без переключения С-сигнала, проникнуть на выход. Триггер может изменить состояние выхода только по спаду С-сигнала. В зарубежной литературе непрозрачные триггеры называют flip-flop в отличие от прозрачных D-триггеров, за которыми укрепился термин latch.

а) б)

а) б)

Рис. 4.4; Двухступенчатый RS-триггер

Управляющие S- и R-сигналы могут обновляться по спаду того же синхроимпульса, который управляет триггером, и триггер при этом всегда будет воспринимать лишь предыдущее, еще не обновленное состояние S и R сигналов. На этом свойстве держится вся идеология однофазной синхронизации.

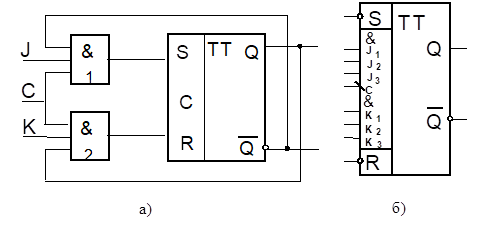

Свойство непрозрачности MS-триггера использовано для построения широко применяемого JK-триггера, схема которого показана на рис.4.5,а

Рис.4.5. JK – триггер

JK-триггер-это непрозрачный триггер, выходы которого петлями обратных связей накрест заведены на входные конъюнкторы 1 и 2. Внешние входы самого триггера при этом принято называть уже не S и R, а J и К.

При J= K=0 С-сигнал не может открыть входные элементы 1 и 2, и триггер находится в режиме хранения. При J=1, К=0 синхросигналом может быть открыт лишь элемент 1 и только при условии, что перед поступлением С-сигнала на выходе триггера был 0 (Q=0). Тогда по спаду синхросигнала триггер переключится в «1». Если же триггер до синхросигнала был в «1», то он так и останется в «1». Таким образом, J-вход выполняет функции синхронизированного S-входа. В силу симметрии схемы легко показать, что K-вход выполняет функции синхронизированного R-входа, переводя триггер в «0». Таким образом, при разных уровнях на J- и К-входах JK-триггер ведет себя как синхронный непрозрачный RS-триггер.

Существенно отличным от RS-триггера является поведение JK-триггера при J=K=1. Для RS-триггера такое сотояние входов запрещено. Диаграмма работы JK-триггера в этом режиме показана на рис. 4.5,б. При любом состоянии триггера сигналы обратной связи открывают для С-сигнала именно тот входной конъюнктор, пройдя через который, С-сигнал переведет триггер в противоположное состояние. Таким образом, при J=K=1 по спаду каждого С-сигнала JK-триггер меняет состояние своих выходов на противоположное. Это так называемый счетный режим, или Т-режим работы триггера (от toggle—кувыркаться).

Кратко функционирование JK-триггера описывается табл. 4.1. Новым символом в таблице является символ спада синхроимпульса, который изображается направленной вниз стрелкой. Таблица отражает тот факт, что для JK-триггера переключающей сущностью синхроимпульса является не уровень его, а перепад уровня.

Таблица 4.1.

| Режим | С | Jt | Kt | Qt+1 |

| Хранение | X | 0 | 0 |

|

| Сброс | ¯ | 0 | 1 | 0 |

| Установка | ¯ | 1 | 0 | 1 |

| Инверсия предыдущего состояния | ¯ | 1 | 1 |

|

Схема, близкая к показанной на рис. 4.5, а, лежит в основе триггера К155ТВ1. Эта микросхема имеет тройные конъюнктивные входы J и K, т.е. сам двухступенчатый триггер получает J или K сигнал лишь при совпадении единиц на всех трех J или K входах микросхемы. Условное обозначение двухступенчатого JK триггера, имеющего тройные входы, показано на рис. 4.5, в. Две буквы Т указывают на наличие двух ступеней. Вход С, реагирующий не на уровень потенциала С, а на его отрицательный перепад, выделен специальным значком. Вход, реагирующий именно на перепад, иногда называют динамическим.

Схема, близкая к показанной на рис. 4.5, а, лежит в основе триггера К155ТВ1. Эта микросхема имеет тройные конъюнктивные входы J и K, т.е. сам двухступенчатый триггер получает J или K сигнал лишь при совпадении единиц на всех трех J или K входах микросхемы. Условное обозначение двухступенчатого JK триггера, имеющего тройные входы, показано на рис. 4.5, в. Две буквы Т указывают на наличие двух ступеней. Вход С, реагирующий не на уровень потенциала С, а на его отрицательный перепад, выделен специальным значком. Вход, реагирующий именно на перепад, иногда называют динамическим.

4.1.4. Асинхронные входы триггеров

Непрозрачные триггеры кроме штатных входов - синхровхода С и управляющих входов D, J, K часто дополняют независимыми от них R и S входами. При этом схема строится так, что R и S входы имеют приоритет в своем воздействии на триггер по отношению к штатным входам, т. е. R или S входы устанавливают диктуемое ими состояние триггера независимо от сигналов, поступающих в это время на штатные входы, в том числе и на вход С. Поэтому такие R и S входы называют асинхронными. По окончании асинхронного сигнала установленное им состояние сохраняется вплоть до очередного активного фронта С-сигнала. По этому фронту триггер сработает уже в соответствии с этим установленным состоянием и с действующими в данный момент уровнями на штатных управляющих входах. Как правило, асинхронные входы имеют активный низкий уровень.

4.2. Регистры

4.2.1. Параллельные регистры

Параллельные регистры - это устройства, предназначенные для записи, хранения и выдачи информации, представленной в виде двоичных кодов. Для хранения каждого двоичного разряда в регистре используется одна триггерная ячейка.

Для запоминания многоразрядных слов необходимое число триггеров объединяют вместе и рассматривают как единый функциональный узел-регистр. Если регистр построен на триггерах-защелках, то его называют регистр-защелка. Типовыми внешними связями регистра являются информационные входы D;, вход сигнала записи (или загрузки) С, вход гашения R, выходы триггеров Q. В упрощенном варианте регистр может не иметь входа гашения и инверсных выходов.

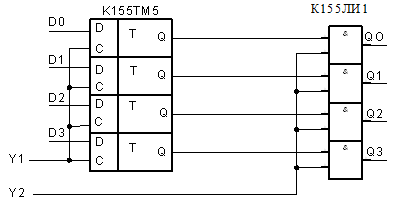

На рис. 4.6 показана схема четырехразрядного регистра, выполненного на ИМС К155ТМ5 и К155ЛИ1.

При подаче управляющего сигнала у1=1 информация по входам X1—Х4 записывается одновременно в соответствующие разряды четырех D-триггеров. При y1=y2=0 информация хранится в регистре памяти, а при y2=1 происходит параллельное считывание информации.

Рис.4.6. Четырехразрядный параллельный регистр

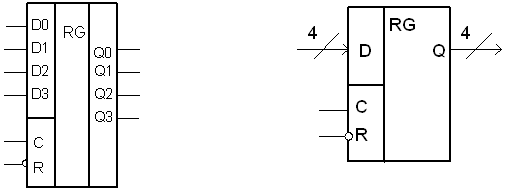

Условным изображением регистра по рис. 4.7, а пользуются тогда, когда на схеме необходимо показать каждый вход и выход данных. Если же тракт данных рассматривается как единое, укрупненное понятие - шина данных, то пользуются обозначением, показанным на рис 4.7, б.

|

а) б)

Рис. 4.7. Условное обозначение регистра

Выпускаемые промышленностью регистры иногда объединяют на кристалле микросхемы с другими узлами, в паре с которыми регистры часто используются в схемах цифровой аппаратуры. Пример такого комплексного узла - микросхема многорежимного буферного регистра (МБР) К589ИР12, основу которой составляет 8-разрядный регистр-защелка с входами DO—D7, С, R и восемью выходами Q0—Q7, снабженными усилителями мощности (буферами) с тремя состояниями выхода. Кроме того, в состав микросхемы входят несколько элементов управления. Усилители с тремя состояниями выхода имеет и 4-разрядный регистр К155ИР15, построенный на непрозрачных триггерах без свойств захвата или проницаемости, т. е. управляемых строго фронтом.

4.2.2. Регистровая память

Существуют микросхемы, в которых регистр объединен с входным мультиплексором, позволяющим принимать входные данные с двух и более направлений, выбираемых сигналами на адресных входах микросхемы. Объединяют регистр и с выходным демультиплексором, позволяющим передавать содержимое регистра на различные направления.

Сразу несколько регистров содержат микросхемы регистровой памяти (register memory, register file, сверхоперативная память). Входы Di регистров подключены к общей входной шине данных (data in). Вход загрузки требуемого регистра выбирается дешифратором записи на основании поступающего на его вход адреса записи (write address), т. е. кода номера загружаемого регистра. Запись данных, присутствующих на шине, происходит в момент поступления сигнала разрешения записи (write enable).

Выходы регистров мультиплексором подключаются к выходной шине (data out). Номер регистра, с которого происходит чтение, определяет код адреса чтения (read address). Выдачу данных разрешает сигнал разрешения чтения (read enable).

Поскольку дешифрация адреса записи и адреса чтения производится двумя независимыми узлами, имеющими автономные адресные входы, регистровая память может одновременно записывать число в один из регистров и читать число из другого.

Микросхемы регистровой памяти легко наращиваются по разрядности и допускают наращивание по числу регистров. Они разработаны для построения блоков регистров общего назначения (РОН) и других специализированных блоков памяти небольшого объема, предназначенных для временного хранения исходных данных и промежуточных результатов в цифровом устройстве.

По мере увеличения числа регистров памяти разработчики отказываются от независимой адресации регистров при записи и чтении. Остается лишь один комплект адресных входов и один дешифратор адреса, которые используются и при записи, и при считывании. Такую схему регистровой памятью уже не называют. По ЕСКД она обозначается RAM (random access memory, т. е. память с произвольным доступом). Используются также термины: запоминающее устройство с произвольной выборкой (ЗУПВ), оперативное запоминающее устройство (ОЗУ), оперативная память, а иногда - просто память. В микросхемах ЗУПВ ввод и вывод данных при записи и чтении могут осуществляться через одни и те же выводы корпуса за счет использования в тракте считывания элементов с тремя состояниями выхода или с открытым коллектором. Режимы работы микросхемы запись, чтение и хранение задаются комбинациями сигналов на ее входах управления. Если для ввода данных при записи и вывода их при чтении используются различные выводы корпуса (входы Di и выходы Qi), то режим хранения может быть совмещен с режимом чтения.

Микросхемы ОЗУ малой емкости часто выпускаются в составе распространенных серий. Они имеют входы адреса Аj, входы данных Di ; вход режима W/R: запись или чтение; выходы данных Qi; вход (или несколько конъюнктивных входов) разрешения Е, чаще называемый выбор кристалла ВК, выбор микросхемы ВМ или CS (chip select). Такую микросхему можно рассматривать как группу регистров, дешифратор для их выборки, цепи записи в регистры и считывания с них. Примерами подобных ИМС могут служить К155РУ2 емкостью 16х4 (16 слов по 4 разряда), К537РУ8 – 2Кх 8. Такие ОЗУ принято называть статическими. Наращивание разрядности и числа хранимых слов производится, как и в случае ПЗУ.

Микросхемы ЗУПВ большей емкости выпускают уже в составе определенных серий БИС памяти. Часто такие микросхемы имеют временную диаграмму с большим числом регламентированных интервалов, адрес может подаваться по частям, есть микросхемы, требующие регенерации хранимых данных (динамические ОЗУ - раздел 5).

4.2.3. Сдвигающие регистры

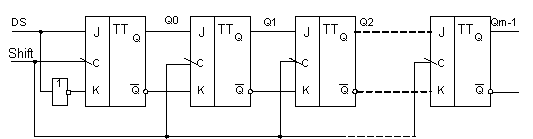

Сдвигающий, или сдвиговый регистр (shift register) это регистр, содержимое которого при подаче управляющего сигнала СДВИГ может сдвигаться в сторону старших или младших разрядов. Схема сдвигающего регистра из цепочки непрозрачных триггеров показана на рис. 4.8, а, а условное обозначение на рис.4.8, б.

|

а) б)

Рис.4.8. Сдвигающий регистр

Пусть на рисунке триггер Q0 – младший , Qm-1 – старший; вход каждого триггера (кроме Q0) подключен к выходу соседнего младшего триггера. Когда на все С входы триггеров поступает активный спад сигнала Shift, выход каждого триггера принимает состояние своего младшего соседа и, таким образом, информация, содержащаяся в регистре, сдвигается на один разряд в сторону старших разрядов, влево. Триггер Q0 принимает при этом состояние последовательного входа DS (data serial). Информация, поступившая на вход DS во время какого-либо такта, появится на выходе Qm-1 через m тактов.

Существенно, что в схеме использованы именно непрозрачные триггеры. Если поставить прозрачные защелки, то при активном уровне сигнала Shift все триггеры становятся прозрачными, и сигнал DS успеет пройти столько триггеров, сколько позволит длительность сигнала Shift .

Часто требуются более сложные регистры: с параллельной синхронной записью информации, реверсивные, с параллельно-последовательной записью. Такие регистры называются универсальными. Примером такого регистра служит ИМС К155ИР11. Регистр может работать в четырех режимах: параллельное занесение данных, сдвиг влево, сдвиг вправо, хранение данных.

Применения сдвиговых регистров очень разнообразны.

В арифметике сдвиг числа на один разряд влево соответствует умножению его на 2, сдвиг вправо – делению пополам.

В аппаратуре передачи данных универсальные регистры преобразуют параллельный код в последовательный и обратно. Передача данных последовательным кодом по сравнению с передачей параллельным существенно экономит число линий связи. Это покупается ценой увеличения времени обмена.

4.3. Счетчики

4.3.1. Общие понятия

Счетчик - это устройство для подсчета числа входных сигналов.

Как операционный элемент счетчик реализует преобразование число- импульсного кода в позиционный по некоторому основанию системы счисления. В ЭВМ счетчики используются для образования последовательности адресов команд, для счета количества циклов выполнения операций и т.д.

С точки зрения теории автоматов, счетчик - это цифровой автомат, внутреннее состояние которого является функцией количества поступивших входных сигналов.

Количество переключающих сигналов, которое надо подать на вход счетчика для того чтобы счетчик вернулся в исходное состояние, равное числу состояний счетчика, называется коэффициентом пересчета или модулем счетчика – Ксч . Счетчик называется двоичным, если Ксч = 2m, где т - целое число, m>0, и десятичным, если Ксч = 10p , где р - целое число, р > 0. Счетчики чаще всего строятся на триггерах различных типов, которые являются элементарными счетчиками с модулем 2.

Состояние счетчика в любой момент времени определяется кодом Q , который зафиксирован на его триггерах. Задать правила работы счетчика - значит тем или иным способом определить функцию Qn, = f(n), при п =0,1,2 ... Ксч , где Qn - состояние счетчика после n-го входного переключающего сигнала, n -номер входного переключающего сигнала. Очевидно, что Qp = Qp + Ксч при любом n .

Любой счетчик с модулем Ксч может быть использован как делитель частоты входных сигналов с коэффициентом деления Ксч .

По порядку изменения состояний могут быть счетчики с естественным и произвольным порядком счета. В первых счетчиках значение кода каждого последующего состояния отличается на 1 от кода предыдущего состояния.

По способу переключения триггеров во время счета счетчики делятся на асинхронные и синхронные. Первые называются еще счетчиками с последовательным переносом, т.к. переход каждого триггера из одного состояния в противоположное происходит последовательно во времени. Входной переключающий сигнал непосредственно воздействует лишь на первый триггер, и каждый триггер вырабатывает переключающий сигнал для следующего соседнего триггера.

Синхронные счетчики называются еще счетчиками с параллельным переносом, т.к. в них входной переключающий сигнал непосредственно воздействует на все триггеры счетчика, что обеспечивает одновременность переходов триггеров.

4.3.2. Асинхронные счетчики

|

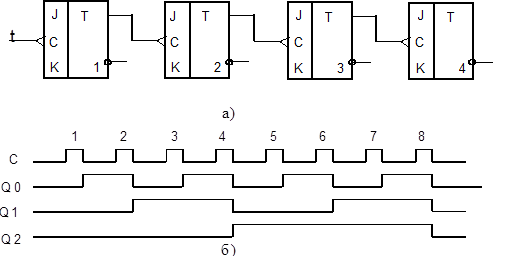

Рис. 4.9. Схема (а) и временные диаграммы (6) двоичного асинхронного суммирующего счетчика

На рис. 4.9, а изображен простейший способ включения триггеров, реализующий последовательный суммирующий счетчик. Показан трехразрядный счетчик с коэффициентом пересчета Ксч = 23 = 8, Следовательно, после подачи на вход восьми импульсов счетчик возвратится к исходному состоянию. Будем говорить, что подача на вход счетчика числа импульсов, превышающего Ксч -1 (в данном примере 7 ), вызывает переполнение счетчика.

Последовательный характер работы является причиной двух недостатков последовательного счетчика: меньшая скорость счета по сравнению с параллельными счетчиками и возможность появления ложных сигналов на выходе схемы.

Допустимая скорость счета в счетчиках обоих типов определяется максимальной скоростью переключения одного триггера.

Определяя максимальную скорость счета последовательного счетчика, следует учитывать наиболее неблагоприятный случай изменения состояния всех m триггеров. Суммарную продолжительность переходного процесса можно определить как сумму времен запаздывания отдельных элементов, соединяющих триггеры, и времен срабатывания всех триггеров. Найденное таким образом максимальное время перехода счетчика из одного состояния и другое следует считать предельным. Обычно реальное время перехода меньше предельного, так как в ряду последовательно включенных триггеров данный триггер начинает переход из одного состояния в другое еще до окончания переходного процесса в возбуждающем его элементе.

Последовательный характер переходов триггеров счетчика является источником ложных сигналов на его выходах. Например, в счетчике, ведущем счет в четырехразрядном двоичном коде с «весами» 8-4-2-1, при переходе от числа 0111 к числу 1000 на выходе появится следующая последовательность сигналов:

0111 ->0110 ->0100 ->0000 ->1000.

Это означает, что при переходе из состояния 7 в состояние 8 на выходах счетчика на короткое время появятся состояния 6; 4; 0. Эти дополнительные состояния могут вызвать неправильную работу других устройств.

4.3.3. Синхронные счетчики

|

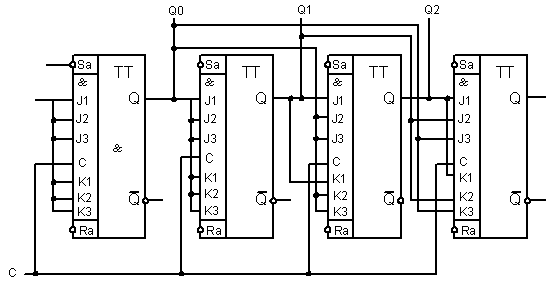

С целью уменьшения времени протекания переходных процессов схему, показанную на рис. 4.9, а, можно реализовать в варианте с подачей входных импульсов одновременно на все триггеры. В этом случае каждый триггер вырабатывает для всех последующих лишь сигналы управления, являющиеся логической функцией состояния счетчика и определяющие конкретные триггеры, которые изменяют состояние при данном входном импульсе. Принцип формирования этих сигналов следует из временной диаграммы на рис.4.9,б : триггер меняет состояние при поступлении очередного счетного импульса , если все предыдущие триггеры находились в состоянии 1. Отсюда и следует схема синхронного счетчика, показанная на рис.4.10.

Рис. 4.10 Четырехразрядный синхронный счетчик

Быстродействие счетчика характеризуется разрешающим временем, т.е. минимальным временным интервалом между входными сигналами, при котором счетчик еще правильно функционирует. Максимальная частота счета Fmax связана с разрешающим временем Тразр простым соотношением: Fmax = Т -1разр . Очевидно, что быстродействие синхронных счетчиков при прочих равных условиях всегда выше, чем асинхронных.

4.3.4. Интегральные счетчики.

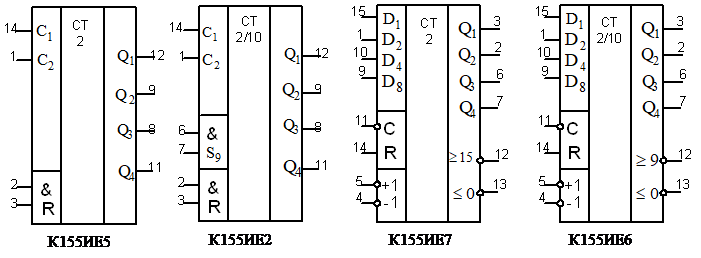

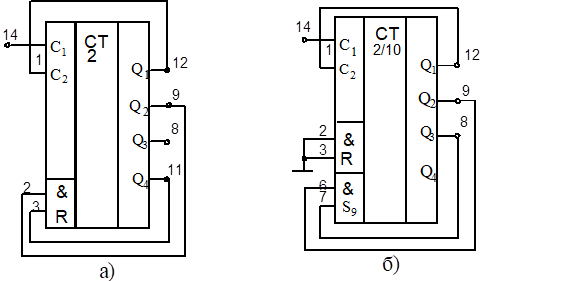

Интегральный двоичный асинхронный счетчик К155И.Е5 (рис.4.11) состоит из счетчика на 2 (триггер T1) и счетчика на 8 (триггеры Т2-Т4), соединение которых исходно отсутствует. Установка "0" производится, когда на входах R1 и R2 одновременно "1". Во время работы хотя бы на одном из входов должен быть "0". Для получения 4-х разрядного счетчика внешней перемычкой соединяют выход Q0 со входом C2.

Десятичные счетчики строят обычно на основе четырехразрядных двоичных счетчиков. Для того чтобы уменьшить Ксч четырехразрядного счетчика с 16 до 10, вводят дополнительные логические связи. При этом в зависимости от вида логической связи одним и тем же десятичным числам в разных счетчиках могут соответствовать различные двоичные кодовые комбинации или, иначе говоря, счетчики работают в различных двоично-десятичных кодах.

Рис. 4.11. Структура счетчика К155ИЕ5

Схема на рис.4.12 соответствует десятичному счетчику К 155 ИЕ 2, работающему в коде 8-4-2-1. Счетчик состоит из счетчика на 2 (триггер TI) и счетчика на 5 (триггеры Т2-Т4), соединение которых исходно отсутствует. Для образования десятичного счетчика выводы Q0 и C2 соединяются между собой. Счетчик имеет входы нетактируемой установки в "0" (0000) и в "9" (1001) - выводы R1,R2 и S1,S2. Во время счета хотя 6ы на одной из каждой пары входов должен быть "0".

Рис. 4.12. Структура счетчика К155ИЕ2

Условные обозначения асинхронных счетчиков К155ИЕ 5, К155ИЕ 2 и синхронных счетчиков К155ИЕ 7 и К155ИЕ 6 показаны на рис.4.13

Рис.4.13. Условные обозначения счетчиков.

К155ИЕ7. интегральный реверсивный двоичный синхронный счетчик имеет два счетных входа: вход суммирования +1 и вход вычитания –1.

Если все триггеры находятся в состоянии "1", то при приходе импульса на вход суммирования (+1) формируется сигнал "переноса" ( ( 15 ). Импульс на входе (-1), если все триггеры находятся в состоянии "0", формирует сигнал "заема" ( 0). Эти сигналы используются для увеличения разрядности счетчиков.

К155ИЕ6 –синхронный реверсивный десятичный счетчик, работающий в коде 8-4-2-1. Кроме двоичных реверсивных межтриггерных связей, в счетчике KI55 ИЕ б существуют дополнительные логические цепи, обеспечивающие недвоичный переход от кода 1001 к коду 0000 при суммировании и обратный переход при вычитании.

Сброс счетчиков KI55 ИЕ 6 и К155 ИЕ 7 производится сигналом "1", подаваемом на вход R Во время счета на этом выводе должен быть "0".

В обоих счетчиках триггеры имеют входы предварительной установки D, тактируемые потенциалом. В режиме счета сигнал на входе С (вывод 11) равен "1", цепи предустановки отключены. Если на входе С "0", то триггеры устанавливаются в состояния, соответствующие сигналам, поданным на входы D0 , D1 , D2 , D3. Естественно, что сигнал переноса в счетчике К 155 ИЕ 6 возникает на выходе ( 9) при состоянии счетчика 1001 и поступлении следующего счетного импульса.

4.3.5. Счетчики с различными коэффициентами пересчета.

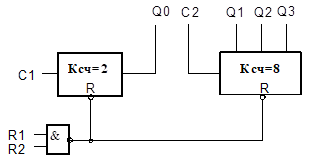

Счетчики с коэффициентами пересчета, отличающимися от двоичных и десятичных, могут быть также построены путем введения дополнительных связей в двоичные счетчики.

Однако существуют и общие методы построения счетчиков с любым заданным Ксч. Один из этих методов заключается в немедленном сбросе в "0" счетчика, установившегося в комбинацию, соответствующую числу Ксч . Если, например, нам нужно построить счетчик на 5, то, сбрасывая двоичный трехразрядный счетчик на "0" каждый раз, когда он будет принимать состояние 101, мы обеспечим возврат счетчика в исходное состояние после каждых пяти входных импульсов.

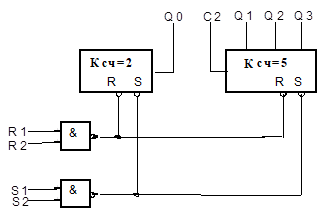

Подобный прием удобно применять при использовании счетчиков, имеющих элементы " И "на входах установки в "0" (К155ИЕ 5 и К155ИЕ 2) и в "9" (К155ИЕ 2). В качестве примера на рис.4.14 показаны соединения для получения Ксч = 10 для счетчика К155ИЕ 5 и Ксч = 7 для счетчика KI55ИЕ 2. В последнем случае из десяти состояний исключается три состояния (0110, 0111 и 1000).

При использовании синхронных счетчиков К155ИЕ б и К155ИЕ 7 для построения счетчиков с различными Ксч может использоваться метод начальной установки. Этот метод заключается в том, что счет каждый раз начинается не с нуля, как обычно, а с некоторого числа. Оно и определяет Ксч .

Рис. 4.14 а) Ксч = 10 б) Ксч = 7

4.3.6. Применение счетчиков

4.3.6.1. Счетчик событий.

События должны быть представлены импульсами с соответствующими логическими уровнями. Максимальное число событий должно быть не более Ксч -1, иначе произойдет переполнение счетчика.

4.3.6.2. Делитель частоты импульсов.

Любой счетчик с модулем Ксч может быть использован как делитель частоты входных сигналов с коэффициентом деления Ксч .

Если частота и период импульсов на входе счетчика Fвх и Tвх, то частота импульсов на выходе старшего триггера Fвых = Fвх / Kсч , а их период Tвых = Kсч . Tвх.

4.3.6.3. Счетчик команд (СК) в процессоре ЭВМ.

В качестве СК используется двоичный счетчик, разрядность которого равна разрядности шины адреса (ША), т.к. выходы его триггеров это линии адреса соответствующего разряда. СК должен иметь возможность не только последовательного счета, но и любого изменения текущего состояния для реализации условных и безусловных переходов в исполняемой программе.

4.3.6.4. Распределители импульсов (РИ).

РИ – устройство, распределяющее поток импульсов последовательно, импульс за импульсом, по нескольким выходам так, что результирующая временная диаграмма имеет вид, как на рис.4.15. Одно из главных применений РИ – системы обегающего контроля, где РИ управляют поочередным подключением однотипных датчиков ко входу измерителя .

РИ могут строиться по различным схемам. Чаще всего это двоичный счетчик с дешифратором (ДШ). Счетчик последовательно перебирает двоичные коды, ДШ в соответствии с ними последовательно возбуждает свои выходы. При этом нужно помнить, что ДШ будет расшифровывать не только верные, установившиеся состояния счетчика, но и неустановившиеся, ложные. В результате на выходах такого РИ кроме нормальных сигналов будут появляться короткие всплески напряжения (у ДШ с прямыми выходами) или короткие провалы до нуля (у ДШ с инверсными выходами). Эти сигналы отсутствуют при использовании синхронных счетчиков или их можно устранить, стробируя ДШ по входам разрешения и запрещая его работу на время существования ложного состояния счетчика.

Роль распределителя импульсов может выполнять и сдвиговый регистр с единственной двигающейся единицей.

1.4. Оперативные запоминающие устройства (ОЗУ)

4.4.1. Разновидности оперативной памяти

Оперативная память (Random Access Memory – RAM), т.е. память с произвольным доступом, используется центральным процессором для совместного хранения данных и исполняемого программного кода. По принципам хранения информации ОЗУ можно разделить на статические и динамические.

Оперативную память можно рассматривать как некий набор ячеек, каждая из которых может хранить один информационный бит.

В статических ОЗУ ячейки построены на различных вариантах триггеров. После записи бита в такую ячейку она может сохранять его сколь угодно долго – необходимо только наличие питания. Отсюда и название памяти – статическая, т.е. пребывающая в неизменном состоянии. Достоинством статической памяти является ее быстродействие, а недостатками – высокое энергопотребление и низкая удельная плотность данных, поскольку одна триггерная ячейка состоит из нескольких транзисторов и, следовательно, занимает на кристалле немало места. К примеру, микросхема емкостью 4 Мбит состояла бы более чем из 24 млн. транзисторов, потребляя соответствующую мощность.

Лекция "27 Молочно-белковые концентраты" также может быть Вам полезна.

В динамических ОЗУ элементарная ячейка представляет собой конденсатор, выполненный по КМОП – технологии. Такой конденсатор способен в течение нескольких миллисекунд сохранять электрический заряд, наличие которого можно ассоциировать с информационным битом. При записи логической единицы в ячейку памяти конденсатор заряжается, при записи нуля – разряжается. При считывании данных конденсатор разряжается, и если его заряд был ненулевым, то на выходе схемы считывания устанавливается единичное значение. Процесс считывания (обращения к ячейке) сочетается с восстановлением (регенерацией ) заряда. Если обращения к ячейке не происходит в течение длительного времени, то конденсатор за счет токов утечки разряжается и информация теряется. Для компенсации утечки заряда периодически циклически обращаются к ячейкам памяти, т.к. каждое обращение восстанавливает прежний заряд конденсатора. К достоинствам динамической памяти относятся высокая плотность размещения данных и низкое энергопотребление, а к недостаткам – низкое быстродействие по сравнению со статической памятью.

В настоящее время динамическая память (Dynamic RAM – DRAM) используется в качестве оперативной памяти компьютера, а статическая память (Static RAM – SRAM)- для создания высокоскоростной кэш – памяти процессора.

Микросхемы динамической памяти организованы в виде квадратной матрицы, причем пересечение строки и столбца матрицы задает одну из элементарных ячеек. При обращении к той или иной ячейке нужно задать адрес нужной строки и столбца. Задание адреса строки происходит, когда на входы микросхемы подается специальный стробирующий импульс RAS (Raw Address Strobe), а задание адреса столбца – при подаче импульса CAS (Column Address Strobe). Импульсы RAS и CAS подаются последовательно друг за другом по мультиплексированной шине адреса.

Регенерация в микросхеме происходит одновременно по всей строке матрицы при обращении к любой из ее ячеек, т.е. достаточно циклически перебрать все строки.

4.4.2. Построение блоков ОЗУ

В инженерной практике блоки ОЗУ приходится строить, главным образом, при проектировании или модификации микропроцессорных управляющих устройств. В этом случае блок обычно имеет небольшую емкость (порядка нескольких Кбайт) и строится на статических ОЗУ, например, серии К537.

Методика построения блоков ОЗУ при этом практически не отличается от методики построения блоков ПЗУ, изложенной в 3.4.2. Разница лишь в том, что ОЗУ, кроме режимов чтения и хранения, имеют режим записи. Поэтому при адресации ОЗУ надо кроме управляющего сигнала MR (чтение ЗУ) ввести в логику выбора сигнал MW (запись в ОЗУ). Для этого сигнала БИС ОЗУ имеют специальный вход.