Электронные цифровые устройства

Раздел 3. Электронные цифровые устройства

3.1. Основные логические понятия, типовые логические функции и элементы (И, ИЛИ, НЕ, И-НЕ, ИЛИ-НЕ, исключающее ИЛИ.

Элементы булевой алгебры

· Булевы константы («0» и «1»)

· Булевы переменные (Х1,Х2,…,Хn)Є{0,1}

· Булевы функции y=f(x1,x2,…,xn) принимают значения 0 и 1

В отличие от переменной в обычной алгебре логическая переменная имеет толькодва значения, которые обычно называются логическим нулем и логической единицей. В качестве бозначений используются «О» и «1» или просто 0 и 1.

Существуют три основные операции между логическими переменными: конъюнкция (логическое умножение), дизъюнкция (логическое сложение) и инверсия (логическое отрицание). По аналогии с алгеброй чисел в алгебре логики используются следующие обозначения операций.

Рекомендуемые материалы

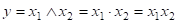

Конъюнкция

Дизъюнкция

Инверсия

Применительно к логическим операциям существуют теоремы:

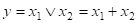

Коммутативный закон:

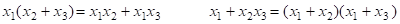

Ассоциативный закон:

Дистрибутивный закон:

Правило склеивания:

Правило повторения:

Правило отрицания:

Правило двойного отрицания:

Теорема де Мограна:

Операции с нулем и единицей:

Таблицы истинности логических функций

| x1 x2 | f1 | f2 | f3 | f4 | f5 | f6 | f7 | |

| 0 | 0 | 0 | 0 | 1 | 1 | 1 | 1 | 0 |

| 0 | 1 | 1 | 0 | 0 | 1 | 0 | 1 | 1 |

| 1 | 0 | 1 | 0 | 0 | 0 | 0 | 1 | 1 |

| 1 | 1 | 1 | 1 | 1 | 1 | 0 | 0 | 0 |

| Λ | V | ~ | → | ↓ | | | ⊕ |

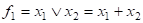

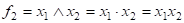

Дизъюнкция (логическое сложение, ИЛИ)

Конъюнкция (логическое умножение, И)

Равнозначность

Импликация

Функция Вебба (стрелка Пирса, ИЛИ-НЕ)

Функция Шеффера (И-НЕ)

Функция сложения по модулю два (полусумматор)

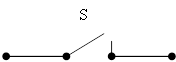

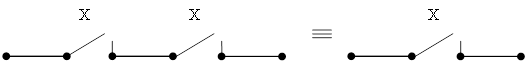

Как можно представить логические функции с помощью электрических переключающих схем? Так как логические переменные могут иметь только два дискретных значения, то следует обратить внимание на схемы, которые могут находиться в двух легко различимых рабочих состояниях. Простейшим способом реализации логической переменной является ключ.

Можно условиться, что разомкнутый ключ эквивалентен логическому нулю, а замкнутый –логической единице. Таким образом, ключ реализует переменную х, если он замкнут при х = 1, и переменную  , если он разомкнут при х = 1.

, если он разомкнут при х = 1.

Рассмотрим сначала, какая логическая функция будет реализована, если два ключа  и

и  соединить последовательно.

соединить последовательно.

Значение зависимой переменной у характеризуется тем, будет ли замкнута или разомкнута составная коммутируемая цепь, расположенная между входными клеммами. Очевидно, что рассматриваемая цепь будет замкнута только тогда, когда  и

и  замкнуты, т.е. равны единице. Таким образом, последовательное включение ключей реализует функцию И.

замкнуты, т.е. равны единице. Таким образом, последовательное включение ключей реализует функцию И.

Функция ИЛИ может быть получена, если ключи включить параллельно.

С помощью такой схемной логики можно наглядно показать справедливость ранее приведенных теорем. Рассмотрим это на примере правила повторения.

На рис. показана реализация обеих частей выражения правила повторения с помощью коммутируемой цепи. Легко заметить, что рассматриваемое тождество выполняется, поскольку два включенных последовательно ключа, замыкание и размыкание которых происходит одновременно, воздействуют на внешние цепи как один такой ключ.

Другой возможностью представления логических переменных является электрическое напряжение, имеющее два различных уровня: высокий и низкий. Этим уровням можно поставить в соответствие логические состояния 1 и 0. Эта система обозначений: высокий = 1 и низкий = 0 – называется позитивной логикой. Но возможна также и обратная система обозначений: высокий = 0 и низкий = 1, которая называется негативной логикой.

Основные логические функции могут быть реализованы с помощью соответствующих электронных схем. Эти схемы имеют один или несколько входов и один выход. Как правило, они называются логическими элементами. Уровень выходного напряжения определяется уровнями напряжения на входах и характером логической функции. Для реализации одной и той же логической функции существует большое число различных электронных схем. Поэтому с целью упрощения документации были введены символы, которые обозначают лишь только логическую функцию и не раскрывают внутреннее строение схемы.

В цифровой технике задача, как правило, формулируется в форме таблицы переключений, которая называется также таблицей истинности. Прежде всего требуется найти такую логическую функцию, которая соответствовала бы этой таблице. На следующем этапе эту функцию преобразуют в простейшую форму, которую потом реализуют с помощью соответствующей комбинации базовых логических схем. Логические функции записывают, как правило, в дизъюнктивной совершенной нормальной форме (ДСНФ). При этом поступают следующим образом.

1. В таблице истинности выделяют строки, в которых выходная переменная у имеет значение 1.

2. Для каждой такой строки составляют конъюнкцию всех входных переменно причем записывают сомножитель  , если рассматриваемая переменная принимает значение 1, в противном случае записывают

, если рассматриваемая переменная принимает значение 1, в противном случае записывают  . Таким образом, составляется столько произведений, сколько имеется строк с у = 1.

. Таким образом, составляется столько произведений, сколько имеется строк с у = 1.

3. Наконец, записывая логическую сумму всех найденных произведений, получают искомую функцию.

3.2. Схемная реализация логических элементов. Их основные параметры.

Эволюция цифровой логики:

1) РТЛ – резисторно-транзисторная логика.

2) ДТЛ – диодно-транзисторная логика.

3) ТТЛ –транзисторно-транзисторная логика.

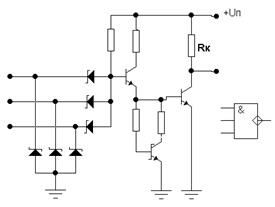

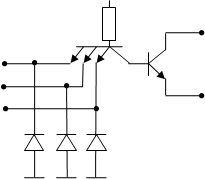

Элемент три «И-НЕ» на ДТЛ.

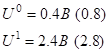

Напряжение <0.4B считается логическим нулем, при U>2.4 – логическая единица.

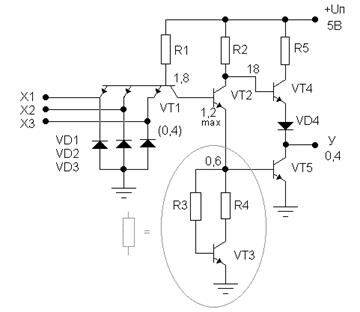

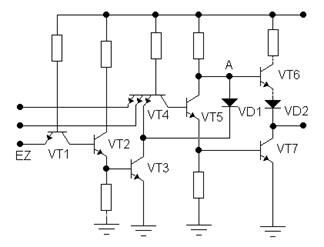

Элементы на основе ТТЛ.

В основе – многоэммитерный транзистор.

Серия 155.

Если на всех входах «1» , то на коллекторе  эмиттерный переход закрыт, а коллекторный открыт и напряжение на базе VT1=1.8 В. VT2 и VT5 открыты, VD4 –предназначен для надежного запирания VT4. R3, R4 и VT3 действуют как резистор и предназначены для увеличения помехоустойчивости.

эмиттерный переход закрыт, а коллекторный открыт и напряжение на базе VT1=1.8 В. VT2 и VT5 открыты, VD4 –предназначен для надежного запирания VT4. R3, R4 и VT3 действуют как резистор и предназначены для увеличения помехоустойчивости.

Если на любом из входов «0», то VT1 переключается из инверсного в активный режим и отпирается. В этом случае напряжение на его коллекторе (0,8В) уже недостаточно для отпирания VT4 и VT5. VT4 при этом открыт и на выходе появляется логическая единица.

R5 предназначен для защиты выходов при кратковременном замыкании на землю.

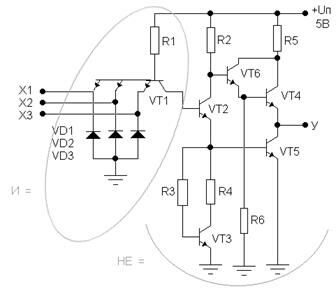

Серия повышенного быстродействия.

VT1, VT2 – VT5 – используются транзисторы Шотке.

Следующим шагом к повышению быстродействия стало использование транзистора Шотке.

Если на базу подать большое напряжение, то транзистор может войти в режим насыщения и его быстродействие уменьшается.

Если на базу подать большое напряжение, то транзистор может войти в режим насыщения и его быстродействие уменьшается.

У диода Шотке напряжение отпирания 0,3-0,4 В. Напряжение на базе транзистора Шотке не может превышать напряжение на его коллекторе более, чем на 0,4 В, т.е. коллекторный переход никогда полностью не открывается транзистор не заходит в режим насыщения, что резко увеличивает его быстродействие.

Каскад с открытым коллектором.

Обычная нагрузочная способность равна 10 входам, которые можно подключить к одному входу. Повышенная нагрузочная способность = 30. В логических элементах входы должны быть обязательно к чему-нибудь подключены. Если схема «И» – вход подключить к «1». Если «ИЛИ» – подать «0».

В схемах с общим коллектором неиспользуемые входы могут оставаться неподключенными.

Выходы двух обычных элементов объединять нельзя, за исключением находящихся в одном корпусе с целью увеличения выходной мощности. В схемах с общим коллектором можно объединять выходы и делать монтажные ИЛИ.

Недостаток: малый ток высокого уровня, ограниченный коллекторным резистором.

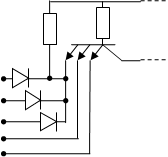

Расширение по «И».

См. на рисунках дополнительные входы.

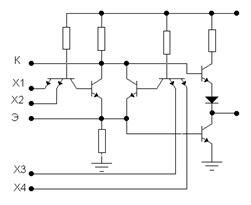

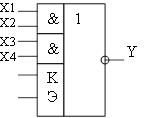

2И-2ИЛИ-НЕ

К и Э предназначены для расширения по ИЛИ.

Расширитель по ИЛИ.

Существуют элементы с открытым коллектором, допускающие подачу повышенного напряжения (15-30 В) через резистор на коллектор выходного транзистора, что позволяет коммутировать различную нагрузку.

Логические элементы с тремя выходными состояниями (Z-состояние).

Когда VT3 заперт, схема действует подобно обычному логическому элементу 2И-НЕ, т.к. VD1 смещен в обратном направлении. Если VT3 открыт, VD1 также открыт. U в точке А близко к нулю и VT6 заперт. VT5 также заперт, т.к. на эмиттере VT4, который связан с коллектором VT3, логический ноль. Следовательно, VT7 также заперт, и выходной вывод окажется отсоединенным от входных цепей и обеих шин питания. При этом уменьшается также потребляемая микросхемой мощность.

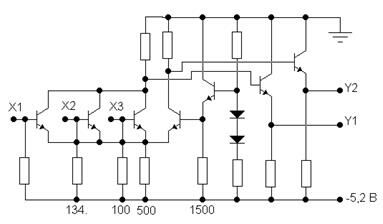

ЭСЛ – эмиттерно-связанная логика.

U0 = -0,7 ÷ -0,95 ≈ -0,8

U1 = -1,45 ÷ -1,95 ≈ -1,6

Высокое быстродействие достигается тем, что транзисторы дифференциального каскада и другие не входят в режим насыщения, а также малой разницей между уровнем логического «0» и логической «1» (0,8В). Последнее, в свою очередь, ухудшает помехоустойчивость. Для согласования микросхем различных видов логики используются микросхемы преобразования уровня.

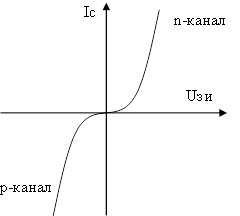

КМОП.

Стандартный КМОП допускает использование Uп от 5В до 15В. Быстродействие изменяется в три раза, возрастает и мощность. Это позволяет непосредственно соединить схемы КМОП и ОУ.

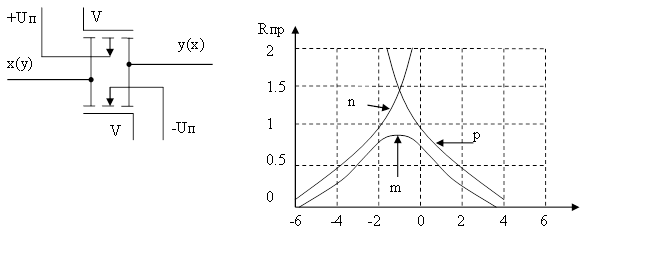

Двунаправленный ключ.

При изменении входного сигнала сопротивление каналов транзистора с n и p каналом изменяется в противоположную сторону. Специальные схемные решения позволяют сделать эквивалентное сопротивление ключа независимым от величины и направления входного сигнала. Величина сопротивления канала ключа достигает единиц Ом. При отсутствии отпирающего напряжения на затворе сопротивление велико (десятки МОм), что равносильно разрыву цепи. Омический характер сопротивления канала позволяет использовать двунаправленные ключи не только для переключения логических сигналов, но и (в отличие от ТТЛ) для переключения аналоговых сигналов, а также для регулировки последних, используя ключ в этом случае в качестве переменного резистора, управляемого напряжением.

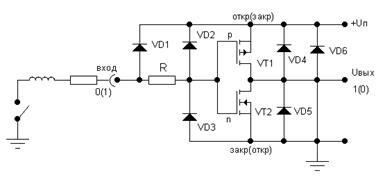

Инвертор КМОП

Защитные диоды обязательно присутствуют во всех логических элементах КМОП, так как они подвержены разрушающему воздействию статического электричества. В инверторе VD3, VD5, VD6 защитные элементы от отрицательных импульсов. Диоды VD1, VD2, VD4 защищают вход и выход от положительных выбросов и ограничивают его на уровне Uп+0,6. Для дополнительной защиты входов, особенно при длинных входных проводах, и для устранения паразитных колебаний последовательно с входом включают резистор для ограничения тока заряда включения емкости.

Сопряжение КМОП и ТТЛ.

При сопряжении КМОП и ТТЛ к выходу КМОП можно подключить два входа ТТЛ 155серии и до девяти входов 555 серии. При подключении выхода ТТЛ ко входу КМОП необходимо включить резистор с выхода ТТЛ на источник питания (2кОм) с целью повышения уровня логической «1».

Параметры цифровых элементов:

1)надежность – интенсивность отказов , наработкой на отказ Т, вероятность безотказной работы

, наработкой на отказ Т, вероятность безотказной работы  ;

;

2)стойкость к механическим и климатическим воздействиям - вибрации, ударам, центробежным силам, воздействиям атмосферы и т.д.

3) быстродействие – прямо пропорционально потребляемой мощности;

4) мощность рассеивания;

5) нагрузочная способность - при исполнении микросхем разных серий количество входов будет различным. Оно может быть указано в таблице, либо рассчитано по входным и выходным токам;

6) помехоустойчивость;

7) степень интеграции.

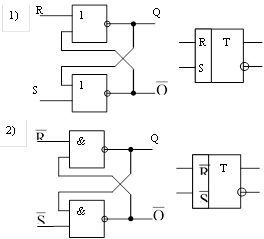

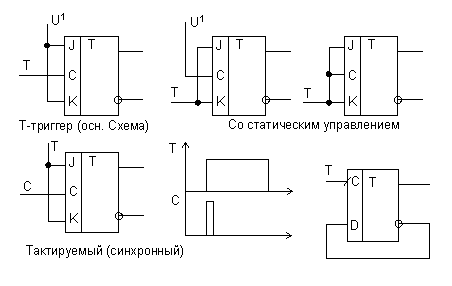

3.3. Триггеры: общая структура и классификация. Назначение и принцип действия триггеров типа: RS-, D-, JK-, Т-.

Разновидности функциональных схем:

- комбинационные схемы

- последовательные устройства

Комбинационные схемы характеризуются отсутствием памяти (память – свойство системы сохранять в течении требуемого времени значение сигнала, характеризующее внутреннее состояние цифрового устройства). Сигнал на выходе комбинационного устройства в любой момент времени однозначно определяется сочетанием сигналов на входе и не зависит от его предыдущего состояния. Схемным признаком таких схем является осуществление в цепи обратной связи. Примеры: логические элементы, эл. ключи, дешифраторы, арифметические устройства.

Последовательные схемы обладают памятью и при смене цифр на входе, для предсказания сигнала на выходе, необходимо знать о состоянии, в котором устройство было до этого. В этих устройствах есть обратная связь. Простейшие из них – триггеры, счетчики, резисторы, запоминающие устройства.

Триггеры – класс устройств, общим свойством которых является способность длительно оставаться в одном из двух (или нескольких возможных) устойчивых состояний и скачком чередовать их под воздействием внешних сигналов. Одно из основных применений – запоминание информации.

Под памятью триггера подразумевают способность оставаться в заданном состоянии и после прекращения действия переключающего сигнала. Приняв одно из состояний за «1», а другое за «0», можно считать, что триггер хранит или помнит один разряд двоичного числа.

|

|

| ||||

| Rn | Sn | Q |

| ||

| 1 | 0 | 0 |

|

| |

| 0 | 1 | 1 | 0 | ||

| 1 | 0 | 0 | 1 | ||

| 1 | 1 | н/о | н/о | ||

| 2 | 0 | 0 | н/о | н/о | |

| 0 | 1 | 1 | 0 | ||

| 1 | 0 | 0 | 1 | ||

| 1 | 1 |

|

| ||

Недостаток: неопределенное состояние.

Для исключения неопределенного состояния разработаны модификации RS-триггеров, у которых при запрещенных входных комбинациях выходной сигнал принимает следующие значения:

R-триггер - 0

S-триггер - 1

E-триггер – Qn

JK-триггер -

Триггерные системы - RS-триггер как ячейка памяти и УУ.

J, K, V, (T)C – внешние входы; Ra, Sa – внешние входы ячейки памяти; Q,  - внешние выходы; S', R' – внутренние входы.

- внешние выходы; S', R' – внутренние входы.

Функциональное назначение внешних входов

| усл. обозн. | назначение |

| информационные входы | |

| S | вход раздельной установки триггера в состоянии «1» |

| R | вход раздельной установки триггера в состоянии «0» |

| J | вход установки JK-триггера в состоянии «1» |

| K | вход установки JK-триггера в состоянии «0» |

| T | вход счетного триггера |

| D | вход установки D- или DV-триггера в состоянии «1» или «0» |

| управляющие входы | |

| V | подготовительный вход разрешения приема информации |

| C | вход синхронизации (тактирующий) |

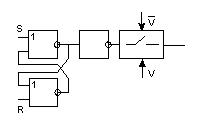

УУ – комбинационное устройство, преобразующее входную информацию в комбинацию сигналов под воздействием которых ячейка памяти принимает одно из двух устойчивых состояний. Изменяя схему УУ и способы ее связи с ячейкой памяти можно получить триггеры с различными функциональными свойствами. Сигнал на информационном входе определяется информацией, которая будет записываться с триггер. С помощью подготовительного сигнала можно в нужный момент прервать действие триггера или группы триггеров, сохраняя информацию на выходе (V-сигнал). Исполнительные сигналы (С-сигнал) задают момент приема входной информации и служат для синхронной работы ряда устройств, образующих функциональные узлы.

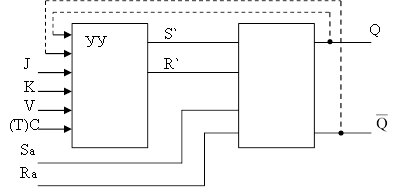

Асинхронные и синхронные триггеры

По способу ввода информации бывают асинхронные и синхронные триггеры.

Асинхронные триггеры имеют только информационный вход и срабатывают непосредственно за изменением сигналов на входе.

У синхронных триггеров смены информации на информационных входах недостаточно для срабатывания. Необходим дополнительный импульс, подаваемый на тактирующий вход.

Синхронные сигналы вырабатывают специальными генераторами тактирующих импульсов, которые задают частоту смены информации.

Основной недостаток – незащищенность перед опасными состязаниями сигналов, то есть возникновение временных сдвигов из-за различных задержек распространения сигнала, проходящего по различным цепям, низкая помехоустойчивость.

Срабатывание синхронных триггеров происходит при поступлении тактовых импульсов, длительность которых гораздо меньше их периода. В остальное время на входной сигнал триггер не реагирует, то есть, по сравнению с асинхронным, обладает более высокой помехоустойчивостью.

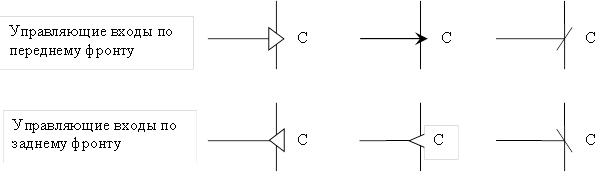

Способы управления, в зависимости от параметра синхронного входа сигнала, используемых для записи информации, триггеры бывают:

1) со статическим управлением записью (управление по уровню входного сигнала);

2) с динамическим управлением записью (по фронту или срезу);

3) двухступенчатое управление.

Способ управления со статическим управлением записью имеет недостаток – триггер в период действия синхронного импульса ведет себя подобно асинхронному. Срабатывает в момент, когда входной сигнал достигает порогового уровня, то есть продолжает действие тактового импульса. Смена сигнала на информационный вход вызывает новое срабатывание.

При динамическом управлении по фронту или по спаду тактового импульса триггер переключается только при переходе от 0 к 1, или от 1 к 0.

Возможность задержки момента опрокидывания триггера на время длительности тактового импульса позволяют по фронту производить считывание, а по срезу – запись информации.

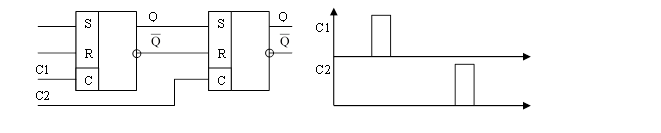

Двухступенчатые триггеры содержат две ячейки памяти, запись информации в которые происходит последовательно в различные моменты времени. Эту структуру называют «ведущий-ведомый» или MS-структура (Master-Slave).

Первая ступень – промежуточная запись входной информации. Вторая ступень – последовательная запись и хранение.

Формирование нового состояния происходит за два такта.

Ввод информации в ведущую ступень происходит с приходом С1. Перезапись соответственно из ведущего в ведомый – с приходом С2, в это же время происходит обновление информации на Q или  .

.

Управлять можно и одним тактовым импульсом. Запись в ведущую по фронту 0-1, перезапись в ведомую – по фронту 1-0.

Динамические двухступенчатые триггеры называют флип-флоп. Статические – лэт.

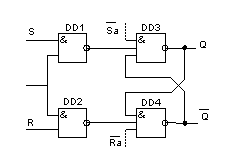

Асинхронные RS-триггеры.

|

|

| V |

|

| 0 | 0 | 1 |

|

| 0 | 1 | 1 | 0 |

| 1 | Х | 1 | 1 |

| Х | Х | 0 | Z |

X – не имеет значения

Z – высокоимпедансное значение выхода (выход отключен от обеих шин источника питания и выходных клемм)

Отсутствие запрещенного состояния обусловлено тем, что не введены выводы  .

.

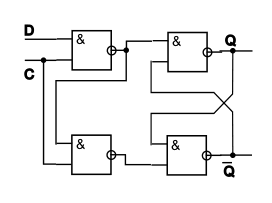

Синхронные RS-триггеры.

При С = 0 на выходах DD2 и DD1 логическая «1» и RS-триггер на DD3 и DD4 находится в состоянии хранения информации (и не реагирует на изменение R и S). При С = 1, информация на управляющих входах RS-триггера зависит от состояния входа R и S, проинвертированных DD2 и DD1. Входы Sa¯ и Ra¯ предназначены для асинхронной установки триггера в заданное состояние.

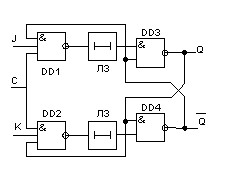

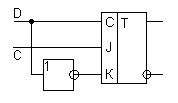

JK-триггеры

JK-триггеры не имеют неопределенных состояний. При всех входных комбинациях, кроме J = K = 1, они действуют подобно RS-триггеру. Причем J играет роль S, а К=R.

При J=K=1 в каждом такте происходит опрокидывание триггера и выходные сигналы меняют свое значение.

JK-триггеры относятся к универсальным устройствам (регистры, счетчики, делители), но кроме того, путем определенных соединений выводов, легко преобразуются в триггеры других типов.

По схеме JK-триггеры отличаются от RS-триггеров наличием обратной связи с выхода на вход, поэтому состояние JK-триггера зависит не только от сигналов на входах J и K, но и от логической связи с ними сигнала с выходов Q и Q¯. Элементы временной задержки играют роль стабилизированного состояния триггера и на его функциональные свойства не влияют. Назначение – создание временного сдвига между моментом ввода входной информации JnQn¯ или KnQn и начала выхода Qn+1 и Qn+1¯.

Без этих цепей во время действия комбинации Jn = Kn = 1 началась бы генерация для предотвращения которой задержка должна быть превыше длительности тактирующих импульсов.

Действие JK-триггера: Qn+1 = Jn Qn¯VKn¯Qn.

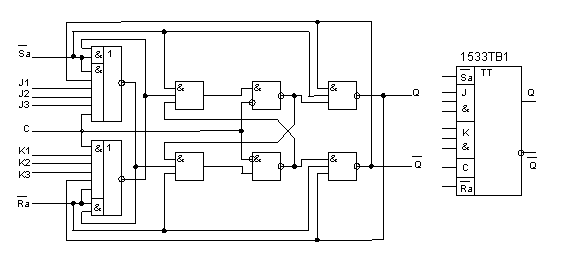

Триггер организован по принципу ведущий-ведомый и имеет по 3 входа J и K, связанных операцией &, синхронный вход С, а также асинхронные входы  и

и  для установки триггера в состояние «0» и «1» независимо от сигналов информационных и тактовых входов.

для установки триггера в состояние «0» и «1» независимо от сигналов информационных и тактовых входов.

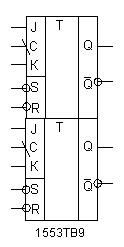

1553ТВ6 – 1553ТВ9

У ТВ6 отсутствует вход  , у ТВ10 отсутствует вход

, у ТВ10 отсутствует вход  . У ТВ11 объединены входы С и

. У ТВ11 объединены входы С и  для двух триггеров. У ТВ15 – вход

для двух триггеров. У ТВ15 – вход  , что позволяет преобразовывать эти триггеры путем объединения J и

, что позволяет преобразовывать эти триггеры путем объединения J и  .

.

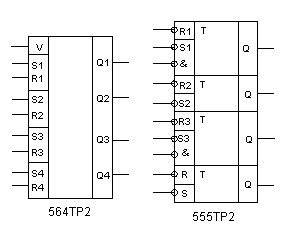

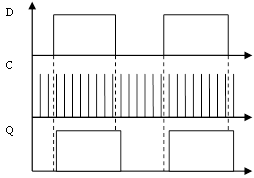

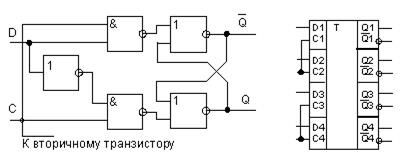

D-триггеры

D–триггеры имеют только один информационный вход. Сигнал на выходе Q в такте n+1 повторяет входной сигнал Dn в предыдущем такте n и сохраняет это состояние до следующего тактирующего импульса, то есть осуществляется задержка на один такт информации, существующей на входе D (Delay).

Qn+1 = Dn

ТМ7

D–триггеры серии ТМ7 со статическим управлением внутренними, объединенными попарно, синхронизирующими входами используются в качестве четырехразрядного регистра хранения информации с попарным тактированием разряда, а также в качестве буферной памяти и элемента задержки.

У ТМ5 отсутствует инверсный выход.

ТМ8 – с динамическим управлением.

T- и TV-триггеры.

T-триггер – счетный триггер, который имеет один информационный вход и меняет свое состояние всякий раз, когда меняет свое значение входной сигнал. В зависимости от того, фронт или срез используется для управления, считается, что триггер имеет прямой или инверсный вход. Единственный вид триггера, состояние которого определяется состоянием в предыдущем такте, а не от входной информации. Выполняет операцию сложения по модулю 2. Легко получается из D- или JK-триггера.

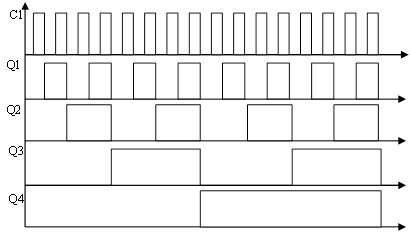

3.4. Счетчики. Назначение, устройство, классификация, принцип действия, область применения. Типовые интегральные схемы счетчиков.

Счетчиком называется устройство, сигналы на выходе которого в определенном коде отображают число импульсов, поступивших на счетный вход. Счетчик, образованный цепочкой из m триггеров может подсчитать в двоичном коде  импульсов. Каждый из триггеров называется разрядом счетчика. Число

импульсов. Каждый из триггеров называется разрядом счетчика. Число  называется коэффициентом или модулем счета.

называется коэффициентом или модулем счета.

Информация может сниматься с прямых и инверсных выходов триггеров. Когда число входных импульсов  , то при n входа равном Kсч происходит переполнение, счетчик возвращается в нулевое состояние и повторяет цикл. Каждый разряд счетчика делит частоту входных импульсов пополам. Для периодических сигналов

, то при n входа равном Kсч происходит переполнение, счетчик возвращается в нулевое состояние и повторяет цикл. Каждый разряд счетчика делит частоту входных импульсов пополам. Для периодических сигналов  .

.

Коэффициент счета называют коэффициентом деления, следовательно каждый счетчик может использоваться как делитель частоты.

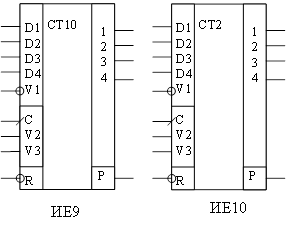

Обозначения:

СТ 2 – двоичный

СТ10 – двоично-десятичный

СТ2/10 – переключающийся

Основные параметры: емкость и быстродействие. Емкость численно равна коэффициенту счета и характеризует число импульсов, доступных счету за 1 цикл. Быстродействие определяется двумя параметрами: разрешающей способностью и временем установления.

Под разрешающей способностью подразумевают минимальное время между двумя сигналами, при которых еще не возникают сбои в работе tразр.сч.

Время установления кода tуст равно времени между моментом поступления входного сигнала и переходом счетчика в новое состояние.

Счетчики классифицируются следующим образом:

1) по модулю счета:

· двоичные

· двоично-десятичные

· с произвольным фиксированным модулем счета

· с переменным модулем

2) по направлению счета:

· суммирующие

· вычитающие

· реверсивные

3) по способу организации внутренних связей

· с последовательным переносом (асинхронные)

· с параллельным переносом (синхронные)

· с комбинированным переносом

· кольцевые

Классификационные признаки независимы и могут встречаться в разных комбинациях.

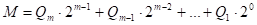

Число, записанное в счетчик, определяется по формуле:

где m – номер триггера,

Q – может принимать значение «1» и «0»,

– вес младшего разряда.

– вес младшего разряда.

Введением дополнительных логических связей (обратных и прямых) счетчики могут быть обращены в недвоичные, для которых  . Например, двоично-десятичные с Ксч=10 (двоичный по коду счета, десятичный по числу состояний). Организуется из 4-х разрядных двоичных путем исключения избыточных состояний за счет введения дополнительных связей. Когда счетчик используется в качестве делителя, направление счета роли не играет.

. Например, двоично-десятичные с Ксч=10 (двоичный по коду счета, десятичный по числу состояний). Организуется из 4-х разрядных двоичных путем исключения избыточных состояний за счет введения дополнительных связей. Когда счетчик используется в качестве делителя, направление счета роли не играет.

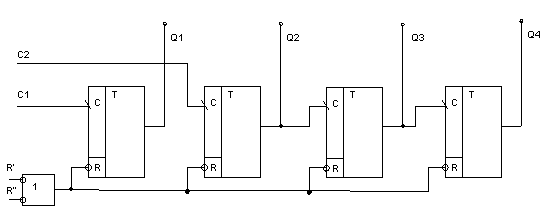

Счетчики с последовательным переносом представляют собой цепочку триггеров, в которых импульсы, подлежащие счету, поступают на вход 1-го триггера, а сигнал переноса передается последовательно от одного разряда к другому.

Достоинства: простота схемы и увеличение разрядности.

Недостатки: низкое быстродействие из-за последовательного принципа работы.

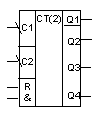

Счетчики с параллельным переносом.

У них счетные импульсы подаются одновременно на все тактовые входы, а каждый из триггеров цепочки служит по отношению к последующему только источником информационных сигналов. Срабатывание триггеров параллельного счетчика происходит синхронно, а задержка переключения всего счетчика равна задержке одно триггера.

В счетчике с параллельно-последовательным переносом триггеры соединены в группы так, что отдельные группы образуют счетчики с параллельным переносом внутри группы, а группы соединяются в счетчик с последовательным переносом. Общий коэффициент счета равен произведению коэффициентов счета всех групп.

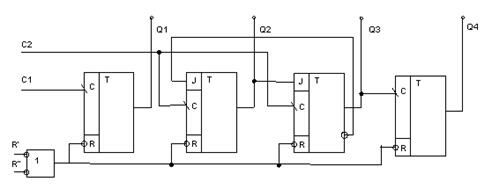

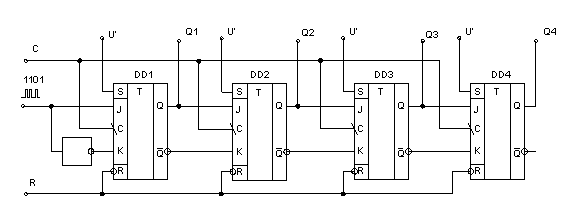

Счетчики ТТЛ с последовательным переносом

Состоят из 4-х одинаковых JK-триггеров, которые могут использоваться как по прямому назначению, так и в качестве ТК-триггеров. Переброс осуществляется по срезу. Три триггера соединяются в последовательную цепочку, 4-й самостоятельно.

К155ИЕ5

К155ИЕ4 (ИЕ5)

К155ИЕ4

К155ИЕ2

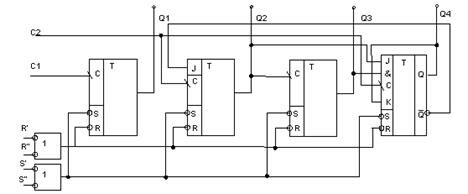

Счетчик ТТЛ с параллельным переносом

Двоично-десятичный суммирующий счетчик.

Имеет 4 входа предварительной установки счетчика при V1=0 независимо от предыдущего состояния и сигналов на входах С, V2, V3. При  происходит нормальный счет, причем переброс осуществляется по переднему фронту. Счет либо от нуля, либо от информации, записанной на входы D.

происходит нормальный счет, причем переброс осуществляется по переднему фронту. Счет либо от нуля, либо от информации, записанной на входы D.

При «1» на входе V3 на выходе Р формируется импульс логической «1» (перенос) с девятым входным импульсом.

V3 – разрешает перенос.

V2=0 – прерывает счет, однако информация на выходах при этом сохраняется.

V1 – предварительная запись.

3.5. Регистры. Принцип действия, область применения. Типовые интегральные схемы регистров.

Регистры – функциональные узлы, предназначенные для приема, хранения, передачи и преобразования информации.

Используются в качестве управляющих и запоминающих устройств генераторов и преобразователей кодов, счетчиков и делителей частоты, узлов временной задержки. Строятся на синхронных триггерах с динамическим или статическим управлением. Занесение информации в регистр называется операцией ввода или записью. Выдача информации к внешним устройствам характеризует операцию вывода или считывание. Запись информации в регистр не требует его предварительного обнуления.

Регистры делятся на:

· сдвигающие

· накопительные (памяти, хранения)

· универсальные.

Регистры памяти предназначены для хранения двоичной информации небольшого объема в течение короткого промежутка времени. Представляют собой набор синхронных триггеров, каждый из которых хранит один разряд двоичного числа. Ввод и вывод информации производится одновременно во всех разрядах параллельного кода. Ввод обеспечивается тактовым командным импульсом. Считывание может производиться в прямом и обратном коде (с инверсных выходов).

Регистры сдвига. Сущность сдвига – с приходом каждого тактового импульса происходит перезапись (сдвиг) содержимого триггера каждого разряда в соседний разряд без изменения порядка следования «0» и «1». При сдвиге вправо бит из более старшего разряда сдвигается в младший. При сдвиге влево – наоборот.

Сдвигающие регистры классифицируются:

1) по способу ввода и вывода информации на:

· параллельные

· последовательные

· комбинированные

2) по направлению сдвига на:

· однонаправленные

· реверсивные

Обозначаются: RG ←, → и ↔ (влево, вправо и реверсивные)

Универсальные в зависимости от управляющих сигналов могут выполнять как операцию хранения, так и сдвиг.

4-х разрядный сдвигающий регистр с последовательным вводом.

Допустим, что в регистр последовательно вводится начиная с младшего разряда двоичный код 1101, который поступает с внешнего устройства синхронно с тактовыми импульсами. С первым тактовым импульсом в триггер DD1 записывается «1» младшего разряда. Со следующим тактовым импульсом эта «1» будет сдвинута в триггер DD2 и окажется на его выходе. Одновременно в 1-ый триггер запишется «0». После 4-х тактовых импульсов параллельный код на выходах Q1—Q4 будет соответствовать последовательному входному. После пятого тактового импульса сигнал, бывший на выходе Q4 выводится из регистра и пропадает. После 8 тактов регистр полностью очищен.

Дополнительная логика позволяет вводить информацию параллельно и снимать последовательно.

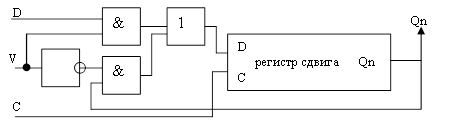

Сдвигающийся регистр может быть использован в качестве кольцевого счетчика или счетчика Джонса, который применяется для последовательного вывода информации без ее стирания.

Для этого информация с выхода регистра по цепи ОС снова вводится на вход. Пока на V единица, информация вводится в регистр по входу D и обратная связь не действует. За n тактов запоминается n разрядный код. Затем на V устанавливается «0» тактовыми импульсами по входу С. Информация с выхода Qn снова вводится в регистр одновременным последовательным (возможно и параллельным) считыванием и через n тактов находится в исходном состоянии.

К155ИР-1

Четырехразрядный регистр сдвига с последовательным или параллельным вводом информации и параллельным выводом (может быть и последовательным).

Четырехразрядный регистр сдвига с последовательным или параллельным вводом информации и параллельным выводом (может быть и последовательным).

Он может выполнять:

· ввод информации параллельным кодом

· ввод информации последовательным кодом со сдвигом влево

· ввод информации последовательным кодом со сдвигом вправо

· хранение.

Регистр имеет:

· 2 тактовых входа С1 и С2.

· управляющий вход выбора режима V2

· 5 информационных входов (V1 для ввода в последовательном коде, D1-D4 для записи в параллельном коде)

· 4 выхода Q1-Q4.

Ввод информации параллельным кодом осуществляется при V2=1 и C2=0. Сдвиг информации в триггерах происходит по перепаду 1-0 на С2. Входы V1 и C1 при этом блокированы. В этом же режиме по входам V2, С2 производится преобразование последовательного кода в параллельный со сдвигом влево. В этом случае поток информации происходит в обратном направлении. Для этого соединяют Q4 – D3, Q3 – D2, Q2 – D1. Информация подается на D4. Сдвиг влево по перепаду 1-0 на С2.

| V2 | V1 | С1 | С2 | |

| 1 | X | X | 1à0 | запись параллельного кода, сдвиг влево |

| 0 | вход | 1à0 | X | запись последовательного кода, сдвиг вправо |

Во избежание сбоев при смене состояний V2 должна происходить при C1=C2=0.

Ввод информации последовательным кодом: входная информация подается на V1, а тактовые импульсы на С1. Сдвиг вправо происходит при каждом перепаде 1à0 тактовых импульсов.

3.6. Шифраторы и дешифраторы. Назначение, устройство, область применения. Типовые интегральные схемы шифраторов и дешифраторов.

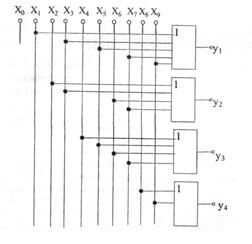

Шифратор — это комбинационное устройство, преобразующее десятичные числа в двоичную систему счисления, причем каждому входу может быть поставлено в соответствие десятичное число, а набор выходных логических сигналов соответствует определенному двоичному коду. Шифратор иногда называют «кодером» (от англ. coder) и используют, например, для перевода десятичных чисел, набранных на клавиатуре кнопочного пульта управления, в двоичные числа.

Если количество входов настолько велико, что в шифраторе используются все возможные комбинации сигналов на выходе, то такой шифратор называется полным, если не все, то неполным. Число входов и выходов в полном шифраторе связано соотношением п = 2т, где п — число входов, т — число выходов.

Рассмотрим пример построения шифратора для преобразования десятиразрядного единичного кода (десятичных чисел от 0 до 9) в двоичный код. При этом предполагается, что сигнал, соответствующий логической единице, в каждый момент времени подаётся только на один вход. Условное обозначение шифратора и таблица соответствия кода.

Схема такого шифратора, на элементах ИЛИ.

Схема такого шифратора, на элементах ИЛИ.

На практике часто используют шифратор с приоритетом. В таких шифраторах код двоичного числа соответствует наивысшему номеру входа, на который подан сигнал «1», т. е. на приоритетный шифратор допускается подавать сигналы на несколько входов, а он выставляет на выходе код числа, соответствующего старшему входу.

Рассмотрим в качестве примера шифратор с приоритетом (приоритетный шифратор) К555ИВЗ серии микросхем К555 (ТТЛШ). Шифратор имеет 9 инверсных входов, обозначенных через PRI,..., PR9. Аббревиатура PR обозначает «приоритет». Шифратор имен четыре инверсных выхода В1, ... , B8. Аббревиатура В означает «шина» (от англ. bus). Цифры определяют значение активного уровня (нуля) в соответствующем разряде двоичного числа. Например, В8 обозначает, что ноль на этом выходе соответствует числу 8. Очевидно, что это неполный шифратор.

входов, обозначенных через PRI,..., PR9. Аббревиатура PR обозначает «приоритет». Шифратор имен четыре инверсных выхода В1, ... , B8. Аббревиатура В означает «шина» (от англ. bus). Цифры определяют значение активного уровня (нуля) в соответствующем разряде двоичного числа. Например, В8 обозначает, что ноль на этом выходе соответствует числу 8. Очевидно, что это неполный шифратор.

Если на всех входах — логическая единица, то на всех выходах также логическая единица, что соответствует числу 0 в так называемом инверсном коде (1111). Если хотя бы на одном входе имеется логический ноль, то состояние выходных сигналов определяется наибольшим номе ром входа, на котором имеется логический ноль, и не зависит от сигналов на входах, имеющих меньший номер.

Например, если на входе PRI — логический ноль, а на всех остальных входах — логическая единица, то на выходах имеются следующие сигналы: В1 - 0, В2 -1, В4-1, В8 -1, что соответствует числу 1 в инверсном коде (1110).

Например, если на входе PRI — логический ноль, а на всех остальных входах — логическая единица, то на выходах имеются следующие сигналы: В1 - 0, В2 -1, В4-1, В8 -1, что соответствует числу 1 в инверсном коде (1110).

Основное назначение шифратора — преобразование номера источника сигнала в код (например, номера нажатой кнопки некоторой клавиатуры).

Для получения шифраторов с большим числом входов, т. е. наращивания размерности шифратора, объединяют микросхемы шифраторов с дополнительными выводами.

Дешифратором называется комбинационное устройство, преобразующее n-разрядный двоичный код в логический сигнал, появляющийся на том выходе, десятичный номер которого соответствует двоичному коду. Число входов и выходов в так называемом полном дешифраторе связано соотношением т = 2n, где п — число входов, а т — число выходов. Если в работе дешифратора используется неполное число выходов, то такой дешифратор называется неполным. Так, например, дешифратор, имеющий 4 входа и 16 выходов, будет полным, а если бы выходов было только 10, то он являлся бы неполным.

Обратимся для примера к дешифратору К555ИД6. Дешифратор имеет 4 прямых входа, обозначенных через А1, ..., A8. Аббревиатура А обозначает «адрес» (от англ. address). Указанные входы называю т адресными. Цифры определяют значения активного уровня (единицы) в соответствующем разряде двоичного числа.

т адресными. Цифры определяют значения активного уровня (единицы) в соответствующем разряде двоичного числа.

Дешифратор имеет 10 инверсных выходов Y0, ... ,Y9. Цифры определяют десятичное число, соответствующее заданному двоичному числу на входах. Очевидно, что этот дешифратор неполный.

Значение активного уровня (нуля) имеет тот выход, номер которого равен десятичному числу, определяемому двоичным числом на входе. Например, если на всех входах — логические нули, то на выходе Yo— логический ноль, а на остальных выходах — логическая единица. Если на входе А2 — логическая единица, а на остальных входах — логический ноль, то на выходе У2 — логический ноль, а на остальных выходах — логическая единица. Если на входе — двоичное число, превышающее 9 (например, на всех входах единицы, что соответствует двоичному числу 1111 и десятичному числу 15), то на всех выходах — логическая единица.

Помимо информационных имеется один или более входов, называемых входами разрешения, или адресными входами. Так, микросхема КР531ИД14 представляет собой два дешифратора 2 х 4, т. е. каждый дешифратор имеет два информационных входа и четыре инверсных выхода, а также инверсный вход разрешения.

Помимо информационных имеется один или более входов, называемых входами разрешения, или адресными входами. Так, микросхема КР531ИД14 представляет собой два дешифратора 2 х 4, т. е. каждый дешифратор имеет два информационных входа и четыре инверсных выхода, а также инверсный вход разрешения.

Цифры на входе (1,2) обозначают вес разряда двоичного числа, а цифры на выходе (0—3) определяют десятичное число, соответствующее заданному числу на входе.

При логической 1 на входе разрешения на всех выходах будут также логические 1. При активизации входа разрешения, т. е. при Е = 0, логический 0 появляется на том выходе дешифратора, номер которого соответствует десятичному эквиваленту двоичного числа, поданного на информационные входы. Благодаря наличию входа разрешения можно наращивать размерность дешифраторов. Так, используя 5 дешифраторов 2x4, можно построить дешифратор 4x16.

Очевидно, что если использовать две микросхемы КР531ИД14, т. е. четыре дешифратора 2x4, можно построить неполный дешифратор.

Дешифратор — одно из широко используемых логических устройств. Его применяют для построения различных комбинационных устройств.

Это основано на том обстоятельстве, что на выходе дешифратора вырабатываются все возможные логические произведения всех входных переменных (конъюнктивные минтермы).

Подключая к определенным выводам дешифратора логический элемент ИЛИ или используя дешифратор с открытым выходом и реализуя на нем «монтажное ИЛИ», можно реализовать любую логическую функцию.

3.7. Сумматоры. Назначение, устройство, классификация, принцип действия. Типовые интегральные схемы сумматоров.

Сумматоры –– функциональные узлы, выполняющие сложение чисел. Подразделяются на:

- комбинационные (нет памяти);

- накопительные.

Каждый из этих групп может быть последовательного и параллельного типа.

Сложение чисел в последовательных сумматорах осуществляется поразрядно последовательно во времени. В сумматорах параллельного типа сложение всех разрядов многоразрядных чисел происходит одновременно.

Как последовательные, так и параллельные сумматоры строятся на основе одноразрядных суммирующих схем. Сумматоры, выполненные в виде самостоятельных микросхем, являются комбинационными.

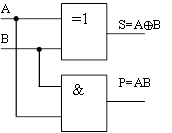

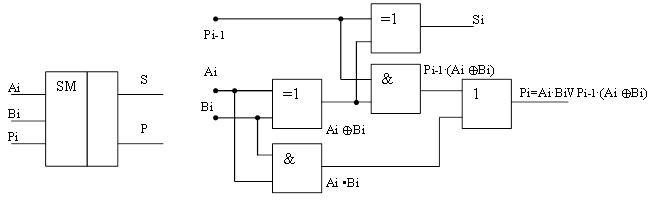

Полусумматор имеет 2 входа и 2 выхода. Используется для суммирования младших разрядов, т.к. не имеет выхода для переноса.

Полусумматор имеет 2 входа и 2 выхода. Используется для суммирования младших разрядов, т.к. не имеет выхода для переноса.

Полный сумматор состоит из двух полусумматоров: 1-й служит для сложения двух чисел, принадлежащих одному разряду, 2-й складывает промежуточную сумму с переносом. Входы можно менять местами.

Последовательный сумматор.

При последовательном вводе используется один полусумматор с дополнительной цепью задержки. Оба слагаемых в последовательном коде подаются на снимаются тоже в последовательном. Цепь задержки обеспечивает хранение импульса переноса на время одного такта, т.е. до прихода пары следующего разряда, с которым он будет просуммирован. Задержку обеспечивает D-триггер. Для хранения и ввода слагаемых А и В, а также для преобразования параллельного кода в последовательный и наоборот применяют регистр сдвига.

При последовательном вводе используется один полусумматор с дополнительной цепью задержки. Оба слагаемых в последовательном коде подаются на снимаются тоже в последовательном. Цепь задержки обеспечивает хранение импульса переноса на время одного такта, т.е. до прихода пары следующего разряда, с которым он будет просуммирован. Задержку обеспечивает D-триггер. Для хранения и ввода слагаемых А и В, а также для преобразования параллельного кода в последовательный и наоборот применяют регистр сдвига.

Достоинства: малые аппаратные затраты.

Недостатки: низкое быстродействие.

Разработаны схемы более быстродействующих сумматоров, например:

1) n-разрядный параллельный сумматор с последовательным переносом. Быстродействие его ограничено задержкой переноса, т.к. формирование сигнала переноса на выходе старшего разряда не может произойти до тех пор, пока сигнал переноса младшего разряда не распространится последовательно по всей системе.

2) n-разрядный параллельный сумматор с параллельным переносом с использованием специальных узлов блоков сквозного переноса.

Сумматоры ТТЛ.

Предназначен для построения многоразрядных схем сложения и вычитания с параллельной обработкой входной информации и последовательной передачей сигналов переноса. Для каждого слагаемого А и В имеется по 4 входа.

Предназначен для построения многоразрядных схем сложения и вычитания с параллельной обработкой входной информации и последовательной передачей сигналов переноса. Для каждого слагаемого А и В имеется по 4 входа.

Элементы входной логики объединены цепью монтажное &, поэтому сигналы на входы А3 и В3 должны поступать с устройств с открытыми коллекторами.

Благодаря усложненной входной логике, сумматор обладает большими функциональными возможностями. Многоразрядные сумматоры и вычитатели на его основе организуются без дополнительных элементов и могут работать в положительной и отрицательной логике. Удобен для схем с последовательным суммированием. Прямые и инверсные входы принадлежащие каждому из слагаемых одновременно не используются. Когда в работе А1, А2, В1, В2 на А3, А4, В3, В4 подаем высокий уровень. При использовании в качестве рабочих А3, А4, В3, В4 на остальные подаем «0».

| Входы | Выходы | ||||

| Ро | А | В |

|

| S |

| 0 | 0 | 0 | 1 | 1 | 0 |

| 0 | 0 | 1 | 1 | 0 | 1 |

| 0 | 1 | 0 | 1 | 0 | 1 |

| 0 | 1 | 1 | 0 | 1 | 0 |

| 1 | 0 | 0 | 1 | 0 | 1 |

| 1 | 0 | 1 | 0 | 1 | 0 |

| 1 | 1 | 0 | 0 | 1 | 0 |

| 1 | 1 | 1 | 0 | 0 | 1 |

К155ИМ2 – двухразрядный полный сумматор. К155ИМ3 – четырехразрядный полный сумматор.

Действие основано на параллельном суммировании данных в разных разрядах при последовательном переносе из разряда в разряд. Вход переноса оставлять открытым нельзя.

3.8. Цифроаналоговые и аналого-цифровые преобразователи.

Цифроаналоговые преобразователи (ЦАП) предназначены для преобразования цифровых сигналов в аналоговые. Такое преобразование необходимо, например, при восстановлении аналогового сигнала, предварительно преобразованного в цифровой для передачи на большое расстояние или хранения (таким сигналом, в частности, может быть звук). Другой пример использования такого преобразования — получение управляющего сигнала при цифровом управлении устройствами, режим работы которых определяется непосредственно аналоговым сигналом (что, в частности, имеет место при управлении двигателями).

К основным параметрам ЦАП относят разрешающую способность, время установления, погрешность нелинейности и др.

Разрешающая способность - величина, обратная максимальному числу шагов квантования выходного аналогового сигнала. Время установления - интервал времени от подачи кода на вход до момента, когда выходной сигнал войдет в заданные пределы, определяемые погрешностью. Погрешность нелинейности - максимальное отклонение графика зависимости выходного напряжения от напряжения, задаваемого цифровым сигналом, по отношению к идеальной прямой во всем диапазоне преобразования.

Как и рассматриваемые ниже аналого-цифровые преобразователи (АЦП), ЦАП являются «связующим звеном» между аналоговой и цифровой электроникой. Существуют различные принципы построения АЦП.

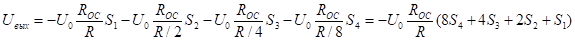

Схема ЦАП с суммированием весовых токов.

Ключ S5 замкнут только тогда, когда разомкнуты все ключи SI... S4 (при этом ивых=0). U0 - опорное напряжение. Каждый резистор во входной цепи соответствует определенному разряду двоичного числа.

Ключ S5 замкнут только тогда, когда разомкнуты все ключи SI... S4 (при этом ивых=0). U0 - опорное напряжение. Каждый резистор во входной цепи соответствует определенному разряду двоичного числа.

По существу этот ЦАП – инвертирующий усилитель на основе операционного усилителя. Так, если замкнут один ключ S1, то ивых = -U0 RОС /R, что соответствует единице в первом

и нулям в остальных разрядах.

Из анализа схемы следует, что модуль выходного напряжения пропорционален числу, двоичный код которого определяется состоянием ключей S1...S4. Токи ключей суммируются в точке «а», причем токи различных ключей различны (имеют разный «вес»). Это и определяет название схемы.

Из вышеизложенного следует, что

где Sj, i = 1, 2, 3, 4 принимает значение 1, если соответствующий ключ замкнут, и 0, если ключ разомкнут.

Состояние ключей определяется входным преобразуемым кодом.

Наиболее распространёнными являются ЦАП серий микросхем 572, 594, 1108, 1118 и др.

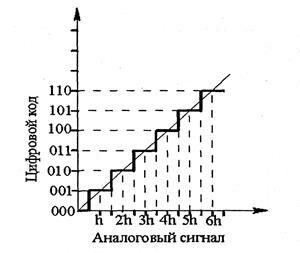

Аналого-цифровые преобразователи (АЦП) — это устройства, предназначенные для преобразования аналоговых сигналов в цифровые. Для такого преобразования необходимо осуществить квантование аналогового сигнала, т. е. мгновенные значения аналогового сигнала ограничить определенными уровнями, называемыми уровнями квантования.

Характеристика идеального квантования имеет вид, приведенный на рис.

Квантование представляет собой округление аналоговой величины до ближайшего уровня квантования, т. е. максимальная погрешность квантования равна +0,5h (h — шаг квантования).

К основным характеристикам АЦП относят число разрядов, время преобразования, нелинейность и др. Число разрядов — количество разрядов кода, связанного с аналоговой величиной, которое может вырабатывать АЦП. Часто говорят о разрешающей способности АЦП, которую определяют величиной, обратной максимальному числу кодовых комбинаций на выходе АЦП. Так, 10-разрядный АЦП имеет разрешающую способность (210 = 1024)-1, т. е. при шкале АЦП, соответствующей 10 В, абсолютное значение шага квантования не превышает 10 мВ. Время преобразования - интервал времени от момента заданного изменения сигнала на входе АЦП до появления на его выходе соответствующего устойчивого кода.

Характерными методами преобразования являются следующие: параллельного преобразования аналоговой величины и последовательного преобразования.

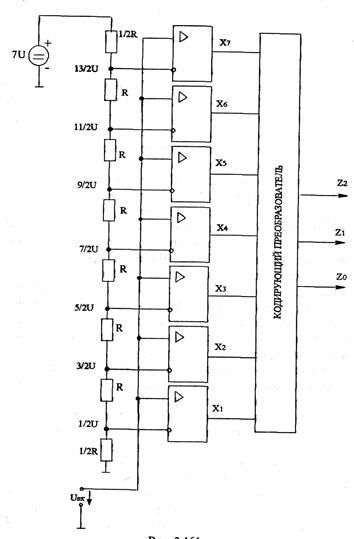

Рассмотрим АЦП с параллельным преобразованием входного аналогового сигнала. По параллельному методу входное напряжение одновременно сравнивают с п опорными напряжениями и определяют, между какими двумя опорными напряжениями оно лежит. При этом результат получают быстро, но схема оказывается достаточно сложной.

Рассмотрим принцип действия такого АЦП. При Uвх = 0, поскольку для всех ОУ разность напряжений (U+ - U-)< 0, напряжения на выходе всех ОУ равны - Епит, а на выходах кодирующего преобразователя (КП) Z0, Z„ Z2 устанавливаются нули. Если UВX>0,5 U, но меньше 3/2 U, лишь для нижнего ОУ U+ - U_ > 0 и лишь на его выходе появляется напряжение +ЕПШ, что приводит к появлению на выходах КП следующих сигналов: Z0 = 1, Z2 = Z, = 0. Если UBX > 3/2 U, но меньше 5/2 i/, то на выходе двух нижних ОУ появляется напряжение +Епит, что приводит к появлению на выходах КП кода 010, и т. д.

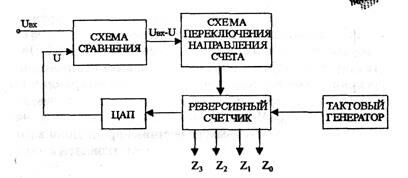

Рассмотрим конкретный вариант АЦП с последовательным преобразованием входного сигнала (последовательного счета), который называют АЦП со следящей связью. В АЦП рассматриваемого типа используются ЦАП и реверсивный счетчик, сигнал с которого обеспечивает изменение напряжения на выходе ЦАП. Настройка схемы такова, что обеспечивается примерное равенство напряжений на входе UBX и на выходе ЦАП — U. Если входное напряжение Um больше напряжения U на выходе ЦАП, то счетчик переводится в режим прямого счета и код на его выходе увеличивается, обеспечивая увеличение напряжения на выходе ЦАП. В момент равенства UBX и U счет прекращается и с выхода реверсивного счетчика снимается код, соответствующий входному напряжению.

Наиболее распространёнными являются АЦП серий микросхем 572, 1107, 1138 и др.

3.9. Запоминающие устройства: назначение, принцип построения и программирования. Типовые интегральные схемы.

Цифровыми запоминающими называют устройства, предназначенные для записи, хранения и считывания информации, представленной в цифровом коде. Запоминающие устройства (ЗУ) классифицируют по назначению, технологии изготовления, способу адресации, способу хранения информации и т.д. По назначению запоминающие устройства подразделяют на оперативные запоминающие устройства (ОЗУ) и постоянные запоминающие устройства (ПЗУ). ОЗУ обеспечивает режим записи, хранения и считывания информации в процессе ее обработки. ПЗУ в рабочем режиме допускает только считывание информации.

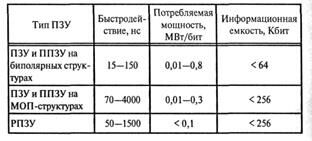

По технологии изготовления ЗУ делятся на биполярные (ТТЛ-,ТТЛШ-, ЭСЛ-, И2Л-технологии) и униполярные (n-МОП, КМОП- и другие технологии).

По способу адресации все ЗУ делятся на адресные и безадресные (ассоциативные). В адресных ЗУ обращение к элементам памяти производится в соответствии с их адресом, задаваемым двоичным кодом. Большинство ЗУ являются адресными. В ассоциативных ЗУ считывание информации осуществляется по ее содержанию и не зависит от физических координат элементов памяти. Ассоциативные ЗУ не имеют входов адресных сигналов.

К основным параметрам ЗУ относятся информационная емкость, потребляемая мощность, время хранения информации, быстродействие и др.

Информационная емкость определяется числом ячеек памяти ЗУ и указывает максимальный объем хранимой информации. Если ЗУ рассчитано на хранение п чисел (слов), каждое из которых имеет т разрядов, то информационная емкость N определяется выражением N = п • т. Так, например, если ЗУ предназначено для хранения 16 слов, каждое из которых содержит 4 разряда, то ЗУ имеет структурную организацию 16 х 4 и информационную емкость N = 16x4 = 64 бит. ЗУ емкостью 64 бит может быть организовано и как ЗУ 32 х 2 (32 слова по 2 разряда каждое). Емкость часто выражают в байтах (1 байт = 8 бит). Емкость ЗУ составляет от нескольких десятков до нескольких миллионов бит.

Потребляемая мощность - мощность, потребляемая ЗУ в установившемся режиме работы.

Время хранения информации - интервал времени, в течение которого ЗУ сохраняет информацию в заданном режиме.

Быстродействие - промежуток времени, необходимый для записи или считывания информации.

Основой любого ЗУ является матрица памяти (накопитель).

Запоминающие устройства с произвольным доступом, т. е. адресные запоминающие устройства, несмотря на большое разнообразие вариантов их реализации, имеют много общего в структуре их построения. Следует отметить, что так называемые динамические ОЗУ имеют свою особенность структуры.

Рассмотрим наиболее характерные структуры запоминающих устройств, которые подразделяют на ЗУ:

• с одномерной адресацией (или структуры 2D и 2DM, или со словарной организацией накопителей);

• с двумерной адресацией (или структуры 3D, или с матричной организацией накопителей).

Структура ЗУ с одномерной адресацией представляет собой матрицу, число строк которой соответствует числу хранимых слов п, а число столбцов — их разрядности т (ЗЭ — запоминающий элемент).

Структура ЗУ с одномерной адресацией представляет собой матрицу, число строк которой соответствует числу хранимых слов п, а число столбцов — их разрядности т (ЗЭ — запоминающий элемент).

Дешифратор DC служит для выбора того или иного слова, разрешая доступ ко всем запоминающим элементам (ЗЭ) выбранной строки. Далее в зависимости от режима работы ЗУ осуществляется либо считывание информации из ячеек выбранной строки, либо запись информации в ячейки выбранной строки. Рассмотренную структуру называют структурой 2D и основным недостатком такой структуры является значительное увеличение количества выходов дешифратора при наращивании объема памяти.

Так, для ЗУ с организацией 4x4 требуется дешифратор с четырьмя выходами, а для ЗУ с организацией 256 х 4 требуется дешифратор, имеющий 256 выходов, что сильно усложняет аппаратную реализацию.

Избежать этого можно, если использовать матрицу, длина строки которой многократно превышает разрядность хранимых слов. Это ведет к уменьшению числа строк матрицы, а следовательно, к уменьшению числа выходов дешифратора. Из выбранной строки матрицы затем выбирается ее часть, соответствующая тому или иному слову.

Структура такого ЗУ (структура 2DM) содержит дешифратор для выбора строки матрицы и мультиплексоры для выбора разрядов слова.

Структура такого ЗУ (структура 2DM) содержит дешифратор для выбора строки матрицы и мультиплексоры для выбора разрядов слова.

Адресный код для выбора того или иного слова в ЗУ содержит к + I разрядов. Часть их к используется для выбора строки матрицы из 2к строк, а другая часть / используется для выбора нужного слова в данной строке. Длина строки равна т 21, где т — разрядность хранимых слов.

На выходах m мультиплексоров формируется выходное слово, каждый разряд которого выбирается из отрезка строки длиной 2l.

Так, для ЗУ с организацией 256 х 4 согласно описанному принципу можно использовать матрицу размером 32х32 элемента, для доступа к каждому запоминающему элементу которого необходимо восьмиразрядное адресное слово. Пять разрядов этого слова, поступая на дешифратор адреса, выбирают одну из 32 строк матрицы. Три другие разряда адресного слова, поступая на адресные входы четырех мультиплексоров, выбирают из отрезков длиной

21 = 8 разрядов один бит каждого слова.

Описанные структуры целесообразно использовать для одновременной записи или считывания слов большой разрядности.

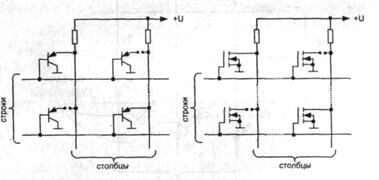

Рассмотрим ЗУ с двумерной адресацией, которая позволяет осуществлять побитовую запись или считывание информации. ЗУ с такой структурой осуществляют двухкоординатную выборку запоминающих элементов матрицы, что позволяет упростить дешифраторы адреса, т. е. уменьшить число выходов дешифратора.

Адресный код разрядностью к + l делится на две части: одна (А: разрядов) служит для определения строки, вторая (l разрядов) — для определения столбца. Таким образом, выбирается один бит нужного слова, находящийся в 3Э на пересечении активных выходов обоих дешифраторов. При построении ЗУ для многоразрядных слов к дешифраторам DC1 и DC2 подключаются параллельно несколько матриц М, число которых равно разрядности хранимых слов.

Адресный код разрядностью к + l делится на две части: одна (А: разрядов) служит для определения строки, вторая (l разрядов) — для определения столбца. Таким образом, выбирается один бит нужного слова, находящийся в 3Э на пересечении активных выходов обоих дешифраторов. При построении ЗУ для многоразрядных слов к дешифраторам DC1 и DC2 подключаются параллельно несколько матриц М, число которых равно разрядности хранимых слов.

Так, для ЗУ с организацией 256 х 4 требуется 4 матрицы, каждая из которых содержит 16 строк и 16 столбцов. Таким образом, дешифраторы имеют гораздо меньшее число выходов, чем в ЗУ с одномерной адресацией.

ОЗУ (их обозначают английской аббревиатурой RAM) подразделяются на статические и динамические. В статических ОЗУ запоминающая ячейка представляет собой триггер на биполярных или полевых транзисторах, что определяет потенциальный характер управляющих сигналов и возможность считывания информации без ее разрушения. Статические ОЗУ выполняются по различным технологиям (ТТЛ, ЭСЛ, КМОП, w-МОП, И2Л) и обладают теми же достоинствами и недостатками, что и элементы, изготовленные по той или иной технологии. Так, для получения высокого быстродействия статические ОЗУ выполняются по ЭСЛ-технологии, а И2Л-технология позволяет увеличивать функциональную плотность ЗУ в несколько раз по сравнению с ТТЛ-технологией. В последнее время интенсивно развиваются статические ОЗУ по КМОП-технологии.

несколько раз по сравнению с ТТЛ-технологией. В последнее время интенсивно развиваются статические ОЗУ по КМОП-технологии.

Среди отечественных серий микросхем статических ОЗУ серии К500, К1500 выполнены по ЭЛС-технологии, К132, К1809 - по и-МОП-технологии, К176, К561, К573, К581 — по КМОП-технологии, К555 — по ТТЛ-технологии, К541, К185 — по И2Л-технологии.

Благодаря высокому быстродействию статические ОЗУ широко используются в КЭШ-памяти. КЭШ-память (или буферная память) предназначена для запоминания копий информации, передаваемой между различными устройствами, прежде всего между процессором и основной памятью различных вычислительных устройств.

КЭШ-память имеет небольшую информационную емкость по сравнению с основной памятью, но более высокое быстродействие и особенно эффективна, когда требуется многократное использование одних и тех же данных.

Так например, микросхема К1500 представляет собой статическое ОЗУ, выполненное по ЭЛС-технологии, имеющее организацию 64 х 4 и предназначенное для построения локальных и буферных ОЗУ (КЭШ-память).

В динамических ОЗУ элементом памяти является емкость (например, входная емкость полевого транзистора), что требует периодического восстановления (регенерации) записанной информации в процессе ее хранения.

ОЗУ динамического типа позволяют реализовать большой объем памяти, но они сложнее в использовании, так как необходимо наличие специальной схемы управления режимами работы. В современных динамических ОЗУ имеются встроенные системы регенерации и синхронизации. Такие ОЗУ по внешним сигналам управления не отличаются от статических ОЗУ.

В обозначении микросхем после номера серии идут две буквы РУ, относящие микросхемы к виду ОЗУ.

В обозначении микросхем после номера серии идут две буквы РУ, относящие микросхемы к виду ОЗУ.

Плотность упаковки элементов памяти динамических ОЗУ в несколько раз превышает плотность упаковки в статических ОЗУ, т. е. они имеют большую информационную емкость. Они в несколько раз дешевле статических ОЗУ.

Динамические ОЗУ имеют ряд особенностей, существенно отличающих их от статических, одной из которых является использование в них последовательной адресации.

К динамическим ОЗУ относятся микросхемы серии К565.

Выводы микросхем имеют следующие назначения: CS — выбор микросхемы, А; — адресные входы, DI, —информационные входы, DO; — информационные выходы, W/R — разрешение записи/считывания, RAS — строб адреса строки, CAS — строб адреса столбца, СЕ — сигнал разрешения.

Микросхема К155РУ2 — это статическое ОЗУ с открытым коллекторным выходом — выполнена на основе ТТЛ-структур емкостью 64 бит. Имеет структуру 16 х 4, т. е. может хранить 16 слов длиной 4 разряда каждое.

Микросхема К537РУ8 — это статическое ОЗУ объемом 2 Кбайта, выполнена на основе структур КМОП, по входу и выходу совместима с ТТЛ-структурами. Имеет двунаправленную 8-разрядную шину данных, которая используется и для записи, и для считывания информации.

Микросхема К565РУ5 — это динамическое ОЗУ на основе и-МОП-структур, по входам и выходам совместима с ТТЛ-структурами, имеет организацию 64Кх 1. Шина адреса работает в мультиплексном режиме. Вначале на ней выставляются адреса строк, которые запоминаются во внутреннем регистре по спаду сигнала RAS. Затем выставляются адреса столбцов, которые запоминаются по спаду сигнала CAS.

Микросхемы К537РУ8 и К565РУ5 имеют выходы с тремя состояниями.

Все ПЗУ можно разделить на следующие группы:

• программируемые при изготовлении (обозначают как ПЗУ или ROM);

• с однократным программированием, позволяющим пользователю однократно изменить состояние матрицы памяти электрическим путем по заданной программе (обозначают как ППЗУ или PROM);

• перепрограммируемые (репрограммируемые), с возможностью многократного электрического перепрограммирования, с ультрафиолетовым (обозначают как РПЗУУФ или EPROM) или электрическим (обозначают как РПЗУЭС или EEPROM, или E2PROM) стиранием информации. Для обеспечения возможности объединения по выходу при наращивании памяти все ПЗУ имеют выходы с тремя состояниями или открытые коллекторные выходы.

В запоминающие устройства, программируемые при изготовлении (ПЗУ или ROM), информация записывается непосредственно в процессе их изготовления с помощью фотошаблона, называемого маской, на завершающем этапе технологического процесса.

Такие ПЗУ называются масочными ПЗУ, они могут быть построены на диодах, биполярных или МОП-транзисторах.

Если соединительный транзистор в данных схемах выполнен полностью (без разрыва), то при подаче на соответствующую строку сигнала активного уровня этот транзистор открывается и на столбце, к которому он подключен, появляется логический 0. Если транзистор не подключен к соответствующему столбцу, то активизация соответствующей строки не приводит к закорачиванию столбца и на нем остается логическая 1.

К масочным ПЗУ относят микросхемы серий 155, 568, 1656, 541, 555, 1656, 1801 и др., выполненные по технологии ТТЛ, ТТЛШ, и-МОП, КМОП. Для обозначения данного вида ПЗУ после номера серии помещают две буквы РЕ. Так, микросхемы К155РЕ21 и К155РЕ22 предназначены для воспроизведения соответственно букв русского (за исключением буквы Ъ) и латинского алфавитов, а также некоторых знаков.

В ППЗУ накопитель часто построен на запоминающих ячейках с плавкими перемычками, изготовленными из нихрома или других тугоплавких материалов. Процесс записи состоит в избирательном пережигании плавких перемычек.

Фрагмент схемы диодной матрицы ППЗУ с плавкими перемычками.

Фрагмент схемы диодной матрицы ППЗУ с плавкими перемычками.

Пропуская импульсы тока между соответствующими строками и столбцами матрицы, такие ЗУ можно программировать, расплавляя те или иные перемычки. На рисунке часть перемычек показаны уже разрушенными.

Фрагмент схемы матрицы ППЗУ с многоэмиттерными транзисторами и плавкими перемычками.

Фрагмент схемы матрицы ППЗУ с многоэмиттерными транзисторами и плавкими перемычками.

Разрушая соответствующие перемычки, осуществляют программирование таких ППЗУ.

ППЗУ выпускаются в составе серий микросхем 155, 541, 565, 1608. В обозначениях таких ЗУ используют буквы РТ.

Так, например, микросхема К541РТ1 выполнена по ТТЛШ-технологии с открытым коллекторным выходом и имеет организацию 256 х 4.

В РПЗУ запоминающие ячейки строятся на основе МОП-технологий. Используются различные физические явления хранения заряда на границе между двумя различными диэлектрическими средами или проводящей и диэлектрической средой.

В первом случае диэлектрик под затвором МОП-транзистора делают из двух слоев: нитрида кремния и двуокиси кремния (SiN4 — SiO2). Было обнаружено, что в сложной структуре SiN4 — SiO2 при изменении электрического напряжения возникает гистерезис заряда на границе раздела двух слоев, что и позволяет создавать запоминающие ячейки.

Такие транзисторы называют МНОП-транзисторами в соответствии с их структурой: металл-нитрид кремния-окисел-полупроводник.

Запись информации в ячейки на МНОП-транзисторах осуществляется подачей относительно высоких напряжений (около 20 В), а перед записью осуществляется электрическое стирание старой информации (запись 0 во все запоминающие элементы). Таким образом, ЗУ на МНОП-транзисторах — это РПЗУ ЭС или EPROM. Они позволяют осуществлять 104 — 106 перезаписей, энергонезависимы и могут хранить информацию годами.

В обозначении микросхем с электрическим стиранием после номера серии указывают две буквы PP.

Так, микросхема К1601РР1 выполнена на основе p-МНОП-транзисторов, по входу и выходу совместима с ТТЛ-структурами, имеет выходы с тремя состояниями и организацию IK x 4. Время хранения информации 500 часов.

Во втором случае основой запоминающей ячейки является лавинно-инжекционный МОП-транзистор с плавающим затвором (ЛИЗМОП-транзисторы).

В лавинно-инжекционном транзисторе с плавающим затвором при достаточно большом напряжении на стоке происходит обратимый лавинный пробой диэлектрика, и в область плавающего затвора инжектируются носители заряда. Поскольку плавающий затвор окружен диэлектриком, то ток утечки мал и хранение информации обеспечивается в течение длительного промежутка времени (десятки лет). При подаче напряжения на основной затвор происходит рассасывание заряда за счет туннельного эффекта, т. е. стирание информации.

В лавинно-инжекционном транзисторе с плавающим затвором при достаточно большом напряжении на стоке происходит обратимый лавинный пробой диэлектрика, и в область плавающего затвора инжектируются носители заряда. Поскольку плавающий затвор окружен диэлектриком, то ток утечки мал и хранение информации обеспечивается в течение длительного промежутка времени (десятки лет). При подаче напряжения на основной затвор происходит рассасывание заряда за счет туннельного эффекта, т. е. стирание информации.

С использованием ЛИЗМОП-транзисторов строятся РПЗУ как с ультрафиолетовым (EPROM), так и электрическим (E2PROM) стиранием информации.

В ЗУ с ультрафиолетовым стиранием в корпусе микросхемы имеется специальное прозрачное окошко для облучения кристалла, причем информация стирается во всем кристалле.

При электрическом стирании информацию можно стирать не со всего кристалла, а выборочно.

Кроме того, длительность электрического стирания значительно меньше, чем ультрафиолетового, а число циклов перезаписи значительно больше.

Поэтому ЗУ с электрическим стиранием информации вытесняют ЗУ с ультрафиолетовым стиранием.

В обозначении микросхем с ультрафиолетовым стиранием после трех цифр серии указывают две буквы РФ.

Люди также интересуются этой лекцией: Самосознание личности.

РПЗУ с ультрафиолетовым стиранием информации серии 573 выполнены на основе ЛИЗМОП-транзисторов, по входу и по выходу совместимы с ТТЛ-структурами.

Промышленность выпускает большое количество типов микросхем ПЗУ. Укажем в качестве примера две микросхемы ПЗУ. На схемах использованы следующие обозначения: Aj— адресные входы; Dj — информационные выходы; CS — выбор микросхемы; СЕ — разрешение выхода.

Промышленность выпускает большое количество типов микросхем ПЗУ. Укажем в качестве примера две микросхемы ПЗУ. На схемах использованы следующие обозначения: Aj— адресные входы; Dj — информационные выходы; CS — выбор микросхемы; СЕ — разрешение выхода.

Микросхема К573РФ5 — это репрограммируемое ПЗУ (РПЗУУФ) с ультрафиолетовым стиранием, имеющее структуру 2К х 8. По входу и выходу эта микросхема совместима с ТТЛ-структурами. Время хранения информации — 50 тыс. часов.

Микросхема К556РТ5 — это однократно программируемая ПЗУ, выполнена на основе ТТЛШ-структур, по входу и выходу совместима с ТТЛ-структурами, имеющая структуру 512 бит х 8.

Характеристики ПЗУ: