Реализация цифровых фрагментов

· Курс «Информационные технологии

· в проектировании ЭВС»

· Лекция №12

· «Технологии проектирования ИСПС»

11.2. Реализация цифровых фрагментов в форме полузаказных кристаллов (продолжение)

В качестве примера рассмотрим проектный процесс с проектными нормами 0,35 мкм. В основе проектной процедуры лежит использование фирменной технологии под названием FlexStream, которая интегрирует в своем составе как специфические собственные проектные средства, так и встроенные лучшие САПР других фирм, таких как Avanti, Cadence, Mentor Graphic и Synopsys Подобное объединение различных средств в единой оболочке позволяет использовать эту технологию на всех уровнях проектирования (системном логическом и физическом).

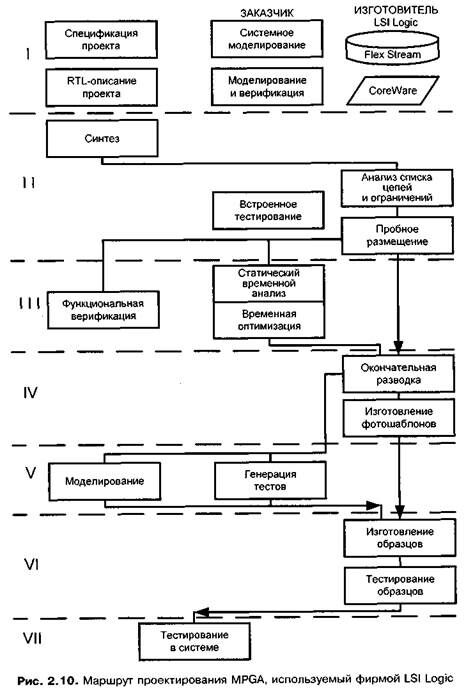

В состав собственных средств фирмы, помимо библиотек, включаются проектные средства, которые позволяют осуществлять проектный анализ, интерфейс со стандартными САПР, вычисление задержек, генерацию модулей, контроль проектных норм и т. д. Так же, как и фирма AMI, фирма LSI Logic в процессе работ над выпуском кристалла предполагает тесное взаимодействие с заказчиком-проектировщиком. Основное различие состоит в ориентации фирмы LSI Logic на описания проектов на уровне регистровых передач. В процедуре проектирования фирма выделяет семь основных контрольных точек. Содержание этапов и взаимодействие разработчика и изготовителя приведены на рис. 2.10.

Рекомендуемые материалы

Рассмотрим последовательно маршрут проектирования и кратко охарактеризуем работы, выполняемые на отдельных этапах.

Этап 1. Начало работ над проектом. Заказчиком создается описание проекта на блочном уровне и спецификация на уровне регистровых передач (RTL). В проекте могут использоваться стандартные решения фирмы LSI Logic — CoreWare. Описание вводится в САПР, САПР контролирует проект и выполняет синтез до вентильного уровня. Одновременно с синтезом производится проверка функционирования и соблюдения указанных временных ограничений. Фирма LSI Logic просматривает спецификации проекта и может осуществлять консультирование и обучение разработчиков. Процесс контроля и синтеза итерационный. Результатом работ этого этапа является предварительное разбиение проекта на части и составление списка соединений.

Этап 2. Начальное физическое размещение. Список соединений и ограничения анализируются совместно, чтобы быть уверенными в том, что проект хорошо структурирован и не содержит фрагментов, которые смогут создать проблемы (во временной области) при физической реализации. Осуществляется статический временной анализ и функциональная верификация.

Этап 3. Пробная разводка. Блоки разводятся, размещаются шины питания и синхронизации, определяются места максимального скопления трасс и цепи, нарушающие временные ограничения. Информация о топологическом распределении элементов и граф их соединений объединяются в общий отчет для просмотра.

Этап 4. Если параметры межсоединений и временные характеристики оказываются приемлемыми, тогда переходят к окончательному размещению и трассировке. В случае неудовлетворительных результатов предыдущего этапа производится повторное разбиение проекта на части, их новая организация или производится синтез с измененными ограничениями. После завершения размещения выдаются данные для верификации законченного изделия. Приступают к генерации тестирующих программ.

Информация в лекции "2 - Подготовка воздуха" поможет Вам.

Этап 5. Заказчик анализирует данные, полученные после окончательной разводки изготовителем. Производится просмотр результатов разводки на моделях. Осуществляется разработка тестовых программ. При выполнении всех требований проект утверждается и передается на изготовление.

Этап 6. Фирма-изготовитель выпускает фотошаблоны, изготавливает и проверяет подложки. Готовность прототипных образцов и тестов позволяют приступить к системному тестированию.

Этап 7. Удачное завершение системных тестов, производимых заказчиком, служит признаком принятия ИС и завершения проекта.

Основное внимание при выборе технологического процесса и используемых проектных средств фирма уделяет уменьшению числа итерационных возвратов к процедуре синтеза проекта.

Важным средством, которое существенно улучшает методологию проектирования схем класса ASIC в форме MPGA/SC, можно считать добавление этапа прототипирования схемы MPGA схемами FPGA/CPLD. Для обеспечения эффективности процесса прототипирования желательно выполнение двух условий. Во-первых, чтобы для конечного и прототипного вариантов продукции либо использовался совпадающий способ задания исходной информации, либо взаимные переводы осуществлялись простыми методами. При этом методы и средства задания исходной информации могут быть различными. Общение между САПР изготовителя MPGA и САПР изготовителя FPGA/CPLD может осуществляться при помощи различных стандартных языков описания аппаратуры (EDIF, Verilog или VHDL). Вторым условием является обеспечение структурно-архитектурной близости между двумя вариантами реализации, которые гарантировали бы преемственность функциональных характеристик проекта. Описание на уровне регистровых передач в наибольшей степени позволяет сохранить близость поведения оригинала и прототипа.