- Системы на кристалле (СНК)

Лекция 6 Системы на кристалле (СНК)

В том случае, если существующая функциональность недостаточна, то систему реализуют в виде нескольких интегральных схем. Системы на кристалле (СНК) потребляют меньше электроэнергии, имеют меньшую стоимость и работают надёжнее, чем микроконтроллеры той же функциональности. А также будут иметь более высокую надёжность. В современных интегральных схемах самую малую надёжность имеют входы-выходы (ножки). Т.е. чем больше интегральных схем, тем больше паяных соединений, тем ниже надёжность. Меньшее количество корпусов интегральных схем упрощает монтаж. В качестве элементной базы СНК, как правило, используются микросхемы ПЛИС.

ЯЗЫКИ ОПИСАНИЯ АППАРАТУРЫ (HDL)

Языки описания аппаратуры предназначены для текстового описания структуры и функциональности аппаратных проектов, и могут применяться в любых областях разработки аппаратуры, но чаще всего используются для конфигурации ПЛИС. Существует большой набор различных языков описания. Специфичных для фирм-производителей интегральных схем, и универсальных (оговоренными мировыми стандартами). В ходе проектирования, описание, полученное на HDL, преобразуется в набор точек соединения в микросхеме ПЛИС, что в свою очередь, создаёт требуемую функциональность интегральных схем. В настоящее время меняется стиль создания аппаратуры, которая происходит в виду языкового описания функциональности, а не в виду электрических принципиальных схем.

Использование электрических принципиальных схем происходит в трёх видах:

1. Построение схем конфигурации ПЛИС. Подобные действия происходят при оптимизации проекта.

2. Взаимоподключение блоков, описанных на HDL.

3. Схема использования ПЛИС (от схемы Э3 до печатной платы).

В качестве примера, рассмотрим использование языка VHDL.

Рекомендуемые материалы

VHDL – very high speed HDL. Язык, определённый международным стандартом IEEE-1076 от 2002го года, и отечественным стандартом ГОСТ Р50-754-95. Язык был создан в 1983 году по заказу Министерства Обороны США для формирования логического описания логических схем. В настоящее время является одним из нескольких универсальных языков, применимых для всех ПЛИС. Формально, язык имеет аналогию с языком Ассемблер, в то время как иные универсальные HDL построены по аналогии с иными языками, например, С. VHDL основан на любимом языке мин.обороны США – ADA. Спектр языков широк, каждый может писать те языки, какие хочет, но VHDL – наиболее системный.

Типы описаний на языке VHDL.

Существует 3 вида описаний на языке VHDL:

1. Структурное;

2. Потоковое;

3. Поведенческое.

1. Структурное (регистровое) описание;

При нём архитектура проекта представляется в виде иерархий связанных компонентов, каждый экземпляр компонента представляет часть проекта, которая, с другой стороны, может быть описана объектом другого уровня иерархии, и т.д.

2. Потоковое описание (dataflow description);

Архитектура представляется в виде множества параллельных регистровых операций, каждый и которых управляется специальными сигналами для потокового описания. Часто используется язык графического описания RTL, который представляет разработку в виде набора регистров и систем управления ими. Описание конфигурации аппаратуры может быть получено из других типов описания (автоматических).

3. Поведенческое описание (behavior description).

Определяет функционирование устройств без определения его структуры. Например, один из разработчиком может детально специфицировать поведение системы, а проработка деталей может осуществляться другим проектировщиком.

При описании цифровой аппаратуры, программа VHDL, состоит из 5 типов, из которых наиболее часто используются первые два.

1. Объявление объекта проектом (сущность проекта). Entity (сущность) – словом VHDL. Представляет собой описание компонента проекта, имеющего чётко заданные входы и выходы, и выполняющую чётко определённую функцию (содержит константы проекта, и описание входа и выход)

2. Архитектурное тело. Служит для описания структуры или поведения разрабатываемого объекта.

3. Объявление конфигураций. Предназначено для описания того, какие объекты используется для создания полного проекта.

4. Объявление пакета. Представляет собой указания пакетов, содержащих наиболее часто используемые функции. Пакеты эквиваленты набору типовых функций в языках программирования.

5. Тело пакета. Если пользователь использует нестандартные операции или функции, их интерфейс указывается в объявлении проекта, а исполнение функций описывается в теле проекта.

Типы используемых библиотек

1. Библиотека проекта (Design library) – включает в себя все разработанные и подключенные модули. Библиотека определяется именем. Каждое из описаний является самостоятельной конструкцией языка VHDL и может быть независимо проанализировано анализатором, и имеет название «модуль проекта» (Design unit).

2. Рабочая библиотека – библиотека, в которой в данном сеансе работает пользователь, и в которую помещается библиотечный модуль, полученный в результате анализа модуля проекта.

3. Библиотека ресурсов – библиотека, содержащая библиотечные модули, ссылка на которые имеется в анализируемом модуле проекта.

В тексте VHDL должны быть указаны все используемые библиотеки и их компоненты и используемые модули этих библиотек. Можно использовать всё – «.all»

Первая часть программы – это библиотеки. Все предложения языка VHDL заканчиваются «;».

Library use *библиотека*

--вот так обозначаются комментарии, в конце не нужно ставить «;»

Блок сущности (entity) – начало большого предложения языка, заканчивается «end *имя*». И только после «end» - «;». Сущность состоит из 2х частей: Generic ((параметры) – содержат переменные, используемые в процессе препроцессинга. Константа используется только в процессе компиляции.)

Generic (*параметр*);

Порты – сдержат описания портов входа и выхода

Port (*описание портов*);

Описания, заключённые в скобки могут быть многострочным.

Лекция 7

Типы данных языка VHDL

Типы данных представляются как в виде включённых в систему типов, например byte, integer, так и определяемые пользователем. Например, наиболее часто используемый тип – стандартная логика «std_logic» может принимать следующие значения:

U – неинициализированный сигнал, т.е. сигнал, который ещё не был задан.

Х - сильный неизвестный сигнал.

0 – сильный ноль

1 – сильная единица

Z – высокоимпедансное состояние

W – слабый неизвестный сигнал (слабый сигнал – это, например, сигнал на линии, реализуемой с открытым коллектором, или подключение по монтажному «И»).

L – слабый ноль

H- слабая единица

– - не имеет значения.

Тип может быть определён командой TYPE, после которой следует название типа, IS и список возможных значений

Type bulian is (FALSE, TRUE);

Разные наборы действий доступны различным типам данных. Например, если есть многоразрядная переменная типа bulian, то к ней недоступна команда сложения, однако, она доступна типу Integer. Для преобразования типа существуют специальные команды.

Модели данных

1. Константа (constant)

2. Переменная (variable)

3. Сигнал (signal) эквивалентен переменной, однако рассматривается её изменение во времени, т.е. доступно её значение в предыдущие моменты времени.

4. Файл – сложноорганизованная переменная

5. Задержанные переменные (shared variables) – переменная, значение которой на момент определения не задано.

Примеры определения данных.

Модель

1. Название модели

2. Список данных: тип данных;

Сигнал

Signal X, Y, mysignal:std_logic;

Переменная

Variable temp : std_logic:=’0’;

Отсроченная переменная

Shared variable Y: bit;

Операторы присваивания.

Для сигналов оператор присваивания - ‘≤’, а для всех остальных типов – ‘:=’

Определение векторов.

Помимо скалярного существует векторный тип. Типы для стандартной логики задаются с помощью слова-команды: std_logic_vector(*диапазон*).

Диапазоны бывают 2х типов:

1. Нисходящий – задаётся словом ‘downto’

std_logic_vector(7 downto 0);

2. Восходящий – задается словом ‘to’

std_logic_vector(0 to 7);

Variable IN: stg_logic_vector (0 to 3);

Для того, чтобы обратиться к отдельному разряду этой переменной, можно использовать ‘()’. Ну или ‘[]’, которые более приняты в схемотехническом плане.

IN[2] – второй бит переменной IN.

1. Сущность:

Generic (length : integer := 8); // создаём глобальную константу length, которая во всём проекте на момент компиляции = 8.

2. Порты:

Типы портов:

a. IN – входной порт только для чтения значения сигналов

b. OUT - выходной порт

c. INOUT – двунаправленный порт. Можно как записывать, так и читать из него.

d. Буфер – выходной порт, значение из которого можно считывать

e. Linkage – двунаправленный порт с ограниченным использованием (практически не используется).

Пример:

Port (A,B: IN:std_logic_vector (0 to 3); S:OUT:std_logic_vector (0 to3); C:OUT:std_logic);

Архитектурное тело состоит из 2х частей: определение констант и переменных, и из поля команд, которое содержит исполняемые действия. Поле определений от поля действий отделяется командой begin.

Architecture *имя архитектуры* *OP-имя сущности* *IS-описание определений*;

begin *действия*;

end *имя архитектуры*;

Действия архитектуры.

Действия могут представляться двояко: как операции и процессы.

Операции VHDL.

1. Логические операции (and, or, nor, xor, xnor…)

2. Операции сравнения (=, /=, <, ≤, >,≥)

3. Операции сдвига (SLL, SRL, ROR, SRA…)

4. Операции сложения (+,-)

5. Умножение и деление (*,/)

6. Выделение частного и остатка (mod, rem)

7. Прочие (abs – модуль инверсий)

Язык VHDL предполагает возможность указания меток и механизма «go to». Операторы бывают последовательные и параллельные, синтезируемые и внедрённые, простые и составные.

Последовательный оператор. Оператор условия.

Особенностью оператора условия является наличие множества блоков срабатывания условия (когда условие верно), которые задаются командой ELSIF (другое если). Условие задаётся следующим образом:

IF *условие 1* then

*выполнение условия 1*…

ELSIF *условие 2* then

*выполнение условия 2*…

ELSE *невыполнение условия*…

End if;

Циклы.

Задаются с использованием чётной переменной.

FOR *счётная переменная* IN *диапазон изменения* LOOP

*операция в цикле*;

END LOOP;

FOR i IN 5 downto 0 loop

*операции в цикле*

End loop;

Цикл с условием

Задаётся командой WHILE.

While *условие* LOOP *операции* end loop;

Множественный выбор

CASE *переменная* IS

When *значение 1* => *выполненная команда 1*;

END CASE

CASE sel IS

WHEN "00" => output <= in0;

…

END CASE;

Оператор ожидания – определяет врем ожидания процесса, или события. Задаётся с помощью команды wait. Опирается на такое понятие, как список чувствительности (лист чувствительности) – одна или более переменных, изменение значения которых приводит к активации того или иного оператора.

Wait on (*лист чувствительности*) UNTIL *действие* FOR *время*;

Например:

Wait on (X,Y) UNTIL z=0 FOR 100ns

VHDL работает с точностью указания времени до фемтосекунды (10-15). Список чувствительности может отсутствовать вместе с командой.

События – либо фронт либо срез! Особые ситуации изменения переменных в списке чувствительности – это события фронта и среза сигнала.

Параллельные операторы – блок и процесс.

Блоки.

Block (*условие*)

*определение используемых данных - константы и переменные*

begin *описание процесса*

End block;

Процессы.

Process (*лист чувствительности*)

*область декларации*

Begin *VHDL операторы* *описание процесса*

End process;

В программе на VHDL может присутствовать множество процессов, отмеченных разными списками чувствительности. Данные процессы реализуются параллельно.

Компоненты.

Оператор определения компонент:

component *имя компонента* *порт (определение линий порта)*;

end component;

Существо выполняемых компонентом функций определяется дополнительно.

Указание линий передачи информации.

*Имя компонента*

Port map (*имя выходного порта в данном компоненте* => *название переменной куда будет записано значение выхода*,… );

Рассматривается классификация современных ПЛИС. Ряд существующих типов опущен ввиду их неиспользования. Рассматриваются такие типы, как CPLD (complex programmable logic device), FPGA (field-programmable gate array – программируемая пользователем вентильная матрица), ASIC (Application-specific integrated circuit - интегральная схема, специализированная для решения конкретной задачи). ASIC микросхемы являются полузаказными и изготовляются на заводе-изготовителе. Дальнейшее изменение ASIC больше невозможно.

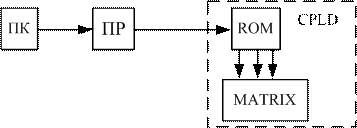

Рисунок 32 - Использование ПЛИС CPLD.

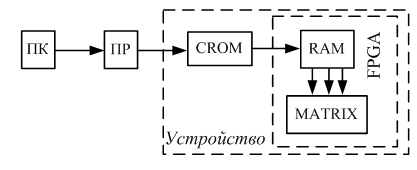

Рисунок 33 - Использование ПЛИС FPGA.

FPSLIC (field programmable system level integrated circuit) – отличается от ПЛИС тем, что в рамках её кристалла реализовано ядро, осуществляющее функции вычислительного устройства с жёсткой логикой функционирования, т.е. микропроцессор.

Преимущества:

1. Для создания вычислительного ядра системы не используются ресурсы ПЛИС.

Недостаток:

1. Функциональность вычислительного ядра не может быть изменена пользователем.

2. В настоящее время микросхемы FPSLIC всё ещё дороги.

Лидером в построении системы FPSLIC, а также разработчиком этой архитектуры является фирма Atmel (AT94).

Виды внутренних ресурсов ПЛИС.

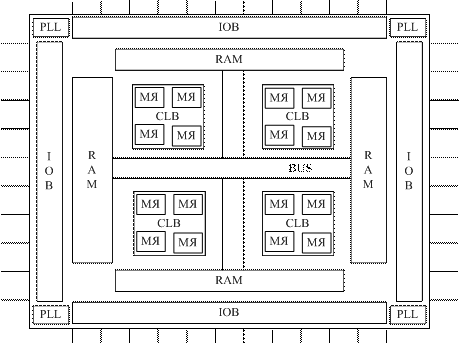

1. Самая минимальная ячейка ПЛИС – программируемая ячейка (макроячейка в случае CPLD , в случае FPGA – блок LUT. LUT (таблица перекодировки) + триггер).

2. Блок конфигурируемых логических ячеек (CLB). CLB состоит из множества соединённых друг с другом программируемой матрицы макроячеек (LUT). Весь набор базовых элементов (см. п1.) разделяется на равные подгруппы (как правило, 2 или 4 блока) с целью снижения сложности программируемой матрицы.

3. INPUT/OUTPUT блок. Блок, задающий подключение конкретных выводов микросхемы к разрабатываемому проекту. Кроме этого, блок задаёт вид логики, используемой для данного выхода (вид логики – уровни напряжений, а также инверсия сигнала).

4. PLL(PLD) – программируемая защёлка. PLL – программируемый делитель частоты, PLD – программируемый формирователь фазы сигнала. По существу, данные блоки – синонимы, на их вход приходит внешний, по отношению к ПЛИС тактовый импульс. На выходе данных блоков пользователь получает сетку частот. Блоки PLL могут как делить частоту, так и в определённых пределах умножать частоту.

5. Блочная память (BRAM) – представляет из себя блоки статического ОЗУ, организованные как битовые массивы. При этом, BRAM может быть сконфигурирована пользователем на требуемую разрядность. Память организована как двупортовая (на запись и на чтение информации). Функции чтении и записи могут осуществляться одновременно. Порт состоит из ША и ШД. BRAM имеет 2 ША и 2 ШД. Шины - однонаправленные.

6. Система шин (BUS). Внутренний состав ПЛИС приведён на рисунке 34. На рисунке изображены по 4 блока каждого вида, однако, их количество специфично для каждого типа микросхемы.

Рисунок 34 - Внутренний состав ПЛИС.

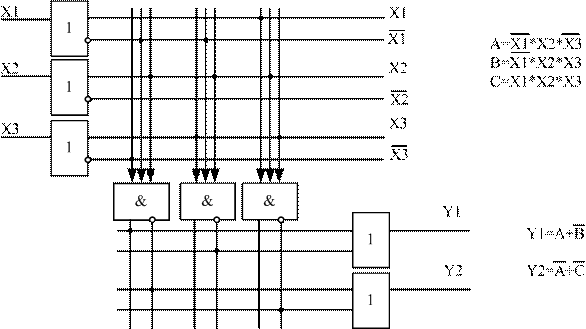

Программируемая логическая матрица «И-ИЛИ»

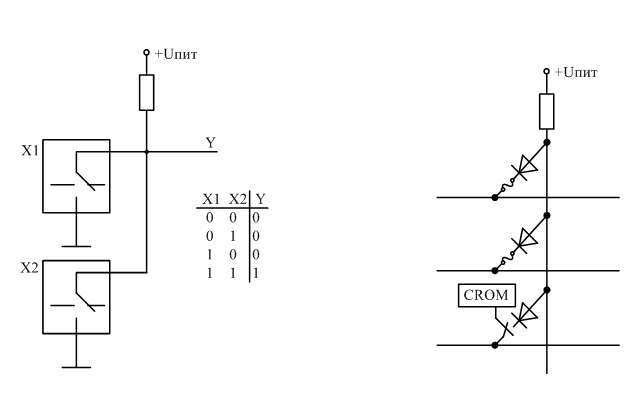

Рисунок 28 - Программируемая логическая матрица «И-ИЛИ».

В качестве входов в первую матрицу «И» используется линейка повторителей сигналов Х1,Х2,Х3… с парафазным выходом, т.е. элемент имеет 2 выхода, первый из которых повторяет сигнал на входе, а второй – инвертирует даны сигнал. ПЛМ «И-ИЛИ» состоит из двух подматриц: «И» и «ИЛИ». На решетчатой структуре подматрицы, пользователь, с помощью управляемых коммутаций может устанавливать или удалять соединения. Выходы столбцов матрицы подаются на многовходовые элементы «И» с парафазным выходом. В данном случае мы имеем линейку многовходовых элементов. Для более удачного изображения схемы, элементы «И» изображены на рисунке не по ГОСТ, т.е. развёрнутыми на 90*, а линии входов обозначены стрелочками линий столбцов. Выходы элементов «И» подаются на следующую матрицу – матрицу «ИЛИ». В данном случае показаны 3 входных сигнала – Х1, Х2, Х3. И 2 выходных сигнала – Y1, Y2. Между ними расположены 2 матрицы – «И» и «ИЛИ». Количество входов и выходов зависит от типа используемой микросхемы.

В современных микросхемах ПЛИС, матрица «ИЛИ» как правило, является вырожденной, те. Представляет из себя многовходовой элемент «ИЛИ», подключаемый по жёсткой логике. Точки подключения в матрице реализуются с помощью электронных ключей и плавких перемычек. Использование плавких перемычек позволяет повысить надёжность функционирования ПЛИС в определённых областях применения (высокое радиационное излучение, космический ветер и т.д.).

Преимущества точек соединения на плавких перемычках:

1. Устойчивы к воздействию случайно залетающих элементарных частиц

Недостаток – одноразовость. Нельзя изменить.

А в случае электронных ключей преимущества и недостатки – зеркальны.

Подключение электронных соединений осуществляется под управлением информации, записанной в конфигурационную память. В случае СPLD – ПЗУ, а в случае FPGA – ОЗУ. В ПЛМ может быть большое количество линий. Это приведёт к тому, что линии столбцов потребуют многовходовых элементов «И». В реальности, многовходовые элементы «И» строятся на основании принципа монтажного «И». Схема монтажного «И» самостоятельна.

Рисунок 29 - Многовходовой элемент И.

О правой части рисунка следует отметить использование диодов, которые предназначены для того, чтобы сигналы одной горизонтальной линии, подключенной к столбцу не влияли на сигнал другой горизонтальной линии. На данной части рисунка изображены как соединения на бае плавких перемычек, так и соединения на базе ключей. Это является примером – в реальных микросхемах такое невозможно.

В реальных микросхемах используются полученные таким образом многовходовые элементы «И». Структура ПЛМ примет вид как на рисунке 30. От рисунка 28 она отличается лишь количеством входов в элементах «И».

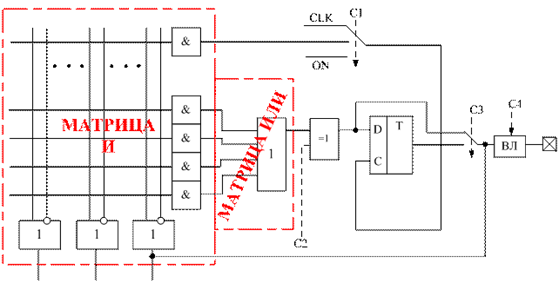

Структура макроячейки ПЛИС CPLD.

Основным компонентом микросхема CPLD является т.н. макроячейка, содержащая, наряду с конфигурируемой логикой, элемент памяти. Данные функции в микросхемах FPGA является блок LUT и триггер. Отличия лишь в том, что в CPLD рассматривается всё в виде единого блока (макроячейка), а в FPGA – блок LUT+блок триггеров. Но функции в принципе те же самые.

Макроячейка состоит из:

· конфигурируемой матрицы «И»

· фиксированной матрицы «ИЛИ» (которая представляет из себя 1 многовходовой элемент «ИЛИ»)

· управляемый инвертор, который выполнен в виде исключающего «ИЛИ» (один вход – информационный, другой – управляющий)

· D-триггер, запись в который осуществляется либо сигналом матрицы «И», либо внешним тактовым импульсом, либо постоянным уровнем.

· Выходная логика, которая показывает:

- следует ли подключать выход макроячейки к внешнему контакту микросхемы ПЛИС

- типа дополнительной функции (инверсия). Нужна или не нужна инверсия.

- тип логики (уровни логических сигналов) – выбор, с какими сигналами работать

В схеме присутствуют 4 управляющих линии (шины) – 2 одноразрядных, 2 многоразрядных.

Control1 (C1) – выбирает, какой сигнал записи в триггер будет использоваться.

Control2 (C2) – сигнал включения или выключения инверсии.

Control3 (C3) – включение триггера в работу/отключение. Сигнал с конфигурируемых матриц может выходить из макроячейки и без запоминания.

Control4 (C4) – сигнал управления выходной логикой.

На входы матрицы i подаются сигналы с выходов всех макроячеек CLB, в том числе и из выхода текущей макроячейки.

Рисунок 31 - Структура макроячейки ПЛИС CPLD.

Виды современных ПЛИС

1. CPLD – complex PLD, основано на блоках макроячеек. Информация о конфигурации данной микросхемы хранится во внутренней энергонезависимой памяти (ROM, EEPROM, flash)

Преимущества:

1. Не требуется дополнительной микросхемы памяти

2. Высокая защищённость проекта (данные микросхемы обладают возможностью запрета чтения информации из конфигурационного ПЗУ, что не даёт злоумышленнику кражи топологии(конфигурации) микросхем)

Недостатки:

1. Необходимость реализации ПЗУ на ПЛИС (дорого, низкотехнологично)

2. Небольшой объём реализуемых функций (32-7000 макроячеек), по сравнению с FPGA – намного меньше например.

2. FPGA – field-programmable gate array (Программируемая пользователем вентильная матрица)

Информация о конфигурации микросхемы FPGA хранится во внутренней энергозависимой памяти, реализованной как статическое ОЗУ. Каждый раз, при перезагрузке микросхемы во внутреннее конфигурационное ОЗУ, информация загружается из внешнего конфигурационного ПЗУ (CROM).

Преимущества:

1. Высокая сложность микросхемы, которая позволяет реализовывать широкий спектр функций

2. Возможность изменения функциональности микросхемы даже в процессе работы (однако, перезагрузка требуется). Можно изменить информацию в конфигурационном ПЗУ, перезагрузить систему и начать работать в системе с новыми конфигурациями.

Недостатки:

1. Дорогая

2. Необходимость внешней микросхемы памяти (зачастую стоимость CROM соизмерима, если не выше, со стоимостью ПЛИС) – падает надёжность.

3. Слабая защищённость проекта заключается в том, что злоумышленник может снять информацию в точке между CROM и FPGA, и на основании снятой информации, получить конфигурацию ПЛИС. Для минимизации этого недостатка используют различные методы, например:

1. Использование батарейного питания и отказ от конфигурационной памяти (CROM). Информация во внутреннюю RAM записывается при создании устройства, после чего напряжение питания этой памяти не пропадает никогда в процессе эксплуатации (каждый раз при перезагрузке не идёт передача информации с ПЗУ в ПЛИС- злоумышленникам неоткуда будет снимать поток). Недостаток – при повреждении батареи функциональность устройства пропадает.

2. Использование пары кодер-декодер по тому или иному криптографическому алгоритму, например, AES. Кодер находится в CROM, декодер – в FPGA.

Кроме применения в научной области и универсальных ЭВМ, СуперЭВМ, микросхемы FPGA используются в процессе прототипирования, т.е. в дальнейшем они могут быть созданы на микросхемах с жёсткой логикой функционировании.

ASIC (Application-specific integrated circuit) – интегральная схема, специфицируемая под специфику предметной области. Разрабатывается аналогично другим микросхемам ПЛИС, однако, изготавливается вплоть до фиксированных внутренних подключений на заводе-изготовителе интегральных схем. Полузаказная микросхема.

Завод имеет определённую структуру микросхем ASIC, список подключений которой ему передаёт пользователь, и завод изготавливает интегральную схему с жёсткой логикой функционирования.

Но недостатки ASIC – невозможность изменения и высокая стоимость, которая потом компенсируется при массовом выпуске микросхем.

CPLD и FPGA приведены на рисунках 32 и 33.

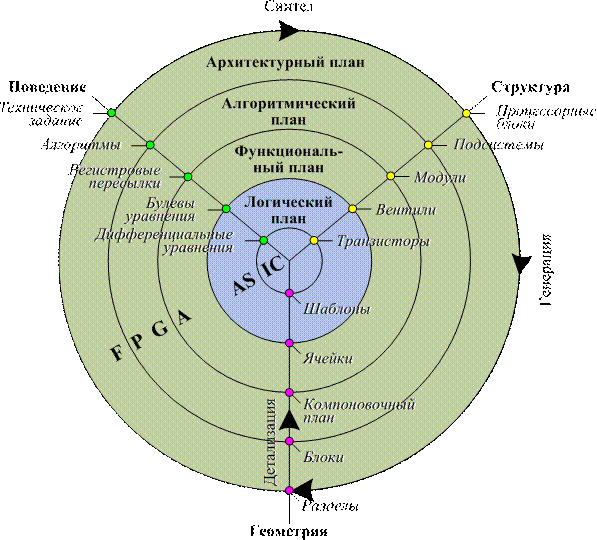

Диаграмма Гайского-Кана (Y-диаграмма)

Рисунок 35 - Диаграмма Гайского-Кана или Y-диаграмма.

Диаграмма Гайского-Кана состоит из 3х ветвей, соединённые в виде Y: поведенческая, структурная и геометрическая.

Поведенческая ветвь рассматривает вопросы проектирования (описания) поведения разрабатываемого устройства. Поведение – это последовательность и взаимосвязь событий по переключению электронных сигналов.

Структурная ветвь предназначена для описания электрической структуры разрабатываемого устройства (от Э1 до Э4).

Геометрическая ветвь описывает внутреннюю геометрию интегральной схемы (расположение функциональных блоков, фотошаблоны)

Перпендикулярно ветвям диаграмма разделяется на 4 плана, изображаемых в виде концентрических окружностей. В точках пересечения этих концентрических окружностей ветвями появляются модули.

Планы:

1. Наружный план – архитектурный план – предназначен для решения задач построения архитектуры электронного устройства.

2. Алгоритмический план – решает вопросы построения алгоритмов функционирования.

3. Функциональный план решает вопросы реализации функций устройства

4. Логический план – решает вопросы построения логики электрических схем.

Таким образом, рассматривается 15 элементов (5 планов * 3 ветви) диаграммы Гайского-Кана:

1. Поведенческая ветвь:

1.1. Техническое задание

1.2. Алгоритмический план

1.3. Функциональный план

(регистровые пересылки описывают решаемую задачу в виде множества регистров и взаимоподключений между ними; схема на этом плане описывается на языке RTL)

1.4. Булевы уравнения

1.5. Дифференциальные уравнения

2. Структурная ветвь:

2.1. Процессорные блоки (например, вычислительное ядро AVR, MARK..)

2.2. Алгоритмический план (подсистемы: блоки памяти, телекоммуникационные блоки, вычислительные блоки)

2.3. Функциональный план (модули: RAM, CLL)

2.4. Вентили (определяют принципы построения результатов проектирования на предыдущих планах)

2.5. Переход на минимальные элементы – транзисторы.

3. Геометрическая ветвь.

3.1. Разделы интегральной схемы

3.2. Блоки – показывают, из каких элементов состоят разделы.

3.3. Компоновочный план – решает задачи взаимного расположения элементов

3.4. Ячейки – показывают, как расположены элементы компоновочного плана

3.5. Шаблоны – технологически определяют взаимную послойную геометрию кристалла интегральной схемы

Синтаксис - переход от поведения к структуре. Синтаксис присутствует в тех.задании. На основе его мы можем решить - какой процесс нам нужен, алгоритмы – синтезируем, какие нам подсистемы нужны для использования. Переход от структуры к геометрии – генерация.

Переход вдоль осей от внешних планов к центру диаграммы называется процессом детализации.

В процессе разработки устройства происходят последовательные переходы от одной ветви к другой с постепенным понижением плана разработки, т.е. происходит переход от внешней области диаграммы к её центру. Чёткий спиральный характер таких переходов необязателен.

Получить работоспособную версию микросхемы можно и не доходя до центральных планов. В этом случае, будет получен проект менее оптимальный.

При осуществлении процесса прототипирования, мы последовательно приближаемся к центру диаграммы. При создании первых прототипов используются микросхемы FPGA. При последующем уточнении и оптимизации проекта, по диаграмме Гайского-Кана, мы приближаемся к её центру, который соответствует микросхеме ASIC.

Проект начинается с использования симулятора на FPGA, и заканчивается получением интегральной схемы неизменной логикой функционирования ASIC.

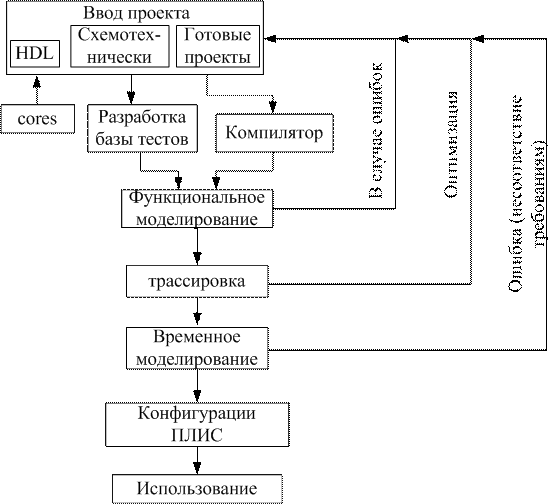

Маршрут проектирования конфигурации ПЛИС (design flow)

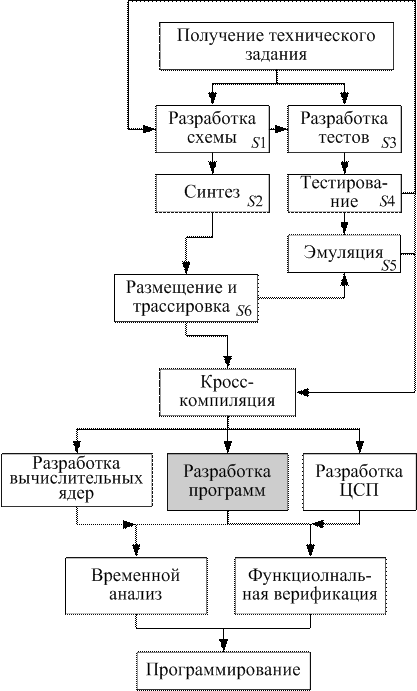

Маршрут проектирования представляет из себя граф, показывающий взаимовызов проектных функций. Типовой маршрут проектирования приведён на рисунке 36. На нём выделены следующий объекты и функции:

1. Cores (ядра) – модули конфигурации, созданные, как правило, третьесторонними разработчиками;

2. HDL-описание;

3. Схемотехническое описание;

4. Готовые проекты.

Рисунок 36 - Типовой маршрут проектирования конфигурации ПЛИС – I.

Блоки функций:

- Блок проекта – ввод проекта. В плане реализации этой функции осуществляется построение схемы или описание устройства.

- Разработка базы теста. Тесты могут представляться как в графической форме (примитивный уровень), так и в текстовом описании, на языках описания аппаратуры HDL, либо других языках (TCL/TK).

- Компилятор. Выполняет функцию генерации диаграммы Гайского-Кана. Вполне возможно, что разработка базы тестов и компиляция могут происходить одновременно, в крупных проектах, например. Но в реальности всё это делает 1 человек.

- Функциональное моделирование. Процесс, предназначенный для подтверждения работоспособности введённого устройства (проекта), его соответствие тех.заданию. В случае возникновения ошибок, происходит возврат на тап ввода проекта.

- Трассировка. Процесс, осуществляющий размещение конкретных функциональных узлов проекта по элементам ПЛИС. В случае трассировки может возникнуть потребность оптимизации проекта (возврат на функцию ввода проекта).

- Временное моделирование. Предназначено для определения временных характеристик проекта. При выполнении этой функции может быть выявлено несоответствие характеристик в требуемом техническом задании, что приводит к возврату на функцию ввода проекта.

- Конфигурация ПЛИС (программирование ПЛИС) – запись в микросхему ПЛИС требуемых настроек и точек соединения в матрице.

- Эксплуатация (использование)

Рисунок 37 - Типовой маршрут проектирования конфигурации ПЛИС – II.

Информация в лекции "1.3 Общая схема микропроцессора" поможет Вам.

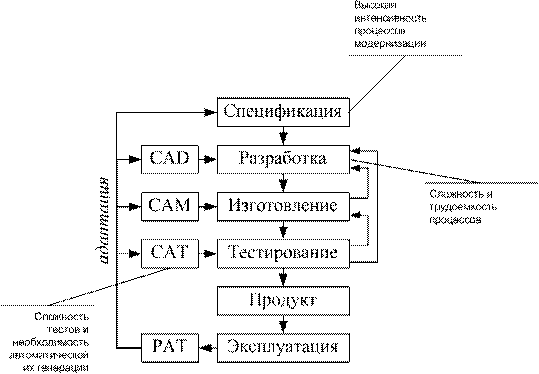

Рис. 38. Области инструментального ПО процесса проектирования устройств на ПЛИС

Рис. 39. Маршрут проектирования конфигурации ПЛИС при построении программно-управляемых устройств

Рис. 40. Использование IP-блоков