Электронная память

Лекция 9 Электронная память.

9.1 Классификация электронной памяти

9.1.1 Основная, или оперативная, память

9.1.2 Кэш-память

9.1.3 Постоянная память

9.1.4 Полупостоянная память

9.1.5 Буферная память

9.1.6 Внешняя электронная память

9.2 Быстродействие и производительность памяти.

Рекомендуемые материалы

9.3 Пакетный режим передачи данных.

9.4 Параметры памяти

9.5. Обнаружение и исправление ошибок

9.6 Организация памяти

9.7 Динамическая память.

9.7.1 Регенерация.

9.7.2.Типы динамической памят9.

9.7.3 Модули динамической памят9

9.8 Статическая память

9.9 Энергонезависимая память.

9.10 Флэш-память и EEPROM.

9.1 Классификация электронной памяти

Электронная память применяется практически во всех подсистемах РС, выступая в качестве оперативной памяти, кэш-памяти, постоянной памяти, полупостоянной памяти, буферной памяти, внешней памяти.

9.1.1 Основная, или оперативная, память

(Main Memory) компьютера используется для оперативного обмена информацией (командами и данными) между процессором, внешней памятью (например, дисковой) и периферийными подсистемами. Ее другое название — ОЗУ (оперативное запоминающее устройство) — примерно соответствует английскому термину RAM(Random Access Memory) — память с произвольным доступом.

Произвольность доступа подразумевает возможность операций записи или чтения с любой ячейкой ОЗУ в произвольном порядке. Требования, предъявляемые к основной памяти:

- большой (для электронной памяти) объем, исчисляемый уже десятками и даже сотнями мегабайт;

- быстродействие и производительность, позволяющие реализовать вычислительную мощность современных процессоров;

- высокая надежность хранения данных — ошибка даже в одном бите в принципе может привести к ошибкам вычислений, к искажению и потере данных, причем иногда и на внешних носителях.

9.1.2 Кэш-память

(Cache Memory) — сверхоперативная память (СОЗУ), является буфером между ОЗУ и ее «клиентами процессором (одним или несколькими) и другими абонентами системной шины. Кэш-память не является самостоятельным хранилищем, информация в ней не адресуема клиентами подсистемы памяти, присутствие кэша для них «прозрачно». Кэш хранит копии блоков данных тех областей ОЗУ, к которым происходили последние обращения, и весьма вероятное последующее обращение к тем же данным будет обслужено кэш-памятью существенно быстрее, чем оперативной памятью. От эффективности алгоритма кэширования зависит вероятность нахождения затребованных данных в кэш-памяти и, следовательно, выигрыш в производительности памяти и компьютера в целом.

9.1.3 Постоянная память

Используется для энергонезависимого хранения системной информации — BIOS таблиц знакогенераторов и т. п. Эта память при обычной работе компьютера только считывается, а запись в нее (часто называемая программированием) осуществляется специальными устройствами программаторами. Отсюда и ее название — ROM (Read Only Memory — память только для чтения) или ПЗУ (постоянное запоминающее устройство). Требуемый объем памяти этого типа невелик — например, BIOS РС/ХТ помещалась в 8 Кбайт, в современных компьютерах типовое значение — 128 Кбайт — 2 Мбайт. Быстродействие постоянной памяти обычно ниже, чем оперативной, но этот недостаток может быть исправлен применением теневой памяти. В последние годы постоянную память вытесняет флэш-память, запись в которую возможна в самом компьютере в специальном режиме работы, и другие типы энергонезависимой памяти (EPROM, FRAM).

9.1.4 Полупостоянная память

в основном используется для хранения информации о конфигурации компьютера. Традиционная память конфигурации вместе с часами - календарем (CMOS Memory и CMOS RTS) имеет объем несколько десятков байт, ESCD (Extended Static Configuration Data) — область энергонезависимой памяти, используемая для конфигурирования устройств Plug and Play— имеет объем несколько килобайт. Сохранность данных CMOS при отключении питания компьютера обеспечивается маломощной внутренней батарейкой или аккумулятором. В качестве полупостоянной применяется и энергонезависимая память — NV RAM (Non Volatile RAM), которая хранит информацию и при отсутствии питания.

9.1.5 Буферная память

различных адаптеров и контроллеров (коммуникационных, дисковых и пр.) обычно является разделяемой между процессором (точнее, абонентами системной шины) и контроллерами устройств. К этой памяти относятся и 16-байтные FIFO - буферы СОМ-портов, и 16-мегабайтные (и более) кэш-буферы высокопроизводительных SCSI-адаптеров. Специфическим типом буферной памяти является видеопамять дисплейного адаптера — к ней производятся интенсивные обращения со стороны центрального процессора и графического акселератора одновременно с непрерывным процессом регенерации изображения.

9.1.6 Внешняя электронная память

Применяется и в качестве накопителей Flash Drive для блокнотных ПК и автономных контроллеров и в других конструктивных исполнениях. Широкому распространению этих сверх быстродействующих «дисков» препятствует очень высокая на сегодняшний день стоимость хранения информации, а также довольно медленная запись.

9.2 Быстродействие и производительность памяти.

Быстродействие памяти определяется временем выполнения операций записи и считывания данных. Основными параметрами любых элементов памяти является минимальное время доступа и длительность цикла обращения. Время доступа (Access time) это временная задержка между запросом на выдачу какой-либо информации из памяти (начала цикла чтения) и появления действительных данных на выходе памяти (ее реальной выдачей). Длительность цикла определяется как минимальный период следующих друг за другом обращений к памяти, причем циклы чтения и записи могут требовать различных затрат времени. В цикл обращения кроме активной фазы самого доступа входит и фаза восстановления (возврата памяти к исходному состоянию), которая соизмерима по времени с активной фазой. Временные характеристики самих запоминающих элементов определяются их принципом действия и используемой технологией изготовления.

Основным фактором производительности оперативной памяти является ее пропускная способность, т.е. количество мегабайт в секунду, которое способна считать (записать) оперативная память.

9.3 Пакетный режим передачи данных.

Пакетный режим передачи (Burst Mode) предназначен для ускорения операций пересылки строк кэша в процессорах 486 и выше. Строка кэша процессора 486 имеет длину 16 байт, следовательно, для ее пересылки требуются четыре 32-разрядных шинных цикла. Для пересылки 32-байтной строки кэша Pentium требуются тоже четыре такта, поскольку разрядность передач составляет 64 бита. Использование кэша предполагает, что строка должна в нем присутствовать целиком. Пакетный цикл (Burst Cycle) оптимизирован именно для операций обмена внутреннего кэша с оперативной памятью.

Архитектура DRAM такова, что для получения доступа первый раз необходимо 5 тактов ожидания. Такт это один период электромагнитного колебания частоты, на которой работает память. Например: частота работы памяти 100МГц, время прохождения одного периода равен 1/100млн, то есть 10нс. Если не разбивать память на страницы и не пользоваться пакетным режимом доступа, то каждая следующая операция получения доступа к следующей ячейке памяти тоже будет занимать 5 тактов ожидания. Однако если использовать режимом burst, то, получив доступ первый раз, потратив на это 5 тактов ожидания, содержимое следующих ячеек можно считать, потратив на это лишь несколько тактов ожидания, т.е. в режиме FPM схема доступа имеет вид не 5-5-5-5, как у обычной DRAM, а 5-3-3-3. В этом и преимущество памяти типа FPM перед обычной DRAM. По нынешним меркам хорошим результатом является цикл 5-1-1-1 для частоты шины 100 или 133 МГц. Однако для процессоров Pentium 4, у которых за каждый такт синхронизации системной шины передается по четыре 64-битньтх слова данных, возможно, будет иной способ выражения производительности памяти.

9.4 Параметры памяти

Разрядность шины памяти — это количество байт (или бит), с которыми операция чтения или записи может быть выполнена одновременно. Разрядность основной памяти обычно согласуется с разрядностью внешней шины процессора (1 байт(8 бит) — для 8088; 2 байта(16 бит) — для 8086, 80286, 386SX; 4 байта(32 бита) — для 386DХ, 486; 8 байт(64 бит) — для Pentium и выше). Вполне очевидно, что при одинаковом быстродействии микросхем или модулей памяти производительность блока с большей разрядностью будет выше, чем у малоразрядного. Именно с целью повышения производительности у 32 - битных (по внутренним регистрам) процессоров Pentium и выше внешняя шина, связывающая процессор с памятью, имеет разрядность 64 бита.

Банком памяти называют комплект микросхем или модулей (а также их посадочных мест — «кроваток» для микросхем, слотов для SIMM или DIMM), обеспечивающий требуемую для данной системы разрядность хранимых данных. Работоспособным может быть только полностью заполненный банк. Внутри одного банка практически всегда должны применяться одинаковые (по типу и объему) элементы памяти

В компьютерах на 486-х процессорах банком является один SIMM-72 или четверка SIMM-30. В компьютерах на процессорах 5-6 (а для AMD и 7-го) поколений банком может быть пара SIMM-72 или один модуль DIMM или RIMM (эти модули могут содержать и несколько банков). На платы с чипсетом i850 для процессора Pentium 4 требуется установка пары RIMM (16-бит).

Микросхемы памяти SDRAM имеют внутреннюю многобанковую организацию, применительно к этой памяти в данном контексте (комплекте микросхем...) используют понятие физический банк или ряд (row).

Достоверность хранения данных и технологии защиты от сбоев.

Отказ ячейки памяти — потеря ее работоспособности, обычно требующая замены элемента памяти. Отказ может быть устойчивым, но возможно и самопроизвольное восстановление работоспособности, например, после повторного включения питания. Часто причиной отказов является неисправность контакта или нарушение условий эксплуатации.

Случайный сбой может произойти и в исправной микросхеме памяти, например, при пролете через неё ионизирующей частицы (по этой причине в условиях высокого уровня радиации обычные электронные элементы неработоспособны). После сбоя, следующая же запись в ячейку произойдет нормально.

9.5. Обнаружение и исправление ошибок

ЕСС (Error Checking and Correcting - схема обнаружения и исправлении ошибок в памяти) в основном применяется в компьютерах, где надо добиться надежной работы. Даже при отсутствии ошибки нужен, по крайней мере, один лишний такт для срабатывания схемы контроля, разрешающей использование считанных данных. Таким образом, ЕСС - память будет работать несколько медленнее неконтролируемой, и при наличии исправимых ошибок замедление будет более заметным. Функцию контроля и исправления выполняет чипсет, его реакцию на ошибки обычно можно задать настройками CMOS Setup. Возможны различные варианты поведения, например:

- автоматически исправлять ошибки, не уведомляя об этом систему;

- исправлять однократные ошибки, уведомляя систему только о многократных;

- не исправлять ошибки, а только уведомлять об их обнаружении (самый достоверный контроль).

Разумеется, что память с ECC стоит заметно дороже обычной памяти и находит применение в первую очередь в серверах.

В современных компьютерах ЕСС широко применяется в кэш-памяти. В процессорах Р6 и выше встроенный вторичный кэш, как правило, имеет ЕСС - контроль, выполняемый схемами процессора. При «разгоне» процессора ЕСС - контроль может подтормаживать кэш, в котором начинают появляться ошибки, но отключение ЕСС - контроля (настройками CMOS Setup) ради ускорения чревато неконтролируемыми ошибками.

Проверка контрольной суммы (Checksum) — обычно это байт, дополняющий каждые 256 байт контролируемой области. Применяется для проверки достоверность информации, хранимой в постоянной (ROM BIOS) и полупостоянной (CMOS RTC, ESCD) памяти. Проверка контрольной суммы обычно выполняется однократно во время включения компьютера.

Кэширование оперативной памяти.

Основная память компьютеров реализуется на относительно медленной динамической памяти (DRAM), обращение к ней приводит к простою процессора - появляются такты ожидания (wait states). Статическая память (SRAM), построенная, как и процессор, на триггерных ячейках, по своей природе способна догнать современные процессоры по быстродействию и сделать ненужными такты ожидания (или хотя бы сократить их количество). Разумным компромиссом для построения экономичных и производительных систем явился иерархический способ организации оперативной памяти. Идея заключается в сочетании основной памяти большого объема на DRAM с относительно небольшой кэш-памятью на быстродействующих микросхемах SRAM.

9.6 Организация памяти.

Чипы памяти принято обозначать в виде AxB (например, 4х4). Такое обозначение значит, что чип имеет А Мбит адресного пространства (или попросту адресов), по каждому из которых можно сохранить B бит информации (при чтении/записи каждый из этих битов требует отдельной линии ввода/вывода). Емкость чипа соответственно - произведение А и В. Например: обозначение 1х4 означает, что данный чип имеет 1 мегабит. по каждому из которых можно сохранить 4 бита информации. Емкость чипа, таким образом, составляет 4 мегабит, то есть результат умножения в формуле 1х4. (Обратите внимание, емкость чипов принято называть в мегабитах, емкость модулей - в мегабайтах). Точно так же чип 256х16 (256 в данном случае килобит) имеет емкость те же 4 мегабит. Наконец, шестнадцати мегабитными являются, например, чипы 4х4 и 1х16.

9.7 Динамическая память.

Динамическая память — DRAM (Dynamic RAM) — получила свое название от принципа действия ее запоминающих ячеек, которые выполнены в виде конденсаторов, образованных элементами полупроводниковых микросхем. Несколько упрощая описание физических процессов, можно сказать, что при записи логической единицы в ячейку конденсатор заряжается, при записи нуля — разряжается. Схема считывания разряжает через себя этот конденсатор, и, если заряд был ненулевым, выставляет на своем выходе единичное значение и подзаряжает конденсатор до прежнего уровня. При отсутствии обращения к ячейке со временем за счет токов утечки конденсатор разряжается и информация теряется, поэтому такая память требует постоянной периодической подзарядки конденсаторов (обращения к каждой ячейке) — память может работать только в динамическом режиме.

9.7.1 Регенерация.

Поскольку обращения (запись или чтение) к различным ячейкам памяти обычно происходят в случайном порядке, то для поддержания сохранности данных применяется регенерация (Memory Refresh — «освежение» памяти) — регулярный циклический перебор ее ячеек (обращение к ним) с холостыми циклами. Регенерация в микросхеме происходит одновременно по всей строке матрицы при обращении к любой из ее ячеек. Максимальный период обращения к каждой строке TRF (refresh time) для гарантированного сохранения информации у современной памяти лежит в пределах 8-64 мс. В зависимости от объема и организации матрицы для однократной регенерации всего объема требуется 512, 1024, 2048 или 4096 циклов обращений. При распределенной регенерации (distributed refresh) одиночные циклы регенерации выполняются равномерно с периодом, который для стандартной памяти принимается равным 15,6 мкс. Период этих циклов называют «refresh rate», хотя такое название больше подошло бы к обратной величине — частоте циклов f=l/tRF. Для памяти с расширенной регенерацией (extended refresh) допустим период циклов до 125 мкс. Возможен также и вариант пакетной регенерации (burst refresh), когда все циклы регенерации собираются в пакет, во время которого обращение к памяти по чтению и записи блокируется. При количестве циклов 1024 эти пакеты будут периодически занимать шину памяти примерно на 130 мкс, что далеко не всегда допустимо.

9.7.2.Типы динамической памяти.

Асинхронная память.

FPM DRAM.

Первой, нашедшей применение в PC модификацией DRAM, была память, которая работала в режиме быстрого страничного обмена FPM (Fast Page Mode) или просто режиме страничного обмена (Page Mode. Чтобы сократить время ожидания на выборку данных (на доступ) стандартная память DRAM разбивается на страницы. Обычно для доступа к данным в памяти требуется указать строку и столбец адреса, что занимает некоторое время. Разбиение на страницы обеспечивает более быстрый доступ ко всем данным в пределах данной строки памяти, то есть изменяется лишь номер столбца, но не номер строки, это позволяет повысить производительность памяти. Для памяти с временем доступа 60 нс время цикла обмена внутри страницы может быть сокращено до 35 нс.

EDO DRAM.

Начиная с 1995 года, в PC используется новый тип оперативной памяти - EDO (Extended или Enhanced Data Out), этот режим иногда называют гиперстраничным режимом обмена HPM (Hyper Page mode). Это усовершенствованный тип памяти FPM. Микросхемы памяти EDO учитывают перекрытие синхронизации между очередными операциями доступа. За счет этого удается частично совместить по времени следующий цикл чтения с предыдущим, то есть чипсет при работе с EDO памятью может начать выполнение новой команды выборки столбца, пока данные считываются по текущему адресу, за счет чего еще уменьшаются задержки на получение доступа.

EDO со временем доступа 60-70 нс в режиме гиперстраничного обмена при частоте системной шины 66 МГц может обеспечить лучший пакетный цикл чтения 5-2-2-2, то есть на четырех операциях считывания тратится не 14, а 11 тактов. Благодаря простоте данного усовершенствования при одном и том же времени доступа запоминающих элементов цена EDO-памяти почти не отличается от цены стандартной памяти.

Микросхемы EDO DRAM применяются в модулях SIMM-72 и DIMM, эти модули конструктивно и по назначению выводов совместимы со стандартными модулями (FPM).

BEDO DRAM. Результатом дальнейшего развития конвейерной архитектуры модулей памяти явилась память BEDO DRAM (Burst EDO). В микросхемах данного типа содержится еще и внутренний счетчик адреса колонок для пакетного цикла. Цикл чтения 5-1-1-1 для BEDO-памяти со временем доступа 60 нс при частоте шины до 66 МГц. Задержка появления первых данных пакетного цикла окупается повышенной частотой приема последующих.

BEDO применяется в модулях SIMM-72 и DIMM, но поддерживается далеко не всеми чипсетами.

Синхронная память.

SDRAM.

Уже начиная с 1997 года на смену памяти типа FPM, EDO и BEDO приходит новый тип оперативной памяти - SDRAM (Synchronous DRAM) - синхронная DRAM. Эффективность SDRAM намного выше, чем у ее предшественников. Схема пакетного чтения у SDRAM обеспечивает цикл 5-1-1-1. То есть для считывания четырех значений подряд задержка для памяти типа FPM составит 5+3+3+3=14 тактов, у EDO 5+2+2+2=11 тактов, а у BEDO и SDRAM 5+1+1+1=8 тактов И если впервые SDRAM применяли в PC на частоте 66 МГц (как FPM, EDO и BEDO в то время), то затем были разработаны чипы SDRAM, работающие на частоте 100 МГц, а после и 133 МГц. При этом нужно отметить, что увеличение тактовой частоты памяти увеличила не только пропускную способность, но и уменьшило время доступа.

DDR SDRAM.

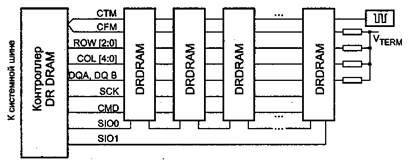

Память DDR SDRAM (Dual Data Rate — удвоенная скорость данных) представляет собой дальнейшее развитие и по многим параметрам и способам изготовления мало, чем отличается от обычной памяти SDRAM. Та же синхронизация шины памяти с системной шиной, практически то же производственное оборудование, энергопотребление, почти не отличающееся от SDRAM, площадь чипа больше лишь на несколько процентов. Это позволило сразу без значительных материальных и временных издержек создать новую быстродействующую память, причем по цене, мало отличающейся от обычной памяти SDRAM (DDR SDRAM иногда называют SDRAM-II). Как и следует из названия, у микросхем DDR SDRAM данные внутри пакета передаются с удвоенной скоростью — они переключаются по обоим фронтам синхроимпульсов. На частоте 100 МГц DDR SDRAM имеет пиковую производительность 200 Мбит/пин, что в составе 8-байтных модулей DIMM дает производительность 1600 Мбайт/с. На высоких тактовых частотах (100 - 133 МГц) двойная синхронизация предъявляет очень высокие требования к точности временных диаграмм. DR DRAM (Rambus).Память RDRAM (Rambus DRAM) И так рассмотрим принцип работы DR DRAM. Канал RDRAM (Rambus Channel) представляет собой последовательно-параллельную шину. Такой подход позволил ограничить количество линий интерфейса, что позволяет упорядочить разводку проводников ради повышения частоты передачи сигналов. Небольшое количество сигналов обеспечивает возможность применить сверхбыстродействующие интерфейсные схемы. Также один канал памяти Rambus может поддерживать до 32 отдельных устройств RDRAM (микросхем RDRAM), которые устанавливаются в модули RIMM (Rambus Inline Memory Modules). Вся работа с памятью организуется между контроллером памяти и отдельным (а не всеми) устройством. Каждые 7,5 нс. (133МГц) одна микросхема RDRAM может передавать 16 байт. Для увеличения производительности было предложено еще одно конструктивное решение - передача управляющей информации отделена от передачи данных по шине. Для этого предусмотрены независимые схемы управления, а на адресной шине

|

Рис. 11. Память Direct RDRAM

выделены две группы контактов: для команд выбора строки и столбца и для передачи данных по двум фронтам тактового сигнала, то есть дважды в тактовом импульсе (DDR). Правая граница тактового импульса называется четным циклом, а левая — нечетным циклом.

Обязательным «фирменным» компонентом ОЗУ на RDRAM является контроллер памяти. В его задачу входит обслуживание микросхем памяти, установленных в канале, по запросам, поступающим со стороны интерфейса системной шины компьютера. В соответствии со спецификацией RDRAM, в одном канале может быть до трех слотов под RIMM, и их интерфейсные линии соединяются змейкой. В слоты могут устанавливаться RIMM различной емкости (64 - 512 Мбайт).

VC DRAM.

Идея архитектуры памяти с виртуальными каналами (Virtual Channel Memory Architecture, не путать с виртуальной памятью) заключается в помещении между массивом запоминающих ячеек и внешним интерфейсом микросхемы памяти набора канальных буферов. При этом операции обмена данными разделяются на два процесса: «фасадный» обмен данными с каналами и «тыловой» обмен между каналами и массивом запоминающих ячеек. Оба процесса выполняются по командам со стороны внешнего интерфейса, почти независимо друг от друга.

9.7.3 Модули динамической памяти.

В самые первые персональные компьютеры память устанавливали непосредственно чипами. Разумеется, такой подход имеет ряд недостатков. Во-первых, установка множества чипов памяти на материнскую плату неэффективна с точки зрения использования свободного места; во-вторых, каждый устанавливаемый чип содержит много гибких контактов, таким образом, уменьшается надежность, так как отсутствие контакта хотя бы у одного чипа приводит к неработоспособности всей системы.

Динамическая память чаще всего применяется в виде модулей с разрядностью 8, 16, 32 или 64 бит, которые могут устанавливаться пользователем без каких-либо приспособлений. Модули стандартизованы, поэтому обеспечивается взаимная совместимость.

- SIPP и SIММ-30 — самые первые модули с 8-битной организацией, применялись вплоть до 486-х процессоров.

- SIMM-72-pin — 32-битные модули, применявшиеся на системных платах для 486 и Pentium.

- DIMM-168 — 64-битные модули для Pentium и выше. Существует два поколения, различные по интерфейсу. Модули DIMM 168-pin Buffered (1-го поколения), как и слоты для них, встречаются редко и с широко распространенными модулями DIMM 2-го поколения несовместимы даже механически (по ключам). Наиболее популярно второе поколение с микросхемами SDRAM. Различают модификации в зависимости от наличия буферов или регистров на управляющих сигналах: Unbuffered, Buffered и Registered.

- DIMM-184 — 64-битные модули DDR SDRAM для системных плат 6-7 поколений процессоров.

- RIMM — 16 или 32-байтные модули RDRAM для системных плат 6-7 поколений процессоров.

- SO DIMM (72 и 144-pin) и SO RIMM — малогабаритные варианты модулей (для блокнотных ПК).

- AIMM (AGP Inline Memory Module), они же GPA Card (Graphics Performance Accelerator) — 66-контактные 32- или 16-битные модули SDRAM, предназначенные для расширения памяти графических адаптеров, встроенных в системную плату.

Существуют еще модули SIMM-68 для Macintosh и к IBM PC они не подходят. В компьютерах, предназначенных для применения в качестве серверов или мощных станций, нередко применяются специальные платы памяти, позволяющие устанавливать большие объемы ОЗУ. На такие платы также устанавливаются модули SIMM, DIMM или SO DIMM. Модули памяти применяются и в принтерах (лазерных) — DIMM-168, 100-Pin DIMM, AIMM, SO DIMM-144, но иногда для них требуются и специальные модули.

Современные модули памяти имеют шину данных разрядностью 8, 32 или 64 бит. Кроме основных информационных бит модули могут иметь дополнительные контрольные биты с различной организацией.

- Модули без контрольных бит (non Parity) имеют разрядность 8, 32 или 64 бита и допускают независимое побайтное обращение с помощью отдельных для каждого байта линий CAS#.

- Модули с контролем паритета (Parity) имеют разрядность 9, 36 или 72 бита и также допускают независимое побайтное обращение, контрольные биты по обращению приписаны к соответствующим байтам.

- Модули с генератором паритета (Fake Parity, Parity Generator, Logical Parity) также допускают независимое побайтное обращение, логические генераторы паритета по чтению приписаны к соответствующим байтам. Действительного контроля памяти они не обеспечивают.

- Модули с контролем по схеме ЕСС имеют разрядность 36, 40, 72 или 80 бит. Обычно они допускают побайтное обращение к информационным битам, но контрольные биты у них привязаны к одному или нескольким сигналам CAS#, поскольку ЕСС подразумевает обращение сразу к целому слову.

- ECC-Optimized — модули, оптимизированные под режим ЕСС. От обычных модулей ЕСС они отличаются тем, что могут не обеспечивать побайтное обращение к информационным битам.

- ECC-on-SIMM (EOS) — модули со встроенной схемой исправления ошибок. Каждый байт модуля имеет встроенные средства контроля и исправления ошибок, работающие прозрачно. Для системы модули функционируют как обычные паритетные — в случае обнаружения неисправимой ошибки они генерируют ошибочный бит паритета. Эти модули обеспечивают отказоустойчивость по памяти (Kill Protected Memory) для системных плат, поддерживающих только контроль паритета.

* В столбце «Разрядность» в скобках указана разрядность с учетом битов паритета или ECC.

Модули SIPP и SIMM.

Модули SIMM (Single In-Line Memory Module) и SIPP (Single In-Line Pin Package) представляют собой небольшие печатные платы с односторонним краевым разъемом. Контактами модулей SIMM являются позолоченные (или покрытые специальным сплавом) площадки, расположенные на обеих поверхностях вдоль одной из сторон. Слово Single (одиночный) в названии подразумевает, что пары площадок на обеих сторонах эквивалентны (электрически соединяются между собой). У малораспространенных модулей SIPP контакты штырьковые (pin — иголка), эти контакты при необходимости можно припаять к площадкам модулей SIMM (такие контакты когда-то даже продавались в комплекте с модулями SIMM). Модули SIPP оказались непрактичными — их контакты не выдерживают транспортировки и многократной установки.

SIPP, SIMM 30 pin.

«Короткие», или SIMM 30-pin, модули SIMM (старый тип) имеют 30 печатных выводов и однобайтную организацию (рис. 12). Разводка выводов у модулей фирмы IBM (для компьютеров IBM PS/2) отличается от общепринятых стандартных. Различия делают несовместимыми модули с объемом более 1 Мбайт: модули IBM могут быть двусторонними (2 Мбайт), стандартные — только односторонними. Малораспространенные модули SIPP имеют 30 штырьковых выводов и совпадают по разводке со стандартными SIMM 30-pin (SIMM-30).

Рис. 12. Модули SIMM-30

Разрядность модуля SIMM 30 pin составляет 8 бит (9 бит, последний девятый бит используется для передачи бита четности). Модуль SIMM 30 pin использовался в 286, 386 и 486 системах. Правда применение 8-битных модулей особенно в 32-битных системных платах сильно сковывает свободу выбора объема памяти.

Также этот модуль имеет так называемый ключ - вырез сбоку со стороны 1-го контакта, который служит для правильной ориентации модуля.

SIMM 72 pin.

Неудобства использования 30 pin SIMM в системах 386 и 486 вполне очевидны: банк памяти состоит из четырех модулей. Поэтому был разработан новый тип модуля.

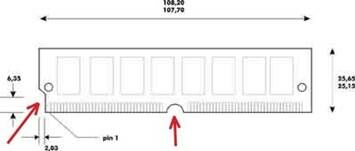

«Длинные», или SIMM 72-pin, модули SIMM имеют 72 печатных вывода (рис. 13) и 32-битную организацию. В односторонних модулях (1, 4, 16, 64 Мбайт — 1 банк) используется только одна пара сигналов выборки RASO# и RAS2#, в двусторонних (2, 8, 32 Мбайт -2 банка) — две пары сигналов RAS#. Заметим, что использование всеми модулями обеих пар линий RAS# поддерживается не всеми системными платами. Контрольные биты модулей с паритетом по выборке приписываются к соответствующим байтам, в ЕСС - модулях возможны различные варианты. Модули без паритета имеют разрядность 32 бит, с паритетом — 36 бит, модули ЕСС — 36 или 40 бит. Модули ЕСС-36 и ЕСС-40 (ECC - optimised) не допускают побайтного обращения и существенно отличаются от 32-битных и паритетных модулей.

Рис. 13. Модули SIMM-72

Этот модуль имеет 2 ключа - аналогичный 30 pin SIMM вырез со стороны 1-го контакта, а также вырез посередине между 36-м и 37-м контактами.

Модули DIMM.

Модули DIMM (Dual In-Line Memory Module) в отличие от модулей SIMM представляют собой печатные платы с двухсторонним краевым разъемом. Слово Dual (двойной) в названии подразумевает, что пары площадок на обеих сторонах электрически независимы друг от друга.

DIMM-168 pin SDRAM.

С выходом процессора Pentium, у которого ширина шины память - процессор увеличивается до 64 бит, снова возникает ситуация, когда банк не равен модулю. В Pentium-системы память при использовании 72pin SIMM снова необходимо устанавливать парами. Для решения этой проблемы, а точнее для применения уже упоминавшейся нами SDRAM, был разработан новый тип модуля – DIMM-168.

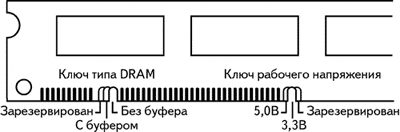

Модуль памяти DIMM (Dual-In-line-Memory Module) имеет 168 независимых печатных выводов, расположенных с обеих сторон (контакты 1-84 — с фронтальной стороны, 85-168 — с тыльной). Разрядность шины данных — 64 бит, организация рассчитана на применение в компьютерах с 32- и 64-битной шиной данных. Конструкция и интерфейс модулей соответствует стандарту JEDEC 21-С. Модули выпускаются для напряжения питания 3,3 и 5 В. Вид модулей и сочетания ключей представлены на рис. 14.

Рис. 14. Модуль DIMM-168

Модуль DIMM 168 pin имеет 2 ключа, между 10 и 11 и между 40 и 41 контактами. Эти ключи, кроме того, что служат для правильной ориентации модуля, ещё и несут определенную информацию своим расположением - первый ключ различает модули с буферизацией и без неё, второй ключ говорит о напряжении питания модуля.

По внутренней архитектуре модули близки к SIMM-72, но имеют удвоенную разрядность и, соответственно, удвоенное количество линий CAS#. Также удвоено число сигналов разрешения записи и разрешения выходных буферов позволяет организовывать модули в виде двух 4-байтных банков с возможностью их чередования (Bank Interleaving). Модули могут иметь разрядность 64, 72 или 80 бит, дополнительные разряды 72-битных модулей организуются либо по схеме контроля паритета (приписываясь к соответствующим байтам), либо по схеме ЕСС; 80-битные — только по схеме ЕСС.

Модули DIMM второго поколения отличаются тем, что позволяют использовать микросхемы как асинхронной (FPM и EDO), так и синхронной динамической памяти (SDRAM). Внешне они похожи на модули первого поколения, но отличаются ключом, не допускающим ошибочную установку. Унифицированное назначение выводов позволяет в одни и те же слоты устанавливать как модули DRAM, так и SDRAM. Нумерация бит данных единая для всех типов организации — контрольные биты имеют отдельную нумерацию, их наличие зависит от организации (паритет, ЕСС-72, ЕСС-80).

В модулях применена последовательная идентификация параметров на двухпроводном интерфейсе (12С) для чтения атрибутов (идентификации) из специальной конфигурационной памяти SPD (обычно EEPROM 24C02), установленной на модулях.

168-pin Unbuffered DIMM — модули, у которых все цепи не буферизованы (одноименные адресные и управляющие сигналы микросхем соединены параллельно и заводятся прямо с контактов модуля). Эти модули сильнее нагружают шину памяти, но позволяют добиться максимального быстродействия. Они предназначены для системных плат с небольшим (1-4) количеством слотов DIMM или имеющих шину памяти, буферизованную на плате. Модули выполняются на микросхемах DRAM или SDRAM. Высота модулей не превышает 51 мм. Объем 8-512 Мбайт.

168-pin Registered DIMM — модули синхронной памяти (SDRAM), у которых адресные и управляющие сигналы буферизованы регистрами, синхронизируемыми тактовыми импульсами системной шины. За счет регистров эти модули меньше нагружают шину памяти, что позволяет набирать больший объем памяти. Применение регистров повышает точность синхронизации, что позволяет повысить тактовую частоту. Однако регистр вносит дополнительный такт задержки. По виду этот тип DIMM легко отличим — кроме микросхем памяти и EEPROM на них установлено несколько микросхем регистров-защелок. Объем 64-1024 Мбайт

DIMM-184 pin DDR SDRAM.

Увеличение пропускной способности памяти вдвое повлекло за собой изменением форм-фактора модулей. При сохранении тех же размеров модуля число контактов увеличилось со 168 до 184. Изменившееся положение ключа не позволит вставить модули DIMM DDR SDRAM в разъемы DIMM, предназначенные для обычной памяти SDRAM.

Модули DIMM-184 предназначены для работы с памятью DDR SDRAM. По габаритам они аналогичны модулям DIMM-168, но у них имеются дополнительные вырезы по бокам и отсутствует левый ключ. Разрядность — 64 или 72 бит (ЕСС), имеются варианты с регистрами в адресных и управляющих цепях (Registered DDR SDRAM) и без них. Напряжение питания — 2,5 В. Идентификация последовательная. Состав сигналов в основном повторяет набор для DIMM SDRAM.

Стандарт модулей DIMM DDR SDRAM предполагает использование чипов с частотой до 200 МГц с результирующей частотой 400 МГц и пропускной способностью 3.2 Гб/с. - как у двухканальной памяти Direct Rambus DRAM. Также появились двухканальные чипсеты для работы с DDR SDRAM - это увеличило производительность до 6,4 Гб/с. при использовании модулей PC3200.

DIMM-230 pin DDR-II SDRAM.

Вскоре предполагается введение нового стандарта - DDR-II(QDR). Скорость DDR-II чипов, как предполагается, начнется со 100 МГц, но за счет того, что будет передаваться уже 4 пакета данных за такт, их пропускная способность также должна составить 3.2 Гб/с. Учитывая такой принцип работы (передачу 32 байтов за такт) рост производительности DDR-II чипов при росте тактовой частоты будет максимальным - в 4 раза: 150 МГц даст уже 4.8 Гб/с, а 200 МГц - 6.4 Гб/с. Модули на этих чипах также будут иметь свой собственный форм - фактор (230 контактов), и требовать новых чипсетов.

Модули RIMM.

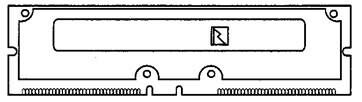

RIMM-184 pin (16 битные).

Модули RIMM (Rambus Interface Memory Module), no форме похожие на обычные модули памяти (рис. 15), специально предназначены для памяти RDRAM. У них 30-проводная шина проходит вдоль модуля слева направо, и на эту шину без ответвлений напаиваются микросхемы RDRAM в корпусах BGA. Модуль RIMM содержит до 32 микросхем RDRAM, которые всеми выводами (кроме двух) соединяются параллельно. Микросхемы памяти закрыты пластиной радиатора. В отличие от SIMM и DIMM, у которых объем памяти кратен степени числа 2, модули RIMM могут иметь более равномерный ряд объемов — в канал RDRAM память можно добавлять хоть по одной микросхеме.

Рис. 15. Модули RIMM

Подсистема памяти Rambus представляет собой непрерывный канал, что приводит к необходимости заполнения всех разъёмов установленных на плате, поэтому были также выпущены так называемые CRIMM (Continuiti RIMM) - специальные модули, единственное назначение которых - продолжить электрические связи в канале памяти. Эти модули не имеют микросхем памяти, и обычно идут в комплекте с материнскими платами.

RIMM-232 pin (32 битные).

Также недавно, несмотря на не удачу с 16-битными модулями RIMM, было объявлено о выпуске новых двухканальных 32-битных RIMM. Новые 232-контактные модули PC3200 имеют тактовую частоту 400МГц и максимальную скорость передачи данных 3,2 Гб/с. и PC4200 с частотой 533МГц и с максимальной скоростью передачи данных 4,2 Гб/с. Фирма Intel не скрывает, что фактически эти два модуля являются аналогами старых PC800 и PC1066, только, для удобства, с увеличиной в два раза шиной. Новые модули будут выпускаться емкостью 128 Мб, 256 и 512 Мб.

На сегодняшний день модули RIMM, в основном из за своей цены, массовой популярности не приобрели, и в основном применяется в серверных решениях фирмы Intel.

9.8 Статическая память.

Статическая память — SRAM (Static Random Access Memory), как и следует из ее названия, способна хранить информацию в статическом режиме — то есть сколь угодно долго при отсутствии обращений (но при наличии питающего напряжения). Ячейки статической памяти реализуются на триггерах — элементах с двумя устойчивыми состояниями. По сравнению с динамической памятью эти ячейки более сложные и занимают больше места на кристалле, однако они проще в управлении и не требуют регенерации. Быстродействие и энергопотребление статической памяти определяются технологией изготовления и схемотехникой запоминающих ячеек. Самая экономичная КМОП - память (CMOS Memory) имеет время доступа более 100 наносекунд, но зато пригодна для длительного хранения информации при питании от маломощной батареи, что и применяется в памяти конфигурации PC. Самая быстродействующая статическая память имеет время доступа несколько наносекунд, что позволяет ей работать на частоте системной шины процессора, не требуя от него тактов ожидания. Типовой объем памяти современных микросхем SRAM достигает 1 Мбит. В PC микросхемы SRAM в основном применяются для построения вторичного кэша; они могут располагаться как на системной плате, на картридже процессора так и в самом процессоре. Разновидности статической памяти — Async SRAM, Sync Burst SRAM и Pipelined Burst SRAM — рассмотрим именно с точки зрения этого применения.

9.9 Энергонезависимая память.

Обобщенное понятие энергонезависимой памяти (NV Storage) включает в себя любое устройство, хранящее записанные данные даже при отсутствии питающего напряжения (в отличие от статической и динамической полупроводниковой памяти), В данном разделе рассматриваются только электронные устройства энергонезависимой памяти, хотя к энергонезависимой памяти относятся и устройства с подвижным магнитным или оптическим носителем. Существует множество типов энергонезависимой памяти: ROM, PROM, EPROM, EEPROM, Flash Memory, FRAM, различающихся по своим потребительским свойствам, обусловленным способом построения запоминающих ячеек и сферам применения. Запись информации в энергонезависимую память, называемая программированием, обычно существенно сложнее и требует больших затрат времени и энергии, чем считывание.

- Микросхемы, программируемые при изготовлении, — масочные ПЗУ, содержимое которых определяется рисунком технологического шаблона. Такие микросхемы используют лишь при выпуске большой партии устройств с одной и той же прошивкой.

- Микросхемы, программируемые однократно после изготовления перед установкой в целевое устройство, — ППЗУ (программируемые ПЗУ) или PROM (Programmable ROM). Программирование осуществляется прожиганием определенных хранящих элементов на специальных устройствах-программаторах.

- Микросхемы, стираемые и программируемые многократно, — РПЗУ (ре-программируемые ПЗУ) или EPROM (Erasable PROM — стираемые ПЗУ). Для стирания и программирования требуется специальное оборудование. Микросхемы программируются в программаторе. Иногда возможно программирование микросхем прямо в целевом устройстве, подключая внешний программатор, — так называемый метод ОВР (On-Board Programming). Наиболее распространены микросхемы УФРПЗУ, стираемые ультрафиолетовым облучением, — их обычно называют просто EPROM или UV-EPROM (Ultra-Violet EPROM). В этом классе имеются и электрически стираемые ПЗУ (ЭСПЗУ) или EEPROM (Elecrical Erasable PROM).

- Микросхемы, перепрограммируемые многократно в целевом устройстве, используя программу его процессора, — так называемый метод ISW (In-System Write). К этому классу относятся чисто электрически перепрограммируемые микросхемы NVRAM и FRAM, но наибольшее распространение получила флэш-память.

Энергонезависимая память в основном применяется для хранения неизменяемой (или редко изменяемой) информации — системного программного обеспечения (BIOS), таблиц (например, знакогенераторов графических адаптеров), памяти конфигурации устройств (ESCD, EEPROM адаптеров). Эта информация обычно является ключевой для функционирования PC (без BIOS компьютер представляет собой только коробку с дорогими комплектующими), поэтому весьма существенна забота о ее сохранности и предотвращении несанкционированного изменения.

NVRAM (Non-Volatile Random Access Memory) — энергонезависимая память с произвольным доступом. Это название подразумевает возможность произвольной смены информации не только во всей ее области или блоке, но и в отдельной ячейке, причем не процедурой, а обычным шинным циклом. К этому классу относятся микросхемы FRAM и EEPROM.

FRAM (Ferroelectric RAM) — ферроэлектрическая энергонезависимая память с истинно произвольным доступом, запись и чтение ее осуществляется как в обычных микросхемах статической памяти. При ее изготовлении используется железо — ее можно считать эхом старинной памяти на магнитных сердечниках больших машин. Ячейки FRAM по структуре напоминают DRAM, но информация хранится не в виде заряда конденсатора (который нужно поддерживать регенерацией), а в виде направления поляризации кристаллов. Запись производится непосредственно, предварительного стирания не требуется. Как и флэш-память, она используется в самых портативных системах класса PDA (personal digital assistants — персональный цифровой ассистент

Постоянная и полупостоянная память — ROM, PROM, EPROM.

Масочные постоянные запоминающие устройства — ПЗУ, или ROM, — имеют самое высокое быстродействие (время доступа 30-70 не). Эти микросхемы в PC широкого применения не получили ввиду сложности модификации содержимого (только путем изготовления новых микросхем), они иногда применялись в качестве знакогенераторов в некоторых моделях графических адаптеров CGA, MDA, HGC.

Однократно программируемые постоянные запоминающие устройства — ППЗУ, или PROM, имеют аналогичные параметры и благодаря возможности программирования изготовителем оборудования (а не микросхем) находят более широкое применение для хранения кодов BIOS материнских плат и в графических адаптерах. Программирование этих микросхем осуществляется только с помощью специальных программаторов, в целевых устройствах они устанавливаются в «кроватки» или запаиваются. Как и масочные, эти микросхемы практически нечувствительны к электромагнитным полям (в том числе, и к рентгеновскому облучению), и несанкционированное изменение их содержимого в устройстве исключено (конечно, не считая отказа).

Репрограммируемые постоянные запоминающие устройства — РПЗУ, или EPROM, до недавних пор были самыми распространенными носителями BIOS как на системных платах, так и в адаптерах, а также использовались в качестве знакогенераторов. Наиболее популярные микросхемы имеют восьмибитную организацию и используемые для микросхем CMOS. Шестнадцатибитные микросхемы в PC применяются редко.

Отметим основные свойства EPROM.

- Стирание информации происходит сразу для всей микросхемы под воздействием облучения и занимает несколько минут. Стертые ячейки имеют единичные значения всех бит.

- Запись может производиться в любую часть микросхемы побайтно, в пределах байта можно маскировать запись отдельных бит, устанавливая им единичные значения данных.

- Защита от записи осуществляется подачей низкого (5В) напряжения на вход Vpp в рабочем режиме (только чтение).

- Защита от стирания производится заклейкой окна.

9.10 Флэш-память и EEPROM.

Микросхемы EEPROM относительно небольшого объема широко применяются в качестве энергонезависимой памяти конфигурирования различных адаптеров. Современные микросхемы EEPROM имеют довольно сложную внутреннюю структуру, в которую входит управляющий автомат. Это позволяет упростить внешний интерфейс, делая возможным непосредственное подключение к микропроцессорной шине или иному интерфейсу, и скрыть специфические (и ненужные пользователю) вспомогательные операции типа стирания и верификации. Микросхемы EEPROM позволяют считывать и перезаписывать (стирать) любую ячейку памяти, но перезапись требует довольно много времени.

Флэш-память по определению относится к классу EEPROM (электрическое стирание), но использует особую технологию построения запоминающих ячеек. Стирание во флэш-памяти производится сразу для целой области ячеек (блоками или полностью всей микросхемы). Это позволило существенно повысить производительность в режиме записи (программирования). Флэш-память обладает сочетанием высокой плотности упаковки (ее ячейки на 30 % меньше ячеек DRAM), энергонезависимого хранения, электрического стирания и записи, низкого потребления, высокой надежности и невысокой стоимости. Каждая ячейка флэш-памяти состоит всего из одного униполярного (полевого) транзистора. Ячейки организованы в матрицу; разрядность данных внешнего интерфейса — 8 или 16 бит (ряд микросхем имеет переключаемую разрядность). Чистые (стертые) ячейки содержат единицу во всех битах; при записи (программировании) нужные биты обнуляются.

Синхронная флэш-память имеет интерфейс (и даже упаковку в корпуса), совпадающий с SDRAM. В настоящее время выпускаются микросхемы с частотой 66 МГц, ожидаются микросхемы и на 133 МГц. Такая память удобна для применения во встраиваемых компьютерах для хранения ПО, исполняемого прямо на месте (без копирования в ОЗУ).

Для хранения BIOS появились микросхемы флэш-памяти с интерфейсом LPC, называемые хабами (firmware hub).

Энергонезависимая память с последовательными интерфейсами.

Для микросхем энергонезависимой памяти малого объема, от которых не требуется высокой производительности обмена данными, часто применяют последовательный интерфейс, применение которого позволяет упаковывать микросхемы памяти любого объема в корпус, имеющий всего 8 выводов. С таким интерфейсом выпускаются микросхемы EEPROM, FRAM и флэш-памяти.

Контрольные вопросы

1 Опишите особенность оперативной памяти.

2 Опишите особенность кэш-памяти.

3 Опишите особенность постоянной памяти.

4 Опишите особенность полупостоянной памяти.

5 Опишите особенность буферной памяти

6 Охарактеризуйте основные параметры памяти.

7 Опишите пакетный режим передачи данных.

8 Опишите особенности динамической памяти.

9 Для чего нужна регенерация памяти?

10 Опишите кратко асинхронную память.

Обратите внимание на лекцию "2.3. Особенности наращивания инженерной защиты".

11 Опишите кратко синхронную память.

12 Перечислите стандартные модули и их параметры динамической памяти.

13 Перечислите новые модули и их параметры динамической памяти.

14 Опишите особенность статической памяти.

15 Опишите кратко типы энергонезависимой памяти.

16 Опишите особенности разных типов флэш-памяти.