Основные типы больших интегральных схем

Лекция 1.

Введение. Основные типы больших интегральных схем для микропроцессорных комплектов.

Особая роль в совершенствовании систем автоматического управления в настоящее время принадлежит микроэлектронике и микропроцессорной технике, использование которых в САУ обеспечивает не только улучшение точностных характеристик, повышение отказоустойчивости, обеспечение стабильности функционирования, но и придает САУ принципиально новых свойств, таких, как гибкость и перестраиваемость структуры, адаптивность, способность решать вычислительные и логические задачи, самоконтроль и т.д.

Использование микропроцессоров в САУ требует решения целого ряда задач, специфика которых обусловлена как распределенным управлением в реальном масштабе времени, так и цифровым характером обрабатываемой информации. В связи с этим требуется подготовка специалистов обладающими знаниями и опытом по разработке и эксплуатации микропроцессорных систем различного назначения: информационных, связанных, вычислительных, управляющих и т.д.

Изучение такой интенсивно развивающейся и наукоемкой предметной области, как микроэлектроника, и микропроцессорная техника в частности - задача весьма интересная и сложная, требующая постоянного совершенствования и пополнения получаемых знаний и знакомства со смежными научно-техническими областями. Для эффективного решения прикладных задач любой современный специалист, профессионально связанный с вычислительной техникой, должен иметь адекватное представление о состоянии и перспективах развития ее элементной базы.

Создание фирмой Intel первого микропроцессора в 1971 году положило начало эпохе компьютеризации. "Благодаря микропроцессорам компьютеры стали массовым, общедоступным продуктом", - заявил Тед Хофф (Ted Поп), один из изобретателей первого микропроцессора. Его имя, вместе с именами его коллег - Федерико Феджина (Federico Faggin) и Стена Мейзора (Stan Mazor), внесено в список лауреатов Национального зала славы изобретателей США, а само изобретение признано одним из величайших достижений XX века.

За чуть более чем четверть вековую историю микропроцессоры прошли поистине гигантский путь. Первый чип Intel 4004 работал на частоте 750 КГц, содержал 2300 транзисторов и стоил около $200. Производительность его оценивалась в 60 тыс. операций в секунду. На сегодняшний день рекордные показатели принадлежат микропроцессорам Pentium 4 и составляют: 3,46 ГГц, 55 млн. транзисторов, и около $650 соответственно.

Такое интенсивное развитие технологий в обществе, где основным предметом труда становится информация, является следствием растущего спроса на новые орудия труда - компьютеры. На сегодняшний день компьютеризация является одним из главных направлений научно-технического прогресса и концентрированным его выражением. Количество и качество производимых в стране компьютеров, степень насыщенности вычислительной техникой самых разных отраслей становится одним из основных критериев ее экономического и военного потенциала.

В формируемом ежегодно в США группой экспертов перечне "критических технологий", охватывающем практически все направления производства, исследований и разработок, оказывающих влияние на военный и экономический статус страны, микроэлектронные технологии традиционно занимают первое место.

В микропроцессорах - наиболее сложных микроэлектронных устройствах - воплощены самые передовые достижения инженерной мысли. В условиях свойственной данной отрасли производства жесткой конкуренции и огромных капиталовложений, выпуск каждой новой модели микропроцессора - так или иначе связан с очередным научным, конструкторским, технологическим прорывом.

Современная элементная база - сверхбольшие интегральные схемы (СБИС), характеризуется большим числом транзисторов на кристалле и относительно малым числом выводов у корпуса. Поэтому БИС адекватны построению логически законченных устройств.

Рекомендуемые материалы

Различные выполняемые функции и сферы применения обусловили специализацию СБИС. Достаточно условно их можно разделить на следующие классы:

1) СБИС с аппаратной реализацией алгоритмов обработки данных:

микропроцессоры универсальные и сигнальные, а также микроконтроллеры, включая интерфейсные схемы для образования мультипроцессорных систем;

2) микросхемы памяти: статические и динамические;

3) программируемые логические интегральные схемы (ПЛИС).

Микропроцессоры и микроконтроллеры

Универсальные микропроцессоры предназначаются для применения в вычислительных системах: персональных ЭВМ, рабочих станциях, а в последнее время и в массово-параллельных супер-ЭВМ. Основной их характеристикой является наличие развитых устройств для эффективной реализации операций с плавающей точкой над 64 разрядными и более длинными операндами. Предназначаются в основном для проведения научно-технических расчетов.

Цифровые сигнальные процессоры рассчитаны на обработку в реальном времени цифровых потоков, образованных путем оцифровывания аналоговых сигналов. Это обусловливает их сравнительно малую разрядность и преимущественно целочисленную обработку. Однако современные сигнальные процессоры способны проводить вычисления с плавающей точкой над 32 — 40-разрядными операндами. Кроме того, появился класс медийных процессоров, представляющих собой законченные системы для обработки аудио- и видеоинформации.

Наибольшей специализацией и разнообразием функций обладают микроконтроллеры, используемые во встроенных системах управления, в том числе в бытовых приборах. Общее число типов кристаллов с различными системами команд превышает 500, и все они, в силу существования изделий с их использованием, имеют свою устойчивую долю рынка.

По прогнозам компаний-производителей дальнейшее развитие технологии производства микропроцессоров будет идти в направлении увеличения плотности транзисторов на кристалле, роста числа слоев металлизации и повышения тактовой частоты, наряду с уменьшением напряжения питания и удельной (на один транзистор) потребляемой электрической и выделяемой тепловой энергии.

Технологический предел линейных размеров транзисторов на кристалле, обусловленный физическими ограничениями, составляет около 0,05 мкм. На пути дальнейшей миниатюризации кроме физических ограничений имеются и экономические. Для каждого следующего поколения микросхем стоимость технологии удваивается ( в 1986 г. Intel 80386 имел 250 тыс. транзисторов и выпускался на заводе стоимостью 200 млн. долларов. Завод, производящий микросхемы по технологии 0,25 мкм, стоил 10 млрд. долларов ). Возрастают сроки изготовления микропроцессоров, так процессор Pentium производился за шесть месяцев, а более новый Pentium Pro - за девять. Во многом уже сейчас уровень технологии, используемой в массовом производстве, определяется экономическими соображениями. Увеличение числа слоев металлизации экспоненциально повышает процент брака при производстве, увеличение площади кристалла также приводит к снижению выхода годных кристаллов. Современный уровень технологии СБИС позволяет уверенно производить схемы с проектными нормами 0,13-0,09 мкм, 5-6 слоями металлизации, площадью кристалла менее 150 кв.мм и числом транзисторов порядка 55 млн. Смена поколений микропроцессоров происходит каждые 2 года. С каждым поколением линейные размеры элементов уменьшаются в 0,7 раза. В настоящее время ширина проводников составляет 0,13 мкм, а к 2004 г. достигнет 0,09 мкм. Тактовая частота будет составлять более 4 ГГц, что существенно усложнит проблему внутрикристальных, а еще более межкристальных соединений.

Основной технологической проблемой будет, по-видимому, отвод тепла от процессоров. Уже сейчас рассеиваемая мощность некоторых процессоров составляет до 70 Вт. И в дальнейшем, с увеличением тактовой частоты и числа транзисторов, ее рост будет продолжаться. Для снижения потребляемой энергии применяются разные технологические способы - уменьшение проектных норм и снижение питающего напряжения. Если мощность и впрямь будет расти, отвод тепла действительно станет непреодолимой преградой.

Микросхемы памяти

Как известно, производительность системы определяется скоростью работы наиболее «медленного» её компонента. Поэтому для достижения оптимального быстродействия необходимо использовать сбалансированные конфигурации. Это означает, что наиболее важные узлы микропроцессорного устройства, к которым относится процессор, набор системной логики и подсистема памяти, должны обладать приблизительно равной производительностью.

Упрощённо работу микропроцессорного устройства можно представить как последовательность операций, совершаемых над различными данными. Задача процессора заключается в выполнении этих операций, а подсистемы памяти – в доставке данных и сохранении результатов. Взаимодействие процессора и памяти управляется чипсетом либо осуществляется напрямую.

Естественно, что для создания быстрого микропроцессорного устройства необходимо прежде всего обеспечить высокую скорость выполнения операций. Но даже самый совершенный процессор, работая в связке с памятью обладающей недостаточной пропускной способностью, окажется бесполезен, т.к. попросту будет простаивать в ожидании очередных порций информации. Поэтому для современных приложений большое значение имеет пропускная способность памяти, объём и сколько задержки в выдаче данных при каждом обращении (латентность).

Любой подсистеме памяти соответствует набор характеристик, которые более-менее полно будут описывать её возможности. К ним, в первую очередь относится частота работы памяти (частота передачи данных) и разрядность шины. Эти два показателя определяют теоретическую пропускную способность шины памяти, которая равна произведению разрядности и частоты. В действительности теоретическая пропускная способность не достижима из-за присутствия латентности (в среднем 60-80%).

В спецификациях модулей часто указывается время доступа (численно оно равно обратной величине рабочей частоты) и представляет собой длительность одного такта. Т.о., чем меньше время доступа, тем на большей частоте сможет работать модуль памяти.

В настоящее время в микропроцессорных устройствах широко применяется многоуровневая иерархическая архитектура памяти, где на верхнем уровне иерархии расположена более быстродействующая кэш-память, в которую в процессе вычислений помещаются интенсивно используемые фрагменты программного кода и обрабатываемых данных. В реальных системах используется до 3 уровней кэш-памяти. Разработчики используют более быстродействующую и, соответственно, более дорогую память в наиболее "ответственных" узлах системы.

Оперативная память (энергозависимая, т.е. теряющая запомненную информацию при снятии питания) случайного доступа RAM развивается уже довольно долгое время, и к настоящему моменту сформировались две основные её разновидности – статическая (SRAM) и динамическая (DRAM). Их отличие заключается в способе хранения данных. Динамическая память (память использует для запоминания бита информации состояния конденсатора "заряжен - не заряжен") требует постоянного обновления записанной информации с периодом порядка десятков мсек, что сказывается на увеличении латентности. При этом она проста и дёшева в производстве. Статическая память, наоборот, достаточна дорога за счёт более сложного устройства ячеек (статические микросхемы памяти запоминают биты данных в триггерах, что требует 4-6 транзисторов для хранения бита), но обладает очень низкой латентностью. Тем не менее именно стоимость во многом определяет популярность продукции. Поэтому SRAM не получила большого распространения в модулях ОЗУ, зато активно применяется в процессорах в качестве кеша 2-го уровня.

В одной из первых разновидностей DRAM под названием EDO RAM применялся асинхронный режим доступа (процессор при считывании данных приостанавливает свою работу), что приводило к существенной потере производительности системы. Но несколько лет назад рынок стал заполняться новым типом DRAM – SDRAM с синхронным режимом работы.

Память SDRAM представляет собой набор элементарных ячеек, в каждой из которых может быть записан 1 бит информации. Они объединяются в матрицы, по номерам строк и столбцов которых производится адресация. Физически каждая ячейка DRAM состоит из конденсатора и транзистора. И в этом кроется основной недостаток DRAM. Дело в том, что конденсатор не может самостоятельно поддерживать электрический заряд, поэтому для функционирования ячейку необходимо периодически подзаряжать. Эта процедура должна повторяться и после каждой операции чтения, что в определенных случаях существенно увеличивает латентность.

Поиск ячейки в матрице осуществляется с помощью двух сигналов – RAS и CAS. Первый несёт информацию о номере строки, второй – о номере столбца.

Операцию считывания данных из ячейки можно разбить на несколько элементарных стадий:

пересылка запроса процессора набору системной логики (1 такт системной шины);

перенаправление запроса на банк памяти, соответствующий запрашиваемому адресу (1 цикл работы ОЗУ);

поиск необходимой строки в матрице (2-3 цикла) – “RAS-to-CAS delay” или “RAS-to-CAS latency”;

поиск необходимого столбца в найденной строке, т.е. ячейке, располагающейся на их пересечении (2-3 цикла) – CAS-латентность;

непосредственно считывание и помещение информации в выходной буфер (1 цикл);

передача считанной информации набору системной логики (1 цикл);

перенаправление её процессору (1 такт системной шины).

Т.о., простая на первый взгляд операция растягивается на 9-11 тактов системной шины и соответственно 45—55 тактов процессора при множителе 5. Но столь большая задержка имеет место лишь при считывании первых 8 байтов. Тогда как другие ячейки из той же строки будут доступны уже по истечении лишь времени CAS-латентности. Если же происходит последовательное чтение ячеек, то задержки будут отсутствовать вовсе. С другой стороны, возможен вариант, когда первая и вторая считываемые ячейки располагаются в одном банке, но на разных строках. В этом случае к выше перечисленным задержкам добавится ещё одна – “Precharge delay”, необходимая на подзарядку первой ячейки после операции считывания (2-3 цикла).

Три выше упомянутых параметра - CAS-латентность, RAS-to-CAS-латентность и “Precharge delay” – образуют набор таймингов модуля памяти.

Общая латентность системы складывается не только из задержек выдачи данных ОЗУ, но и времени их пересылки процессору.

Наименьшие потери при пересылке данных будут иметь место при синхронном обмене информацией, т.е. когда частоты системной шины и шины памяти совпадают. При использовании асинхронного режима появляется дополнительная латентность, вызванная необходимостью согласования двух шин.

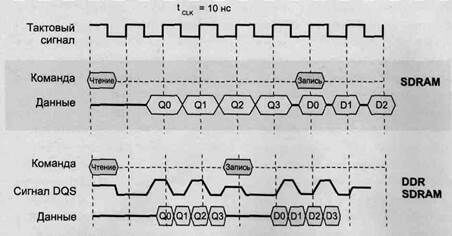

DDR SDRAM является эволюционным шагом в развитии обычной памяти SDRAM. Основное отличие между ними заключается в способе передачи данных. В DDR SDRAM используется так называемая DDR (Double Data Rate) технология, при которой для кодирования информации используются как передний, так и задний фронт тактового импульса. В результате при той же частоте FSB эффективная частота шины памяти удваивается. При этом на удвоенной частоте передаются только данные, а пересылка адресов осуществляется на основной частоте. В остальном модули SDRAM и DDR SDRAM мало отличаются друг от друга.

Подобная схема передачи данных весьма чувствительна даже к самой незначительной задержке тактового сигнала, поэтому, в отличие от SDRAM, для синхронизации передачи данных помимо сигнала тактового генератора применяется дополнительный сигнал DQS. Этот сигнал передается параллельно с тактовым сигналом и корректирует процесс передачи данных для каждой линии шины данных. Для выдачи сигнала DQS, означающего доступность данных на выходе, используется специальный цикл с фиксированной задержкой DLL (Delay Locked Loop).

Для точной синхронизации сигналов DQS и передачи данных (DQ) соответствующие проводники имеют одинаковую длину и емкость. Таким образом, колебания напряжения и температуры одинаково отражаются на обоих сигналах, что обеспечивает отсутствие нарушения синхронизации между контроллером памяти и микросхемами модулей памяти. Дополнительный контроль синхронизации передачи данных обеспечивает более надежную и высокую скорость передачи данных, чем при использовании только сигнала тактового генератора. Чтение и запись данных производится не в соответствии с тактовым сигналом, а синхронизируется сигнал DQS (рис. 1).

Рис. 1. Временная диаграмма DDR SDRAM

Архитектура микросхемы состоит из четырех независимых банков (рис. 2).

При тактовой частоте 100 и 133 МГц пропускная способность шины памяти DDR SDRAM составляет соответственно 1,6 и 2,1 Гбайт/с.

В настоящее время тактовая частота шины памяти с поддержкой DDR SDRAM составляет 100, 133, 166, 200 МГц, соответствующие микросхемы памяти называются соответственно DDR200, DDR266, DDR333 и DDR400, а модули памяти РС1600, РС2100, PC2700 и PC3200 (в названии модулей указана фактическая пропускная способности шины памяти в Гб/сек).

Дальнейшим развитием технологии DDR SDRAM является технология DDR II. Появление этого типа памяти ожидается в 2003 году. В отличие от DDR SDRAM в DDR П за один такт по каждой линии будет перерваться не 2, а 4 бита информации (при 64-разрядной шине — 32 байта), что вдвое увеличит пропускную способность шины памяти. Естественно, данный подход требует более совершенной системы синхронизации. Рабочие напряжения DDR П уменьшены с 2,5 до 1,8 В. Микросхемы выполнены в корпусе микро-BGA.

Первоначально модули DDR-II будут работать на эффективных частотах 400, 533 и 667 Мгц, что позволит говорить о теоретической пропускной способности 3,2, 4,2 и 5,3 Гб/сек.

Для уменьшения времени доступа к данным планируется использовать технологию Virtual Channel (разработанную компанией NEC), а также кэширование информации.

Рис. 2. Структурная схема DDR SDRAM

Следующий большой шаг в развитии DDR SDRAM должен будет произойти лишь 2007 году, когда планируется появление памяти следующего стандарта DDR-III. По предварительным данным, стартовая эффективная частота модулей составит 800 Мгц, которая впоследствии вырастет до 1,5 Ггц. Планируется дальнейшее понижение напряжения питания до 1,2 В. Будут приняты специальные меры по борьбе с возникающими на высоких частотах помехами.

В ближайшее время может появиться ещё один тип ОЗУ – QBM SDRAM. QBM (Quad Band Memory) фактически представляет собой слегка усовершенствованную память DDR, но с увеличенной вдвое теоретической пропускной способностью. При производстве модулей QBM используются те же самые чипы DDR SDRAM. Однако циклы работы половины из них смещены на четверть такта. В результате ширина шины как бы увеличивается до 128 бит, а модуль как бы превращается в двухканальный (для PC2100 пропускная способность составит 4,2 Гб/сек).

Повышение пропускной способности шины памяти может осуществляться либо за счёт увеличения тактовой частоты шины, либо её разрядности. К сожалению, внутреннее устройство SDRAM не позволяет существенно продвинуться в этой области. Дело в том, что каждая разрядная линия шины памяти при распространении по ней переменного сигнала неизбежно излучает электромагнитные волны. Чем выше частота сигнала и плотность расположения линий, тем сильнее влияние излучаемых помех на сигнал. Поэтому у памяти SDRAM существует предел пропускной способности. Чтобы как можно ближе к нему подобраться, можно увеличивать частоту шины при неизменном количестве разрядов. Но есть и альтернативное решение – заметно сократить количество линий в шине, что позволит существенно увеличить частоты. Именно эта идея и была реализована в памяти Rambus DRAM.

Разрядность шины большинства модулей RDRAM составляет 16 бит, а рабочая частота 400 МГц. К тому же в памяти RDRAM используется DDR-технология. Поэтому эффективная частота шины равняется 800 Мгц. Модули RDRAM должны устанавливаться парами, т.к. предназначены для работы в двухканальной конфигурации. Т.о., суммарная теоретическая пропускная способность – 3,2 Гб/сек.

Несмотря на принципиально иной подход к организации памяти, ячейки RDRAM не отличаются от ячеек SDRAM – это та же совокупность транзистора и конденсатора. Тем не менее для реализации RDRAM потребовалось перестроить инфраструктуру модулей. Если у SDRAM один банк состоит из 8 чипов, то у RDRAM, наоборот, каждый чип является независимым и сам может состоять из нескольких десятков банков. В результате такого «распараллеливания» RDRAM способна производить гораздо больше, чем SDRAM, операций чтения за один и тот же промежуток времени. Причём латентность при считывании окажется незначительной как раз из-за того, что многие банки памяти могут постоянно держаться открытыми. С помощью подобных технических решений достигается высокая эффективность использования шины памяти – более 90%.

Обратная сторона медали заключается в усложнении модулей. В отличии от SDRAM чипы RDRAM необходимо оснащать управляющей логикой, что увеличивает их площадь, а высокая частота функционирования приводит к значительному тепловыделению. Более того, сложность в проектировании и производстве определила высокую конечную стоимость, что и сказалось в итоге на отсутствии популярности данного типа памяти среди массового потребителя.

Но у RDRAM есть ещё один серьёзный недостаток – высокая латентность при выдаче первых байтов информации, которая может в 2-3 раза превышать соответствующую латентность памяти SDRAM. В результате RDRAM показывает рекордную пропускную способность при считывании потоковых данных, располагающихся друг за другом. Но в задачах с хаотическим характером обращения к памяти эффективность использования шины памяти резко снижается.

Вся подсистема памяти Rambus состоит их следующих компонентов (рис. 3):

• контроллера памяти (RMC — Rambus Memory Controller);

• Rambus-канала (RC — Rambus Channel);

• генератора тактовых импульсов (DRCG — Direct Rambus Clock Generator);

• микросхемы памяти RDRAM (Rambus DRAM), которая установлена на модулях памяти RIMM (Rambus In-line Memory Module).

Рис.3 Подсистема памяти RambusDRAM.

Rambus-канал

Rambus-канал (рис. 4) предназначен для осуществления электрической связи между контроллером памяти и микросхемами RDRAM. Физически он представляет собой шину, которая состоит из 30 проводников, разведенных строго параллельно на материнской плате.

Рис.4 Схема Rambus-канала

Сигналы в Rambus-канале передаются в соответствии с высокоскоростным протоколом сигналов RSL (Rambus Signal Levels). Согласно данному протоколу осуществляется низковольтовый перенос номинальных напряжений логического «0» и логической «1» с разностью 800 мВ (рис. 5).

Рис.5

Генератор тактовых импульсов

Rambus-канал является синхронным. Команды и данные передаются параллельно по переднему и заднему фронту синхроимпульсов, создаваемых генератором тактовых импульсов (рис.6).

Рис.6 Схема генератора тактовых импульсов

Конструктивно генератор тактовых импульсов может быть интегрирован в контроллер памяти или установлен в виде отдельной микросхемы (в 24-контактном корпусе типа SSOP).

Передача данных

Данные и служебные биты передаются по каждому фронту тактового сигнала с частотой 800 МГц (1,25 нс), что соответствует скорости передачи 800 Мбит/с на линию. Таким образом, пропускная способность шины составляет 1,6 Гбайт/с. Передача данных осуществляется только между контроллером и микросхемами памяти, обмен только между микросхемами невозможен.

Вся информация передается по Rambus-каналу пакетами (пакеты строк, столбцов и данных). Каждый пакет передается за четы ре такта (10 нс).

Конвейеризация

Операция чтения/записи в Rambus-канале могут быть конвейеризированы. В этом случае время задержки первого пакета составляет 50 нс, далее операции чтения/записи осуществляются практически непрерывно.

При последовательном чередовании двух операций записи и двух операций чтения, адресованных к одной микросхеме, пропускная способность канала составляет 86% от предельной, а при адресации к разным микросхемам — 95%.

Контроллер памяти

Контроллер памяти Rambus осуществляет управление системой памяти RDRAM и основные функции мультиплексирования/демультиплексирования при преобразовании данных, передающихся по 16-разрядной последовательной шине Rambus-канала в 64-разрядную системную шину. Контроллер принадлежит к семейству специализированных интегрированных микросхем ASIC (Application Specific Integrated Circuits). Данные микросхемы способны объединить в себе функции, обычно реализуемые целым набором микросхем, но при этом оказываются существенно быстрее, компактнее и дешевле.

Основным элементом контроллера памяти Rambus (RMC — Rambus Memory Controller) является специализированная микросхема библиотеки макроядра (RAC — Rambus ASIC Cell). Здесь происходит преобразование высокоскоростных сигналов RSL канала Rambus в низкоскоростные сигналы CMOS-уровня.

Контроллер памяти осуществляет взаимодействие подсистемы памяти Rambus с другими компонентами персонального компьютера, взаимодействующими с памятью (центральным процессором, жестким диском, видеосистемой и др.).

Структурная схема микросхемы RDRAM представлена на рис. 7.

Рекомендуем посмотреть лекцию "Иностранный капитал на информационном рынке".

Внутреннее ядро RDRAM имеет 128/144-разрядную шину, работающую на частоте 100 МГц - 1/8 тактовой частоты Rambus-канала. Таким образом, каждые 10 нс в ядро (или из ядра) может быть передано 16 байт данных.

Компания Rambus планирует эволюционное развитие существующей линейки модулей RDRAM. В 2003-2004 годах ожидается выпуск как 32-, так и 64-битных чипов, работающих на эффективных частотах 1,2 и 1,33 Ггц (10,6 Гб/сек).

Параллельно Rambus представила новый сигнальный интерфейс памяти Yellowstone. Для реализации данного интерфейса планируется использовать три разработки: дифференциальный протокол передачи запросов, технологию ODR (Octal Data Rate), позволяющую за один такт передавать 8 бит данных, и технологию упрощающую привязку данных к тактовой частоте. По заявлению компании Rambus, технология Yellowstone позволит достичь тактовых частот 6,4 Ггц и пропускной способности до 100 Гб/сек.

Рис.7 Структурная схема RDRAM