Цифровые интегральные микросхемы

6. Цифровые интегральные микросхемы

6.1. Общие понятия

Анализ и синтез цифровых схем проводят на основе Булевой алгебры. Джон Буль - английский математик XIX века.

Цифровые схемы оперируют с логическими переменными, которые обозначаются буквами латинского алфавита. Над логическими переменными можно совершать 3 основных действия:

операция ИЛИ;

операция И;

операция НЕ.

ИЛИ - логическое сложение (дизъюнкция).

Рекомендуемые материалы

И - логическое умножение (конъюнкция).

НЕ - инверсия, отрицание.

Обозначение этих действий:

ИЛИ обозначается +,(V);

И обозначается ´,(/);

НЕ обозначается чертой над логической переменной.

6.2. Основные свойства логических функций

Переменная, связанная логическими операциями, образует логическую функцию. Свойства логических функций:

1. Свойства логического сложения.

0+0=0;

0+1=1;

1+1=1.

2. Свойства логического умножения.

0´0=0;

0´1=0;

1´1=1.

3. Свойства отрицания.

Приведенные соотношения называются аксиомами.

Основные свойства в общем виде:

а+0=а; а´0=0;

а+1=1; а´1=а;

а+а=а; а´а=а;

6.3. Основные логические законы

1. Переместительный закон

a+b=b+a;

a×b=b×a.

2. Сочетательный закон

(a+b)+c=a+(b+c);

(a×b)×c=a×(b×c).

3. Распределительный закон

a×(b+c)=a×b+a×c;

a+(b×c)=(a+b)×(a+c).

Доказательство: a+bc=a(1+b+c)+bc=a+ab+ac+bc=a(a+c)+b(a+c)=(a+c)×(a+b).

4. Закон поглощения

a+ab=a(1+b)=a;

a×(a+b)=a+ab=a.

5. Закон склеивания

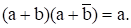

6. Закон отрицания (законы Моргана)

Законы Моргана позволяют реализовать функционально полные системы на элементах И-НЕ, ИЛИ-НЕ.

6.4. Функционально полная система логических элементов

Функционально полная система - это такой набор элементов, используя который можно реализовать любую сколь угодно сложную логическую функцию.

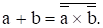

Набор из основных логических элементов И, ИЛИ, НЕ является естественно функционально полным. Функционально полные системы могут быть реализованы также на элементах И-НЕ, ИЛИ-НЕ. Реализация основных логических функций на элементах И-НЕ доказывается следующими соотношениями:

Для И:

Для ИЛИ:

Для НЕ:

6.5. Обозначения, типы логических микросхем и структура ТТЛ

Обозначения основных логических микросхем показано на рис. 105. В корпусе микросхемы содержится несколько логических элементов. Типы логических микросхем:

1. ТТЛ - транзисторно-транзисторная логика.

Выпускаются серии: К133, К155, К555, К1531, К1533.

2. КМОП - микросхемы на основе комплементарных полевых транзисторов по структуре металл-окисел-полупроводник: К176, К561, К1561.

3. ЭСЛ - эмиттерно-связанная логика: К500.

Структура ТТЛ логического элемента 2И-НЕ представлена на схеме рис.106. На входе схемы используется многоэмиттерный транзистор VT1, который имеет 2 эмиттера для организации двух входов. VT2,VT3 образуют усилительные каскады.

Рассмотрим работу схемы. При нулевом сигнале на вх1 протекает ток через R1,Б-Э VT1, ключ Кл на общую точку ОТ. VT1 работает в ключевом режиме, на эмиттер подан ноль, напряжение на базе составляет примерно 0,6в. Тогда через переход Б-К транзистора VT1 и базовые переходы транзисторов VT2, VT3 ток протекать не может, т.к. эта цепь закорочена переходом Б-Э VT1. Значит, ток через Б-Э VT2 и Б-Э VT3 отсутствует, транзисторVT3 закрыт, напряжение питания приложено к выводам К-Э VT3, следовательно, напряжение на выходе схемы соответствует 1. Логический элемент по одному из входов реализует логическую функцию НЕ (0 на входе, 1 на выходе).

При 1 на вх1 ток по входной цепи протекать не может. Закоротка Б-К VT1 отсутствует. Ток протекает по цепи +5В, R1, Б-К VT1, Б-Э VT2, Б-Э VT3.Транзистор VT3 открыт. Он закорачивает выход с ОТ, что соответствует 0 на выходе.

Для реализации функции ИЛИ-НЕ в рассматриваемой структуре используют параллельное включение транзисторов. На рис.107 приведена схема элемента 2ИЛИ-НЕ. В этой схеме параллельно включены транзисторы VT2 и VT2'. Работу схемы поясняет таблица.

Основные функции И, ИЛИ, НЕ могут быть изображены в виде схем из контактов реле. Катушки реле являются входами таких схем. Элементу И соответствует последовательное соединение контактов - рис.108. Элементу ИЛИ соответствует параллельное соединение контактов - рис.109. Работа схем поясняется приведенными таблицами. Сигнал 0 на входе соответсвует разомкнутому состоянию контакта, 1 –замкнутому. Столбец значений выходного сигнала записывается на основе аксиом.

Основные параметры логических ТТЛ элементов

1. Напряжение питания Uпит=+5В±(5¸10)%.

2. Быстродействие.

Характеризуется временем переключения(изменение состояния на противоположное), составляет 5...50 нс.

3. Помехоустойчивость (по входу).

Определяется тем уровнем помех на полезном сигнале, который не приводит к ложному изменению состояния элемента. У большинства ТТЛ -элементов порогом срабатывания их является напряжение Uпор=1,4В, т.е. напряжение от 0 до 1,4В воспринимается как 0, а 1,4В и больше воспринимается как 1.

4. Потребляемая мощность.

5. Нагрузочная способность (по выходу).

Составляет несколько миллиампер.

6. Выходные параметры ТТЛ:

Логической 1 соответствует Uвых>2,4В, логическому 0 соответствует Uвых<0,4В.

6.6. Синтез комбинационных логических схем

Комбинационные схемы - это схемы, которые не содержат элементов

памяти и элементов выдержки времени.

Последовательность синтеза следующая:

1. Задаётся словесный алгоритм работы схемы.

2. Составляется таблицы истинности.

3. Записывается исходная логическая функция и выполняется её минимиза-ция.

4. Выполняется реализация полученной логической функции на логических элементах.

Пример: требуется построить логическую схему голосования на 3 вхо-

да: cигнал на выходе схемы равен 1, когда большинство входных сигналов равно 1.

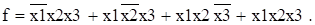

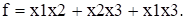

Составляем таблицу истинности: таблица истинности - это табличная запись алгоритма. Обозначим входные переменные: x1,x2,x3. В таблице истинности для входных переменных должны быть записаны все возможные комбинации. Число строк в такой таблице равно 2 в степени n, где n -количество входных переменных. Выходная логическая функция ¦ записывается по словесному алгоритму (рис.110). Когда две или три входных переменных равны 1, выходная функция тоже равна 1.

По таблице истинности может быть записано логическое выражение. Форма записи по таблице истинности называется совершенно нормальной формой. Существует две формы записи: дизъюнктивная совершенно нормальная форма - сокращенно ДСНФ, конъюнктивная совершенно нормальная форма - КСНФ. Обычно запись ведётся в дизъюнктивной форме. В этой форме записи принимаются во внимание строки, в которых логическая функция принимает значение 1. Произведения переменных этих строк складываются логически. ДСНФ для нашего примера:

Можно принимать во внимание строки с нулевым значением функции, только при этом каждая строка - это сумма переменных строки, а между собой суммы переменных соединяются произведением. Функция называется КСНФ.

Дальше выполняется следующий этап синтеза - минимизация, т.к. реализация логической функции по ДСНФ является достаточно сложной ввиду большого размера выражения для f. Цель минимизации - упростить выражение до такого вида, которое далее бы не упрощалось. В результате получается, так называемая, тупиковая форма.

6.6.1. Методы минимизации логических функций

Минимизация может быть выполнена несколькими способами.

1. На основе законов алгебры логики.

Недостаток метода - сложно выбрать из законов подходящий закон для очередного упрощения, трудно наметить путь преобразования, нельзя гарантировать, что полученная упрощенная форма является тупиковой.

2. Метод карт Карно.

Применяется при числе переменных n<5...6.

3. Метод Квайна и его модификации. Является табличным, не имеет ограничений по количеству переменных. Сложный, но хорошо поддаётся

алгоритмизации и исполнению на ЦВМ.

Минимизация с помощью карт Карно

Карта Карно представляет собой прямоугольную таблицу, в которой число клеток равно 2 в степени n. Карта заполняется на основе таблицы истинности или записи логической функции в ДСНФ.

Для приведенного выше примера таблица истинности имеет вид, представленный на рис. 111. Внутри карты Карно записываются значения

логической функции. Значения входных переменных записываются по краям карты. Каждая входная переменная делит поле карты пополам. Для одной половинки поля значения входных переменных равны 1, для другой - 0. При расстановке переменных необходимо соблюдать следующее правило:

соседние столбцы и строки должны различаться только одной переменной. Значение входной переменной, равное 1, принято охватывать скобочкой.

Там, где нет скобочки, значение переменной равно 0. Возможно другое обозначение переменной по краю Карты (рис. 112).

Далее единицы в карте Карно объединяются контурами. Правила нанесения контуров:

1. Каждый контур должен быть прямоугольным.

2. Количество клеток внутри контура должно быть равным 2 в степени k,

где k=1,2,3,...,n.

3. Одни и те же клетки с единицами могут входить в несколько контуров.

4. Размеры контуров должны быть как можно большими, а число контуров

как можно меньшим.

5. Нижняя и верхняя строки, левый и правый столбцы считаются соседними.

Запись минимизированного выражения по карте Карно с нанесенными контурами выполняется по следующим правилам:

1. Количество слагаемых в дизъюнктивной форме равно количеству контуров.

2. Из конъюнкции переменных исчезают те переменные, границы изменения которых пересекаются контуром.

Для рассматриваемого примера:

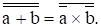

В этом выражении x1x2 записано из первого контура, x2x3 - из второго контура, x1x3 - из третьего контура.

Реализация по этому выражению имеет вид, представленный на рис.

113. Реализация требует два корпуса микросхем.

Для уменьшения количества корпусов преобразуют полученную логическую функцию по законам Моргана и записывают её в базисе И-НЕ или в базисе ИЛИ-НЕ. Применение законов Моргана позволяет избавиться от “+” в логической функции или от произведений. Один из законов Моргана имеет вид:

Изменим запись закона

Запись справедлива для любого количества элементов. Под a и b можно понимать логические выражения. Применим формулу для нашего выражения:

Реализация по данному выражению показана на рис. 114. Реализация требует два корпуса микросхем.

6.6.2. Примеры минимизации, записи функции и реализации

Пример 1 (рис. 115).

Свойство 5 в Правилах нанесения контуров можно понимать так, что края карты не являются границами. Говорят, что карта Карно представляет собой “бублик”. Она может быть соединена по левому и правому краю, образуя цилиндр, а затем по верхнему и нижнему краю, образуя ”бублик”. Для

нашего примера

f = x3.

f = x3.

Реализация представлена на рис.115.

Пример 2 (рис.116).

Логическая функция имеет вид:

|

f=x1 + x2 = x1x2.

Реализация – рис.117. Реализация после применения закона Моргана – рис.118.

Пример 3. Рассмотрим типовую функцию, которая называется “Сумматор по модулю 2” или “Исключающее ИЛИ”. Таблица истинности

для неё имеет вид (для двух входов), представленный на рис.119. Обозначе-

ние функции “Исключающее ИЛИ”:

f=x1 Å x2.

Карта Карно для этой функции показана на рис.120.Она показывает, что

нельзя организовать контур с несколькими единицами, т.е. минимизация

единицами, т.е. минимизация

невозможна и логическую функцию можно записать только в ДСНФ

.

.

Обращаем внимание, что  . Реализация представлена на рис. 121. Требуется 2 корпуса.

. Реализация представлена на рис. 121. Требуется 2 корпуса.

Пример 4. Вид карты Карно для четырёх входных переменных показан на рис.122.

6. 7. Интегральные триггеры

В отличие от комбинационных логических схем, триггеры - это последовательностные схемы, т.е. устройства с памятью. Их выходные сигналы зависят не только от сигналов на входах в данный момент времени, но и от ранее воздействовавших сигналов.

Типы триггеров в зависимости от способов управления:

1. Асинхронные или не тактируемые.

2. Синхронные или тактируемые.

Изменение состояние асинхронного триггера происходит сразу же после изменения сигналов на его управляющих входах.

У синхронного триггера изменение состояния под действием управляющих сигналов возможно только при присутствии сигнала на специальном тактовом входе. Тактирование может осуществляться импульсом (т.е. потенциалом) или фронтом импульса (т.е. перепадом потенциала). Поэтому различают триггеры со статическим и динамическим управлением. Существуют также универсальные триггеры, которые могут работать как в тактируемом, так и в не тактируемом режиме. Чаще всего применяются синхронные триггеры, которые обладают большой помехоустойчивостью.

Типы триггеров в зависимости от функционального назначения:

1) RS - триггеры; 2) D - триггеры; 3) JK - триггеры; 4) T - триггеры.

На основе триггеров строятся счетчики, регистры, элементы памяти, которые составляют основу ЦВМ.

6.7.1. RS асинхронный триггер

Реализация на элементах 2И-НЕ имеет вид, представленный на рис.123. На нем обозначено: S - Set - установка, R - Reset - cброс. Черточки над S и R означают инверсию, т.е. управление триггерами ведется нулевыми сигналами. При подаче 0 на инверсный вход S на выходе Q устанавливается 1. При подаче 0 на инверсный вход R на выходе Q устанавливается 0. Одновременная подача нулевых сигналов на оба входа запрещена. Наличие 1 на обоих входах - это состояние хранения предыдущей информации (память). Отличительная схемотехническая особенность триггера - это наличие обратной связи с каждого выхода на вход. На основе корпуса с элементами 2И-НЕ можно реализовать 2 триггера. Функционирование RS триггера можно записать на основе таблицы истинности (рис. 124). Состояние выходов триггера определяют нулевые сигналы на входах. Форма сигналов на управляющих входах, представлена на рис. 125. При подаче питания такой триггер встает в одно из возможных состояние Q=1 или Q=0. Заранее это определить нельзя.

Реализация RS триггера на элементах 2ИЛИ-НЕ показана на рис. 126. Состояние его выходов определяют 1 на входах, т.к. черточек над R и S нет. Это означает, что управление ведется 1. Таблица истинности представлена на рис. 127.

6.7.2. Асинхронный D - триггер

Буква D в названии триггера - это начальная буква слова Delay-задержка. Основой D -триггера является RS триггер, у которого выполняется условие несовпадения управляющих сигналов, а управляющий вход у триггера один (рис.128). Диаграммы работы представлены на рис.129.

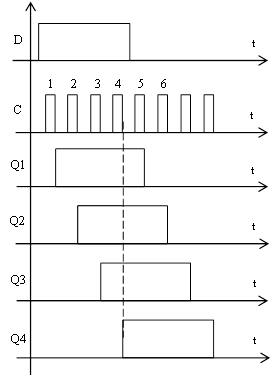

6.7.3. Синхронный D - триггер со статическим управлением

Схема такого триггера (рис.130) имеет вход D -информационный вход и вход C -вход синхронизации. Логические элементы 2И-НЕ на входе при подаче на вход C единичного сигнала разрешает пройти на выход триггера сигналу с входа D. При подаче на вход С нулевого сигнала -на выходе логических элементов появляется единица, информация на выход со входа D не проходит и триггер хранит предыдущую информацию. На вход С всегда подаются импульсы постоянной частоты. Частота обычно выбирается достаточно высокой по сравнению с частотой изменения сигнала на входе D. Обозначение триггера на схемах показано на рис. 131. Диаграммы работы приведены на рис. 132. В серии 155 выпускается 2 типа D -триггеров со статическим управлением: К155ТМ7, К155ТМ5.

6.7.4. Синхронный D - триггер с динамическим управлением

Триггеры с динамическим управлением обычно строятся по структуре двухступенчатого триггера, содержащего ведущий и ведомый триггеры. Это так называемая структура MS (ведущий-ведомый).

Обозначение на схемах показано на рис. 133. R и S -это установочные входы, используются при включении триггера для предварительной установки в нужное состояние. Выпускается триггер K155TM2. Значок > на входе C говорит о том, что синхронизация триггера осуществляется по фронту импульса синхронизации, подаваемого на вход C. Если применяется значок < , то синхронизация осуществляется по спаду импульса синхронизации. Диаграммы работы триггера приведены на рис.134.

6.7.5. Синхронный JK - триггер

Буква J обозначает слово Jump-прыжок, K - Keep-держать. Выпускается триггер К155ТВ1, он является универсальным.

Обозначение на схемах показано на рис.135. Значок < на входе C говорит о том, что синхронизация триггера осуществляется по спаду импульса синхронизации, т.е. при С=1®0: Q -var.

Возможные режимы работы:

1. J=1, K=0. Это режим записи Q=1 по спаду сигнала синхронизации С=1®0.

2. J=0, K=1. Это режим записи Q=0 по спаду сигнала синхронизации С=1®0.

3. J=1, K=1. При этом Q=var по спаду сигнала С=1®0. Это счетный режим работы.

4. J=0, K=0 или С=0=const. При этом Q=const. Это режим хранения информации.

JK-триггер может быть преобразован в D-триггер, как показано на рис. 135б.

6.7.6. T - триггер

Это счетный триггер. Обозначение на схемах показано на рис.136, диаграммы работы - на рис.137. Т - тактовый вход. С приходом тактового импульса Т- триггер изменяет свое состояние на противоположное.

На рис. 138 показано преобразование JK - триггера в T- триггер, а на рис 139 - преобразование D - триггера в Т- триггер.

6.7.7. Вспомогательные схемы для триггеров

Схема генератора импульсов

Схема представлена на рис.140. Она используется для получения импульсов, подаваемых на вход С или Т синхронных триггеров. Основой схемы является RS - триггер, у которого одна обратная связь с выхода на вход заменена конденсаторной обратной связью. Величина сопротивления резисторов R»300 Ом. Резисторы R обеспечивают лучшую возбуждаемость генератора и стабильность работы. Триггер имеет управляющий вход. В режиме генерации на вход управления должна быть подана 1, при 0 - генерация запрещена.

Форма выходных импульсов и диаграммы напряжений в различных точках схемы приведены на рис. 141. Период работы T=t1+t2=f(C).

Формирователь импульса

Формирует импульсы заданной ширины. Схема приведена на рис.142, диаграммы работы - на рис.143. Инверторы на входе и выходе схемы придают ей универсальность - в качестве входа можно использовать Вх.1 или Вх.2, а в качестве выхода -Вых.1 или Вых.2 или Вых.3.

6.8. Мультиплексоры и демультиплексоры

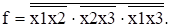

Мультиплексор (MS) (другие названия – селектор данных, коммутатор) – это комбинационное логическое устройство, предназначенное для управляемой передачи данных, которые поступают по нескольким входам, на один выход. Выбор того или иного входа осуществляется в соответствии с поступающим кодом адреса. Согласно определению, мультиплексор имеет две группы входов (информационные и адресные) и один выход. Код, подаваемый на адресные входы, определяет, какой из информационных входов в данный момент подключен к выходному выводу. Если число адресных входов равно n, то число информационных входов может быть равно 2n .

На рис. 144a приведена схема мультиплексора К561КП2. Это восьмивходовой мультиплексор-демультиплексор. Микросхема имеет три адресных входа 1, 2 и 4, восемь информационных входов Х0-Х7 и вход стробирования S, с помощью которого выход мультиплексора отключается от входов и переходит, в так называемое, третье состояние (верхний и нижний ключи выходного каскада микросхемы находятся в закрытом состоянии). Для получения третьего состояния на вход S необходимо подать лог.1. При подаче на адресные входы 1, 2 и 4 двоичного кода адреса, а на вход S лог. 0 выход мультиплексора соединяется с входом, номер которого равен двоичному коду адреса. В этой микросхеме соединение входов с выходом организуется с помощью двунаправленного ключа на КМОП-транзисторах. Передаваемый через мультиплексор сигнал может быть как аналоговым, так и цифровым, он может передаваться как с входов на выход (режим мультиплексора), так и с выхода распределяться по входам (режим демультиплексора).

Мультиплексор может применяться для опроса различных датчиков цифровых и аналоговых сигналов и передачи этой информации на вход одного приемника (для усиления, преобразования, индикации).

Демультиплексор (DMS) – это комбинационное логическое устройство, предназначенное для управляемой передачи данных от одного источника информации в несколько информационных каналов. Согласно определению, демультиплексор в общем случае имеет один информационный вход, n адресных входов и 2n выходов. Демультиплексор может применяться для распределения сигнала, принятого по одному проводу, к различным потребителям (рис. 144б).

|

Рис.144а Рис.144б Рис.145

6.9. Дешифраторы

Дешифратор или декодер (DC) – это комбинационное логическое устройство, предназначенное для преобразования входного кода в другой код. В качестве примера рассмотрим дешифратор К561ИД1 (рис. 145). Он преобразует входной код в так называемый унитарный: выходной сигнал с уровнем лог.1 появляется на том выходе дешифратора, номер которого соответствует десятичному эквиваленту входного кода, а на остальных выходах дешифратора при этом лог.0.

Широко распространены также дешифраторы двоично-десятичного кода в код семисегментного индикатора.

В заключение отметим, что мультиплексоры и дешифраторы относятся к классу комбинационных логических устройств. Далее рассматриваются устройства на основе последовательностных логических устройств (триггеров).

6.10. Двоичные счетчики-делители

Счетчик (CT) – это последовательностное устройство, предназначенное для подсчета числа входных импульсов и хранения результатов счета в двоичном коде (преобразование последовательности импульсов в параллельный двоичный код), а также для деления частоты входных импульсов. В ЦВМ они используются для образования адресов команд, подсчета количества циклов и т.п. Счетчики выполняются на основе триггеров. По целевому назначению счетчики могут быть простыми (для суммирования или вычитания) или реверсивными (для работы в обоих режимах). По принципу работы различают:

· Асинхронные счетчики, информация у которых передается последовательно по цепочке триггеров, начиная с входного;

· Синхронные счетчики, у которых входные импульсы поступают одновременно на все триггеры счетчика.

Основным параметром счетчика является коэффициент или модуль счета К – это наибольшее число, которое может быть подсчитано счетчиком. В зависимости от значения модуля счета счетчики делятся на двоичные (К=2n , где n – число триггеров), декадные (К=10), с произвольным модулем счета.

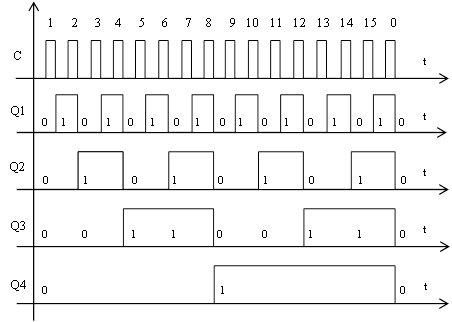

На рис. 146 представлен типичный четырехразрядный асинхронный счетчик-делитель на JK-триггерах. Диаграммы работы счетчика показаны на рис. 147. Каждый из триггеров делит частоту пополам, поэтому частота выходного сигнала Q4 равна 1/16 частоты входного сигнала синхронизации.

|

Рис. 147

Перед началом счета на входы R всех триггеров кратковременно подается низкий уровень сигнала (R=0) для предварительной очистки счетчика (для установки на всех прямых выходах Q триггеров логического ноля). Как видно из диаграммы счетчик на прямых выходах формирует линейно нарастающие кодовые наборы от 0000 до 1111, являющиеся двоичными эквивалентами десятичных чисел от 0 до 15. Шестнадцатый импульс переводит все триггеры в нулевое состояние. Модуль счета этого счетчика К=24=16.

Очевидно, что при счете импульсов на инверсных выходах триггеров формируются линейно убывающие коды от 1111 до 0000, что используется для реализации вычитающих счетчиков. В вычитающем счетчике синхронизирующий вход каждого триггера связан с инверсным выходом предыдущего триггера. Перед началом счета должна быть выполнена предварительная установка счетчика в состояние 1111.

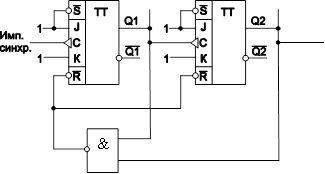

Для увеличения скорости счета применяют синхронные (параллельные) счетчики, у которых счетные импульсы поступают одновременно на входы синхронизации всех триггеров (рис. 148). Порядок переключения триггеров в таких счетчиках определяют логические схемы совпадения «И». В схеме рис. 148 первый импульс при условии J=K=1 изменит состояние только первого триггера (Q1=1) и одновременно подготовит к переключению второй триггер, т. к. для него будет J2=K2=1.

При модуле счета К<2n двоичный счетчик будет иметь избыточные состояния, которые необходимо исключить с помощью дополнительной комбинационной схемы. Например, если требуется создать суммирующий счетчик с К=6, то потребуется не менее 3-х триггеров, т.к. 22<6<23. Счетчик из 3-х триггеров возвращается в исходное состояние после 8-го импульса, а надо после 6-го. Избыточные состояния исключаются с помощью комбинационной схемы И-НЕ, которая после 6-го импульса, когда будет набран двоичный код 110, эквивалентный заданному К=6, подаст сигнал 0 на сбросовые R- входы триггеров и возвратит триггеры в исходное состояние Q1=Q2=Q3=0. Для исключения избыточных состояний входы логического элемента И-НЕ надо соединять только с выходами тех разрядов счетчика, на которых будут единицы при достижении кодового набора, соответствующего требуемому модулю счета К. Пример счетчика-делителя c модулем счета К=3 приведен на нижеследующем рисунке:

|

Задание: используя рисунок 147 нарисовать диаграммы работы этого счетчика-делителя.

Широкое распространение получили декадные (десятичные) счетчики с К=10. Декадный счетчик можно реализовать на основе схемы рис. 146, если дополнить ее логическим элементом 2И-НЕ, подав на его входы сигналы Q2=Q4=1 (1010 – двоичный код числа 10) для очистки счетчика по входу R с приходом 10-го импульса.

Различные счетчики изготовляются в виде готовых микросхем.

6.11. Регистры

Регистр (RG) – это последовательностное устройство, предназначенное для записи, хранения и (или) сдвига информации, представленной в виде многоразрядного двоичного кода. В зависимости от функционального назначения различают регистры сдвига (последовательные) и памяти (параллельные). Регистры выполняются на основе триггеров.

В четырехразрядном регистре сдвига, выполненном на JK-триггерах (рис. 149), с приходом каждого спадающего фронта тактового импульса синхронизации на входы «С» происходит запись сигналов с прямых и инверсных выходов на информационные входы каждого последующего триггера, от младшего разряда к старшему.

Если Вам понравилась эта лекция, то понравится и эта - 63 Гражданско-правовая защита ограниченных вещных прав.

Если на входе данных первого триггера имеем 0, т.е. J=0, К=1, то в исходном состоянии на выходах Q1=0,  =1. Эти же уровни сигналов последовательно передаются каждому триггеру после прихода тактовых импульсов, но не изменяют их состояния. Если же на входе первого триггера J=1, К=0, то после первого тактового импульса на его выходах установятся новые логические уровни Q1=1,

=1. Эти же уровни сигналов последовательно передаются каждому триггеру после прихода тактовых импульсов, но не изменяют их состояния. Если же на входе первого триггера J=1, К=0, то после первого тактового импульса на его выходах установятся новые логические уровни Q1=1,  =0; вторым тактовым импульсом в это состояние переключится второй триггер и т.д. (рис. 150). Очевидно, что четвертый тактовый импульс сдвинет уровень логической единицы в четвертый триггер, и на выходах разрядов регистра появится кодовый набор 1111.

=0; вторым тактовым импульсом в это состояние переключится второй триггер и т.д. (рис. 150). Очевидно, что четвертый тактовый импульс сдвинет уровень логической единицы в четвертый триггер, и на выходах разрядов регистра появится кодовый набор 1111.

|

Рис. 150

Регистры памяти применяются для хранения информации, представленной в виде двоичного кода. Такие регистры должны по тактовому разрешающему импульсу принимать параллельный код входной информации и хранить его до прихода следующего тактового импульса. Для построения регистров памяти наиболее удобны D–триггеры. На рис. 151 показана схема четырехразрядного регистра памяти К155ТМ5. Он содержит четыре тактируемых потенциалом D–триггера. Если на тактовые входы триггеров подан потенциал С=1, то информация с входов D1–D4 устанавливает триггеры в соответствующие состояния и эта информация появляется на выходах регистра. При С=0 триггеры хранят запомненную информацию вне зависимости от того, какие потенциалы присутствуют при этом на входах D1–D4.