Элементная база цифровых устройств

2. Элементная база цифровых устройств

2.1. Особенности структуры и элементной базы цифровых БИС и СБИС.

Базовые логические элементы (ЛЭ) предназначены для: логического преобразования информации, представленной в двоичном коде; формирования потенциальных (токовых) уровней сигналов с электрическими характеристиками, соответствующими кодируемой информации на выходе элемента. Для реализации функциональных блоков цифровых БИС обычно используют маломощные базовые ЛЭ, имеющие невысокую нагрузочную способность, содержащие небольшое количество компонентов (транзисторов, диодов, резисторов) и занимающих на кристалле возможно меньшую площадь.

Входные элементы согласования (ЭС) БИС (входные трансляторы) предназначены для:

а) защиты внутренних цепей БИС от внешних электрических нагрузок;

б) формирования внутренних для микросхем логических уровней;

в) хранения информации в процессе ее обработки в БИС;

Рекомендуемые материалы

г) согласования уровней внешних сигналов, подаваемых на входы БИС, с внутренними;

д) усиления входных сигналов;

е) повышения чувствительности, быстродействия и помехоустойчивости БИС.

Выходные ЭС БИС предназначены для:

а) формирования внешних логических уровней напряжения (тока); зашиты внутренних цепей БИС от внешних электрических перегрузок и помех;

б) усиления внутренних сигналов БИС;

в) формирования необходимых длительностей фронтов выходных сигналов.

г) обеспечения возможности работы нескольких устройств на одну линию связи.

2.2. Логические элементы и их характеристики

Основные параметры и характеристики логических элементов.

Логическое состояние элементов определяется значениями электрического потенциала на их входах и выходах. Элементы характеризуются следующей системой параметров: потенциалы, соответствующие 0 и 1; U0, U1, порог переключения Uп, число входов (коэффициент объединения по входу) М; входные токи I0вх при Uвх = U0 и I1вх при Uвх = U1 коэффициент разветвления по выходу N (нагрузочная способность); устойчивость к помехам положительной и отрицательной полярности Uп+, Uп- ; мощность Рэ или ток Iп , потребляемые от источника питания; задержки переключения t013 из состояния 0 на выходе в состояние 1 и t103 из состояния 1 в состояние 0. Параметры определяются по статическим и переходным характеристикам элементов.

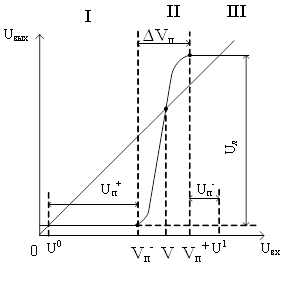

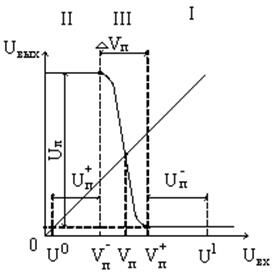

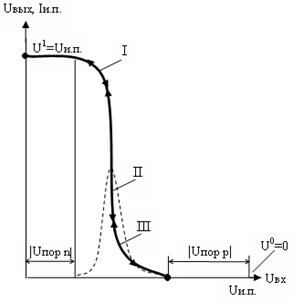

Основной статической характеристикой логических элементов является передаточная характеристика Uвых=f(Uвх) — зависимость потенциала на выходе от потенциала на одном из входов при постоянных значениях потенциала (U0 или U1) на остальных входах. По типу передаточной характеристики элементы делятся на инвертирующие, на выходе которых образуется инверсия входных сигналов (элементы НЕ, И—НЕ, ИЛИ—НЕ и др.), и неинвертирующие, сигналы на выходе которых не инвертируются элементы И, ИЛИ и др.).

|

а) б)

Рис. 2.1. Передаточные характеристики инвертирующего (а) и неинвертирующего

(б) логических элементов

Типичная передаточная характеристика инвертирующего элемента показана на рис. 2.1,а, неинвертирующего — на рисунке 2.1,б. Так как в цифровом устройстве должно быть обеспечено четкое разделение (квантование) уровней логических 0 и 1, то передаточная характеристика имеет три явно выраженных участка: I — соответствующий состоянию Uвых = U0, II — состоянию Uвых = U1, III — промежуточному состоянию. Значения потенциала Uвх, соответствующие границам участков, называются порогами переключения V0п и V1п область между порогами — зоной неопределенности.

Максимально допустимая величина потенциальной помехи, не вызывающая сбоя в цифровой схеме, называется помехоустойчивостью и определяется выражениями (рис. 2.1)

U+п = Vп0 – U0 ; U-п = U1–Vп1

U+п – U-п = Uл – ΔVп ,

где Uл = U1 – U0 — логический перепад: ΔVп =Vп0 - Vп1 — ширина зоны неопределенности.

Таким образом, для повышения помехоустойчивости надо увеличивать Uл и уменьшать ΔVп . Поэтому в цифровых схемах обеспечивают ΔVп < Uл и приближенно можно считать Vп0 ≈ Vп1 ≈ Vп , где Vп — средний порог переключения.

Максимальная величина логического перепада ограничивается напряжением питания Uл <= Uип , вследствие чего получаем (U+п+ U-п)<= Uип. Таким образом, сумма помехоустойчивостей U+п, U-п не превышает напряжения питания.

Чтобы одновременно получить достаточно высокие значения U+п, U-п, следует использовать такие схемы, в которых средний порог переключения Vп располагается приблизительно посередине между U0 и U1. В этом случае значения U+п и U-п равны и составляют

U+п≈ U-п ≈ Uп=0,5(Uл - ΔVп)≈ 0,5 Uл<= 0,5 Uип

Передаточные характеристики реальных схем имеют определенный разброс, обусловленный различием внешних условий, разбросом параметров компонентов и другими факторами. При этом значения уровней U0, U1 и порогов Vп0, Vп1 заключены в диапазонах

U0min<=U0<=U0max, V0п min<=V0п<=V0п max ,

U1min<=U1<=U1max, V1п min<=V1п<=V1п max .

Значения U+п и U-п определяются для наихудшего сочетания факторов

U+п= V0п max- U0min, U-п = U1min- V1п max.

Передаточная характеристика зависит от потенциалов шин питания (Uип) и земли (Uз=0). Действие помех Vш, возникающих на этих шинах, можно представить как изменение потенциалов U`ип=Uип±Vш, U`з=±Vш и определить получающуюся при этом передаточную характеристику. Помехоустойчивость находится с помощью этой передаточной характеристики как максимальная величина Vш, при которой сохраняются значения U+п, U-п>0.

Если на входы схемы или шины питания и земли поступают импульсные помехи амплитудой Vи и длительностью tи, то при достаточно больших значениях tи их действие аналогично действию потенциальной помехи такой же величины. Импульсные помехи малой длительности, сравнимой с временем переключения схемы (tи<= t013, t103), не успевают произвести ложное переключение схемы даже при значительной их амплитуде Vи. Таким образом, при уменьшении длительности помехи tи для создания сбоя требуется увеличение ее амплитуды, т. е. импульсная помехоустойчивость для большинства логических схем повышается при уменьшении длительности помехи.

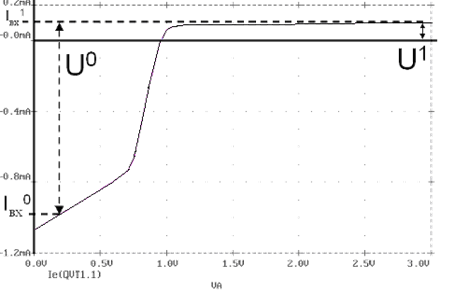

Входная характеристика ТТЛ элементов Iвх=f(Uвх), представленная на рис. 2.2, служит для определения входных токов: I0вх=>0, вытекающего из схемы при Uвх = U0, I1вх<=0 и втекающего в схему при Uвх = U1.

|

Рисунок 2.2. Входная характеристика ТТЛ-схемы.

Выходные характеристики логических элементов U0вых=f(I0н) и U1вых=f(I1н) показаны на рис 2.3.

Выходные характеристики логических элементов U0вых=f(I0н) и U1вых=f(I1н) показаны на рис 2.3.

Рис 2.3. Выходные характеристики логического элемента

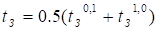

Динамические параметры определяются с помощью переходных характеристик.

Одним из важнейших динамических параметров является средняя задержка

которая определяет среднее значение время выполнения логических операций. Параметр  обычно рассчитывают по измеренным значениям

обычно рассчитывают по измеренным значениям  и

и  .

.

2.3. Элементы ТТЛ, ТТЛШ

2.3.1. Элемент ТТЛ с простым инвертором.

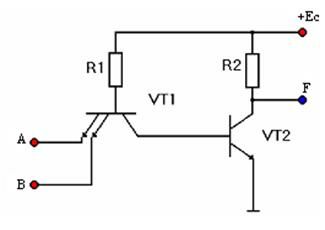

На рис.2.4, представлена схема элемента И-НЕ ТТЛ с простым инвертором. Схема элемента состоит из многоэмиттерного транзистора VT1, выполняющего логическую операцию И, и транзисторного ключа инвертора VT2. На выходе элемента реализуется функция И-НЕ.

Рис. 2.4. Схема элемента И-НЕ ТТЛ с простым инвертором

2.3.2. Элемент ТТЛШ с простым инвертором.

Транзисторно-транзисторная логика с диодами Шоттки (ТТЛШ) является одним из распространенных типов элементной базы цифровых логических микросхем различной степени интеграции, используемых в устройствах цифровой автоматики и вычислительной техники.

Наиболее эффективными для быстродействующих СБИС высокой функциональной сложности являются известные базовые ЛЭ, включающие быстродействующий ключевой транзистор, работающий в ненасыщенном режиме, и схему логической обработки сигналов на входе или выходе ключевого элемента.

На рис. 2.5,а приведена основная электрическая схема ЛЭ ТТЛШ такой структуры. Схема содержит ключевой транзистор VT2 с диодом Шоттки, в котором ограничение насыщения обеспечивается диодом Шоттки, и логическую схему с функцией И на основе МЭТ VTI. Такая схема имеет невысокий порог переключения (UТ ~ 0,5 В), широкий диапазон напряжений питания, высокое быстродействие.

а) б)

Рис. 2.5. Электрические схемы базовых логических элементов ТТЛШ СБИС:

а – основная схема логического элемента;

б – логический элемент с ограничением перепада напряжений диодами

На рис.2.5,б приведен вариант схем ЛЭ ТТЛШ такого типа с улучшенными характеристиками, а именно повышение быстродействия достигается за счет ограничения логического перепада напряжений Δ UТ, на выходе ЛЭ с помощью диодной цепочки VDI, VD2.

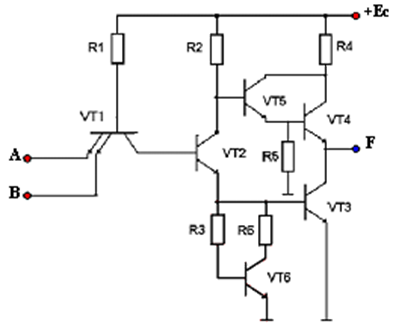

2.3.3. Схемы ТТЛ/ТТЛШ логики со сложным инвертором

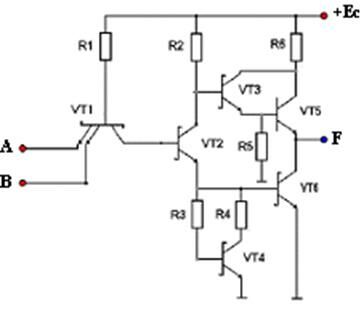

Серия К155

На рисунке 2.6 представлена схема логического элемента серии К155. Схема состоит из следующих каскадов: входного многоэмиттерного транзистора VT1 с малым инверсным коэффициентом усиления по току, фазорасщепляющего каскада, постоенного на проходном транзисторе VT2 (этот каскад работает в режиме с малым рабочим током и имеет малые емкости p-n переходов); выходного каскада (VT4, VT3). Транзистор VT3 рассчитан на большой рабочий ток и имеет малое время выхода из режима насыщения при переключении схемы. Через этот транзистор стекают на общую шину входные токи ключей-нагрузок.

Рис 2.6. Схема базового логического элемента серии К155

Высокое быстродействие микросхем ТТЛ при большой емкостной нагрузке объясняется тем, что как заряд, так и разряд нагрузочной емкости происходит через низкоомную выходную цепь. Однако при переключении выходных транзисторов есть момент, когда они оба открыты. Из-за этого в цепи питания схемы возникают кратковременные, но мощные импульсы тока, которые могут привести к появлению импульсов помехи. Во избежание этого в аппаратуре, построенной с применением микросхем ТТЛ, необходимо создавать цепи питания цифровых микросхем с малой индуктивностью проводников и предусматривать развязку между соседними платами устройства.

При Uвх1=0 (на один из эмиттеров транзистора VT1 подан потенциал «общий») переход база–эмиттер транзистора VT1 открыт, но образующийся при этом потенциал UбVT1 = 0,8 В не может открыть три p-n перехода: база–коллектор транзистора VT1, база–эмиттер транзистора VT2 и VT3 (для отрывания этой цепи необходим потенциал примерно 3∙0,6 = 1,8 В). Потенциал на базе транзистора VT3 близок к нулю, и транзистор VT3 закрыт. Потенциал на коллекторе VT2 и базе VT4, близкий к напряжению источника питания +5В, открывает переход база–эмиттер транзистора VT4, вызывая ток I1вых.

При увеличении Uвх (на всех эмиттерных входах транзистора VT1) до значения порогового напряжения Uпор1=0,8 В транзистор VT2 начинает открываться, но транзистор VT3 ещё закрыт, при дальнейшем увеличении Uвх до Uпор2=1,25 В транзистор VT2 открывается, а транзистор VT3 только начинает открывается.

Дальнейшее увеличение Uвх приводит к увеличению потенциала на базе транзистора VT1 до 1,2 В. Этого вполне достаточно, чтобы открыть два перехода: база–коллектор транзистора VT1 и база–эмиттер транзистора VT2. Транзистор VT2 открывается, ток через резистор R2 увеличивается, что вызывает уменьшение напряжения UкVT2. В базу выходного транзистора включена корректирующая цепочка, состоящая из резисторов из резисторов R3 и R6 и транзистора VT6. Эта цепочка позволяет получить передаточную характеристику, по форме близкую к прямоугольной, и тем самым повысить помехозащищенность схемы в состоянии «1».

Сопротивление корректирующей цепочки имеет малую зависимость от температуры, что обеспечивает ряд особых свойств схемы. При повышенной температуре (125 оС) время рассасывания для транзистора VT6 мало, что способствует быстрому выключению схемы. Это, в свою очередь, уменьшает импульсный ток короткого замыкания (когда транзисторы VT4 и VT3 открыты одновременно), а значит и динамическую мощность потребления. При пониженной температуре (–60 оС) сопротивление корректирующей цепочки высоко, что увеличивает ток включения транзистора VT3 и приводит к уменьшению времени включения схемы.

В выходном каскаде применена схема Дарлингтона (транзисторы VT5 и VT4), позволяющая повысить коэффициент усиления выходного транзистора по току и поэтому обеспечить примерно равные значения выходных сопротивлений схемы при её включении (определяется верхним эмиттерным повторителем VT4) и выключении (определяется насыщенным транзистором VT3). Это дает почти одинаковые задержки распространения сигнала при включении и выключении схемы.

Серия К531

На рисунке 2.7 представлена схема логического элемента серии К531. Повышение быстродействия здесь получено снижением степени насыщения транзисторов за счет применения диодов Шотки, шунтирующих переход коллектор–база насыщенного транзистора. Диоды Шотки имеют существенно меньшее пороговое напряжение открывания, чем переход коллектор–база, поэтому во время действия входного импульса диоды Шотки открываются раньше, чем переход коллектор–база, таким образом предотвращается накопление избыточных зарядов в базовой области транзисторов. Накопления зарядов в самих диодах Шотки не происходит, так как протекающий в них ток вызван переносом основных носителей.

Рис. 2.7. Схема базового логического элемента серии К531

Работа транзисторов Шотки в ненасыщенной области приводит к увеличению падения напряжения на их переходах база–эмиттер, что уменьшает в статическом режиме ток потребления и соответственно потребляемую мощность. В выходном каскаде применена схема Дарлингтона (VT3 и VT5), позволяющая при выключении схемы повышенный ток заряда емкостной нагрузки, что уменьшает время задержки фронта выходного сигнала. Благодаря малому падению напряжения на переходе база–эмиттер транзистора VT3, а также низкому выходному сопротивлению схемы в обоих логических состояниях схема Дарлингтона позволяет получить в микросхемах этой серии более высокий уровень выходного напряжения U1вых.

Преимущества ИС с диодами Шотки: введение диодов Шотки исключает накопление лишних базовых зарядов, увеличивающих время выключения транзистора, и обеспечивает стабильность времени переключения в диапазоне температур. Для получения крутой передаточной характеристики добавляется схема активного выключения, что повышает динамическую помехозащи- щенность при высоком напряжении. Фиксация входов с помощью диодов Шотки уменьшает отрицательные выбросы импульсов напряжения на входе.

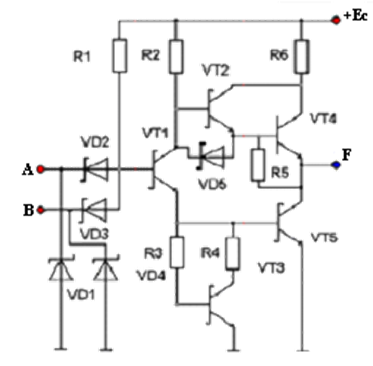

Серия К555(LS)

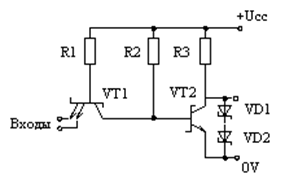

На рисунке 2.8. представлена схема логического элемента серии К555. Базовый логический элемент серии К555 состоит из трех основных каскадов: входного, реализующего функцию И, на диодах VD2, VD3 и резисторе R1; фазоразделительного на транзисторе VT1, резисторе коллекторной нагрузки R3 и резисторно-транзисторной (R3, R4, VT3), эмиттерной нагрузки; выходного двухканального усилителя с верхним плечом, состоящим из транзисторов VT2, VT4, включенных по схеме Дарлингтона с резистором R5 нагрузки VT2 и ограничительного резистора R6, и нижним плечом на транзисторе VT5.

Рис. 2.8. Схема базового логического элемента серии К555

Входной каскад реализует функцию И при напряжении высокого уровня на входах в положительной логике. При этом выходное напряжение равно входному напряжению минус прямое падение напряжения на входном диоде Шотки: Uвых = U1вх – UD. Напряжение Uвых превышает в этом случае суммарное прямое падение напряжения на переходах база – эмиттер транзисторов VT1 и VT5 последующих каскадов и создает ток в базу транзистора VT1 второго каскада из цепи питания через резистор R1. Входной ток элемента соответствует обратному току входных диодов, является втекающим и незначительным. При напряжении низкого уровня на одном из входов (или всех входах) каскада реализуется функция ИЛИ в отрицательной логике. При этом напряжение на выходе каскада Uвых = U0вх + UD. Значения его для этого случая ниже 2Uбэ последовательно включенных транзисторов VT1, VT5; ток через резистор R1 из цепи питания вытекает на вход элемента. Значение тока определяется разностью напряжения питания и входного напряжения с учетом прямого падения напряжения на входном диоде и номиналом резистора R1:

I0вх = [Ес – (U0вх + UD)]/ R1.

В фазоразделительном каскаде при (при напряжении высокого уровня на входе) протекает ток через его нагрузку. На эмиттерной нагрузке каскада поддерживается напряжение выше напряжения Uбэ транзистора VT5, и при этом обеспечивается базовый ток транзистора. На коллекторной нагрузке за счет протекающего через транзистор VT1 тока создается падение напряжения на резисторе R2 и напряжение на диоде VD5 ниже 2Uбэ транзисторов верхнего плеча выходного каскада VT2 и VT4. Ток в цепи диода VD5 – втекающий для фазоразделительного каскада. При напряжении низкого уровня на входе транзистор VT1 устанавливается в 0 по базе и на эмиттерной нагрузке напряжение близко к 0, напряжение Uк транзистора VT1 превышает примерно 2Uбэ транзисторов VT2 и VT4 и обеспечиваются базовые токи этих транзисторов.

Для выходного каскада нижнее плечо (транзистор VT5) находится в открытом состоянии за счет тока, протекающего в базу. Верхнее плечо каскада в этом случае закрыто. Выходное напряжение каскада соответствует напряжению на коллекторе открытого транзистора с диодом Шотки U0вых≈Uбэ– – UD. Ток нагрузки каскада для этого режима – втекающий. В режиме низкого уровня на входе нижнее плечо закрыто, верхнее открыто. Каскад создает на выходе ток, вытекающий в нагрузку, ограничиваемый резистором R6. Выходное напряжение соответствует высокому уровню U1вых ≈ Ес – (2Uбэ) –IR2.

Резистор R5 верхнего плеча выходного каскада создает необходимое напряжение на базе транзистора VT4 для его открывания. Для уменьшения потребляемой мощности при напряжении высокого уровня на выходе схемы резистор R5 подключен не к общей шине, а к выходу элемента. Диод VD5, включенный последовательно с R5 и параллельно резистору коллекторной нагрузки фазоразделительного каскада R2, позволяет уменьшить задержку включения схемы за счет использования части энергии, запасенной в емкости нагрузки, для увеличения тока коллектора транзистора VT1 в переходном режиме. Верхнее плечо выходного каскада выполнено на транзисторах VT2 и VT4 по схеме Дарлингтона, что обеспечивает высокий коэффициент усиления каскада в состоянии высокого уровня, повышает нагрузочную способность схемы и улучшает динамические свойства. Ток заряда емкости нагрузки в динамическом режиме пропорционален току короткого замыкания. Транзистор VT4 реализуется без диодов Шотки, то есть работает в активном режиме. К внешним входам ИС подключены антизвонные диоды, ограничивающие напряжение отрицательных помех.

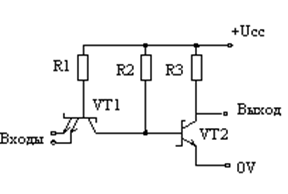

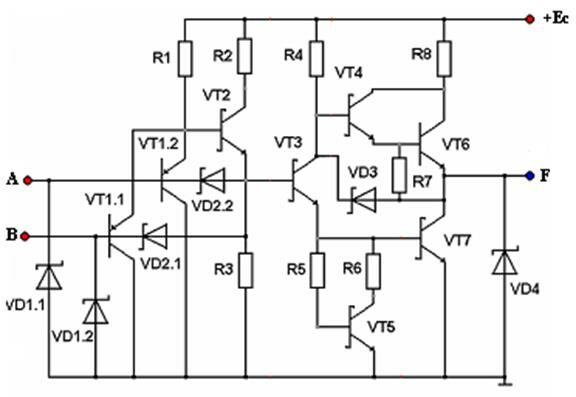

Серия К1533(ALS)

На рисунке 2.9 представлена схема логического элемента серии К1533. Схема имеет следующие преимущества по сравнению со схемой серии К555: полное ограничение диодом Шотки всех насыщающихся транзисторов, что способствует исключению накопления излишнего базового заряда и значительно уменьшает время выключения транзисторов; устранение излишнего накопления заряда, что позволяет получить более стабильное время переключения в диапазоне температур; обеспечение улучшения динамической помехоустойчивости при высоком логическом уровне за счет активного выключения выходного транзистора.

Рис. 2.9. Схема базового логического элемента серии К1533

Схема имеет следующие преимущества по сравнению со схемой серии К555: полное ограничение диодом Шотки всех насыщающихся транзисторов, что способствует исключению накопления излишнего базового заряда и значительно уменьшает время выключения транзисторов; устранение излишнего накопления заряда, что позволяет получить более стабильное время переключения в диапазоне температур; обеспечение улучшения динамической помехоустойчивости при высоком логическом уровне за счет активного выключения выходного транзистора.

Входной порог переключения устанавливается транзисторами при следующем соотношении: Uпор = UбэVT2 + UбэVT3 + UбэVT7 – UбэVT1 = 1,3 В. В схеме серии К555 в отличие от приведенной выше отсутствует транзистор VT2. Когда открывается выходная схема Дарлингтона (транзисторы VT4, VT6), позволяющая осуществить формирование сигнала на выходе с сохранением низкого выходного сопротивления при высоком и низком логических уровнях, на выходе устанавливается напряжение высокого уровня U1вых при выходном сопротивлении, равном 10 Ом.

При небольших токах нагрузки схема Дарлингтона находится в ненасыщенном состоянии. При увеличении тока нагрузки она насыщается и выходное сопротивление возрастает до 58 Ом, определяясь в основном сопротивлением R8 = 50 Ом. Это сопротивление обеспечивает защиту каскада от короткого замыкания. Стабильность выходного напряжения высокого уровня U1вых осуществляется благодаря активному выключению транзистора VT7 транзистором VT5. Выходное напряжение определяется как

U1вых = Ес – (IбVT4R3 + UбэVT4 + UбэVT6)

Выходное напряжение низкого уровня U0вых устанавливается транзистором VT7, когда он включен. Этот транзистор включается цепью VT3, R4, когда на входе схемы высокий логический уровень, а транзистор VT2 включен.

2.4. Элементы КМОП логики

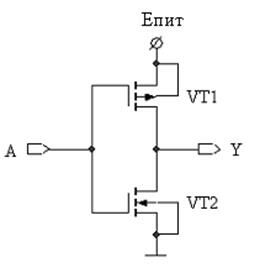

2.4.1. Инвертор на комплементарных транзисторах

Схема инвертора (рис.2.10) содержит транзисторы VTn и VTp с каналами соответственно n- и р-типа. В структуре на кремниевой подложке последняя соединяется с общей шиной. Для p-канального транзистора «подложкой» служит n-область кармана, соединяемая с плюсом источника питания.

При UBX = U1 = UИП транзистор VTn открыт, a VTp закрыт. На выходе получаем UBЫХ = U0 ≈ 0. Если UBХ = U0 = 0, то, наоборот, транзистор VTn закрыт, a VTP открыт и UBЫХ = U1 = UИП.В обоих состояниях ток, потребляемый от источника питания, практически равен нулю. Предполагается, что выход инвертора соединен со входами аналогичных инверторов-нагрузок. Таким образом, мощность, потребляемая в статическом режиме, практически равна нулю, что является важнейшим преимуществом по сравнению с любыми другими микросхемами.

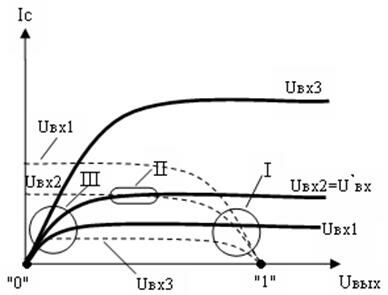

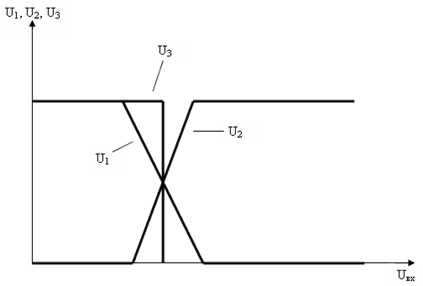

На рис. 2.11, а показана передаточная характеристика инвертора (сплошная линия). С помощью рис. 2.11, б можно пояснить графический метод ее построения. На нем сплошными линиями изображены стоковые характеристики n-канального транзистора ICn(UВЫХ), а штриховыми – стоковые характеристики p-канального транзистора ICp(UВЫХ) при одних и тех же входных напряжениях UBX3> UBX2> UВХ1> UПОР. Пороговые напряжения для простоты предполагаются одинаковыми для обоих транзисторов. При малых UВХ точки пересечения ВАХ лежат в области I, где n-канальный транзистор работает в режиме насыщения, а p-канальный не насыщен. Это соответствует области I передаточной характеристики на рис. 2.11, а. Когда входное напряжение достигает UВХ2 = U’BX, оба транзистора находятся в режиме насыщения, а выходное напряжение изменяется скачкообразно в пределах области II на рис. 2.11, а, б. При UВХ > U’BX p-канальный транзистор работает в режиме насыщения, а n-канальный не насыщен, чему соответствует область III на передаточной характеристике.

Рис. 2.10. Схема инвертора Рис. 2.11 а. Передаточная характеристика

КМОП-инвертора

Рис. 2.11 б. Передаточная характеристика КМОП-инвертора

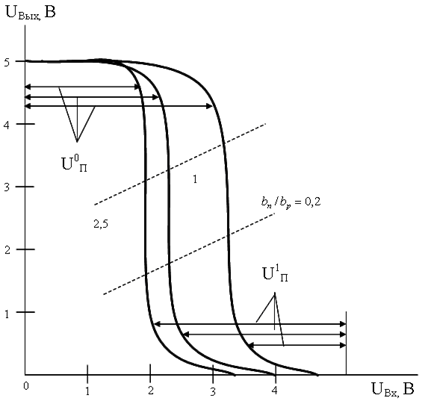

Оптимальная форма передаточной характеристики достигается при одинаковых параметрах транзисторов (bn = bp, UПОРn = |UПОРp|). Тогда U’ВХ = UИП/2, помехоустойчивость максимальна и близка к UИП/2, а коэффициент помехоустойчивости UП/UЛ = 0,4 ... 0,5. Столь высокие значения не достигаются в инверторах других типов, в том числе на биполярных транзисторах. Это обусловлено минимальным значением U0 = 0, максимальным значением U1 = UИП и оптимальной (симметричной) передаточной характеристикой. К тому же она практически не зависит от температуры. Высокая помехоустойчивость в широком интервале температур – также важное преимущество.

На рис. 2.12 показано влияние параметра bn/bp, зависящего от геометрических размеров транзисторов, на передаточную характеристику (UИП = 5 В, |UПОР| = UПОРn= 0,7 В). Между параллельными штриховыми линиями находится область II, проходящая практически вертикально, где оба транзистора работают в режиме насыщения. С ростом bn/bp характеристика смещается влево, помехоустойчивость U0П уменьшается, а U1П увеличивается.

Из-за разной подвижности электронов и дырок (µn/µp = 2,5) для выполнения условия bn/bp = 1 требуется разная ширина каналов транзисторов (Wp/Wn = µn/µp), длина каналов обычно выбирается одинаковой. При этом площадь инвертора не получается минимальной. При одинаковых геометрических размерах транзисторов, обеспечивающих минимальную площадь, получаем bn/bp = µn/µp, что ухудшает форму передаточной характеристики (см. рис. 2.12) и снижает помехоустойчивость U0П (на 20%).

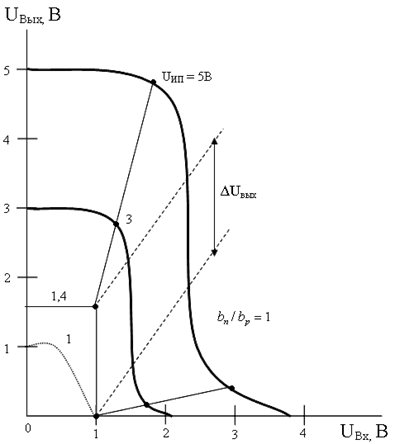

На рис. 2.13 показано изменение передаточной характеристики в зависимости от напряжения питания. Напряжение U’ВХ, соответствующее вертикальному участку (между штриховыми линиями), снижается пропорционально UИП, в то же время протяженность этого участка (ΔUВЫХ) не изменяется вплоть до UИ.П.МИН = UПОРn + |UПОРp|, когда характеристика близка к прямоугольной. Помехоустойчивость U0П, U1П изменяется пропорционально UИП; при UИП = UИ.П.МИН помехоустойчивость U0П = U1П = UПОР (если UПОРn = |UПОРp| = UПОР) независимо от значения bn/bp. Коэффициенты помехоустойчивости UП/UЛ постоянны вплоть до UИ.П.МИН. Таким образом инвертор может работать в широком интервале напряжений питания (практически UИП=2...15 В) без ухудшения относительной помехоустойчивости, что является существенным достоинством, которым не обладают другие микросхемы. Работоспособность сохраняется и при UИП < UИ.П.МИН (пунктирная линия), пока напряжение питания превышает большую из величин UПОРn или |UПОРp|, но помехоустойчивость мала и работать при таких напряжениях не рекомендуется.

Быстродействие инвертора оценивается средней задержкой tзд.ср. = 0,5(t1,0 + t0,1), где времена переходов t1,0, t0,1 при подаче прямоугольного импульса на вход определяются процессами разряда нагрузочной емкости через n-канальный и заряда ее через р-канальный транзистор.

.

.

где токи насыщения определяются выражениями

,

,

а временные коэффициенты – формой ВАХ транзисторов.

Если пороговые напряжения составляют (0,l…0,5)UИП, то kT = 1,2...1,6; для грубых оценок можно полагать t1,0T = t0,1T = 1,4. Нагрузочная емкость складывается из суммарной входной емкости нагрузок n(СЗИn + СЗИp), емкости соединительных проводников  и выходной емкости инвертора, равной сумме емкостей р-n переходов сток – подложка обоих транзисторов:

и выходной емкости инвертора, равной сумме емкостей р-n переходов сток – подложка обоих транзисторов:

В случае bn = bp, оптимальном с точки зрения помехоустойчивости, получаем t0,1T = t1,0T (при UПОРn = |UПОРp|). Однако значение tзд.ср не является минимальным, так как большая ширина канала транзистора VTp, обусловливает большие емкости СЗИр, ССПр и общую емкость СН. Минимальное значение tзд.ср (т. е. максимальное быстродействие) достигается при  , тогда

, тогда  .

.

Рис. 2.12. Влияние параметра bn/bp на передаточную

характеристику.

Рис. 2.13 Передаточная характеристика при различных напряжениях питания

В результате быстродействие инвертора на комплементарных транзисторах выше, чем на n-канальных, несмотря на большую нагрузочную емкость и большее вследствие этого значение t1,0. Оценка tзд.ср дает СН = 0,34 пФ (вместо 0,17 пФ) и tзд.ср = 1,5 нс (вместо 13 нс) при UИП = 5 В. Быстродействие увеличивается с ростом напряжения питания, так как токи насыщения в формулах (2.13) пропорциональны (UИП - UПОР)2. В пределах UИП = 2...15 В величина tзд.ср изменяется от 6 до 0,4 нс. Типичное значение tзд.ср = 1 нс.

В импульсном режиме основная часть потребляемой мощности расходуется на перезаряд нагрузочной емкости. За период Т поступающих на вход прямоугольных импульсов емкость перезаряжается дважды, на что необходима энергия CHU2ИП, поэтому мощность

где f – частота следования импульсов. На низких частотах (порядка 1 кГц) мощность составляет единицы нановатт. На максимальной частоте 1/10 tзд.ср (десятки мегагерц) мощность составляет десятые доли или единицы милливатт, что все же меньше, чем для инверторов на n-канальных транзисторах. Реальная потребляемая мощность на 10...20% выше рассчитанной, из-за кратковременного протекания «сквозного тока» через оба транзистора при переключении.

2.4.2. Логические элементы на комплементарных транзисторах (КМОП).

Для реализации функции И-НЕ применяется последовательное включение n-канальных и параллельное включение p-канальных транзисторов (рис. 2.14, а). При тех же геометрических размерах транзисторов, что и в инверторе, ток, задаваемый n-канальными транзисторами и открытом состоянии, уменьшается в т раз, а ток, задаваемый р-канальными транзисторами, увеличивается в m раз. Поэтому ЛЭ И-НЕ имеет характеристики и параметры, близкие к инвертору, эффективная удельная крутизна транзисторов которого bnЭФ = bn/m, bpЭФ = mbp. С ростом m параметр bnЭФ/bpЭФ уменьшается, передаточная характеристика сдвигается вправо и уменьшается помехоустойчивость U1П (см. рис. 2.12). При m ≥ 5 помехоустойчивость U1П стремится к |UПОРp|. Если этого недостаточно, надо увеличивать ширину канала транзисторов VTn (Wn > Wp) для повышения bn/bp.

С увеличением m время t1,0 линейно возрастает, a t0,1 во столько же раз убывает, поэтому средняя задержка изменяется сравнительно медленно. При одинаковых размерах транзисторов (Wn = Wp) величина tзд.ср для m = 1 и m = 4 отличается только в 1,3 раза. Таким образом, элемент И-НЕ на комплементарных транзисторах характеризуется гораздо более слабой зависимостью быстродействия от m по сравнению с элементом на n-канальных транзисторах. Для больших m (более 4...5)t0,1 « t0,1 и средняя задержка возрастает пропорционально m.

Рис. 2.14, а. Элемент И-НЕ

Для реализации функции ИЛИ-НЕ применяется параллельное включение n-канальных и последовательное включение р-канальных транзисторов (рис. 2.14,6). Логический элемент ИЛИ-НЕ имеет характеристики и параметры, близкие к характеристикам и параметрам инвертора с эффективной удельной крутизной транзисторов bnЭФ = mbn, bpЭФ = bp/m. С ростом m передаточная характеристика сдвигается влево и уменьшается помехоустойчивость U0П, стремящаяся в пределе (при m > 4...5) к UПОРn. Время t0,1 линейно возрастает, а время t1,0 убывает. При одинаковых геометрических размерах транзисторов t0,1 значительно больше t1,0, даже если m = 1. Поэтому средняя задержка увеличивается примерно пропорционально m, т.е. гораздо сильнее, чем в элементе И-НЕ.

Оптимальным с точки зрения быстродействия является соотношение  . Для m = 2...4 получаем Wp/Wn = 2...3, т. е. размеры р-канальных транзисторов должны быть существенно больше, чем n-канальных. Это ведет к росту площади, занимаемой ЛЭ на кристалле, и повышению нагрузочной емкости (по сравнению с элементом И-НЕ). Поэтому даже в оптимальном случае быстродействие элементов ИЛИ-НЕ (в предположении, что они нагружены на подобные ЛЭ) примерно в 2 раза хуже, чем элементов И-НЕ. Таким образом, в КМОП-микросхемах предпочтительнее использовать элементы И-НЕ.

. Для m = 2...4 получаем Wp/Wn = 2...3, т. е. размеры р-канальных транзисторов должны быть существенно больше, чем n-канальных. Это ведет к росту площади, занимаемой ЛЭ на кристалле, и повышению нагрузочной емкости (по сравнению с элементом И-НЕ). Поэтому даже в оптимальном случае быстродействие элементов ИЛИ-НЕ (в предположении, что они нагружены на подобные ЛЭ) примерно в 2 раза хуже, чем элементов И-НЕ. Таким образом, в КМОП-микросхемах предпочтительнее использовать элементы И-НЕ.

Рис. 2.14, б. Элемент ИЛИ-НЕ

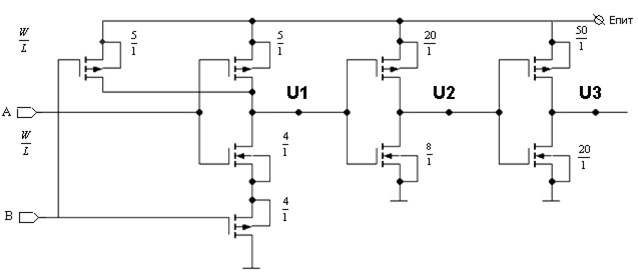

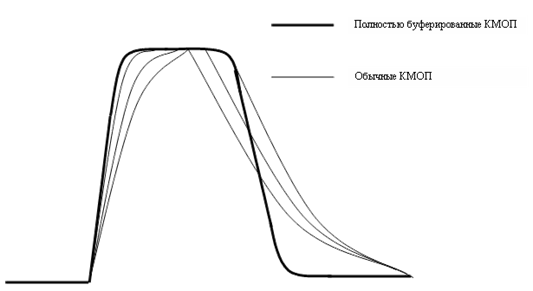

2.4.3. Буферированные КМОП

Благодаря уменьшению размеров становится возможным выпускать буферированные КМОП с улучшенными характеристиками. Это реализуется путем добавления двух инверторов без существенного изменения размеров ячейки. Например, на рис. 2.16, а показан результат буферирования ячейки И-НЕ, исходная схема которой дана на рис. 2.15. Времена нарастания и спада выходного сигнала в схеме на рис. 2.15,а зависят от сочетания входных сигналов, что показано тонкими линиями на рис. 2.16,б. В буферированной КМОП-схеме благодаря усилению сигналов парой инверторов (рис.2.16, а) этот недостаток удалось устранить (см. утолщенную линию на рис. 2.16,б). Улучшаются и передаточные характеристики (рис. 2.16, в), что ведет к повышению помехоустойчивости схем.

Рис. 2.15. Ячейка И-НЕ с двумя входами

Рис. 2.16,а. Буферированная ячейка И-НЕ

Рис. 2.16,б. Временная задержка

Рис. 2.16, в. Передаточная характеристика

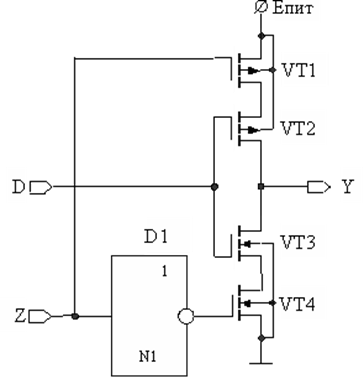

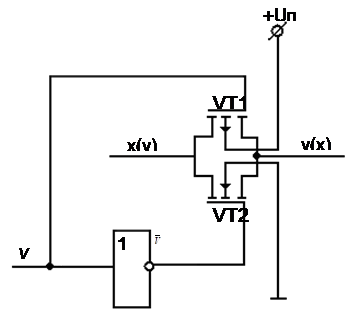

2.4.4. Схема КМОП логики с тремя состояниями выхода

Рис.2.17. Схема КМОП логики с тремя состояниями выхода

При Z = “0” схема работает как обычный инвертор, а при Z = “1” транзисторы VT1 и VT4 закрываются и схема переходит в высокоомное состояние, что позволяет нескольким устройствам работать на одну линию связи.

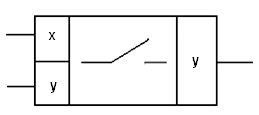

2.4.5. Двунаправленный ключ

а

б

Рис. 2.18. Двунаправленный ключ

При V = “0” транзисторы VT1 и VT2 открыты – ключ замкнут, и при V = “1” транзисторы VT1 и VT2 закрыты – ключ находится высокоомном состоянии.

2.5. БиКМОП логика

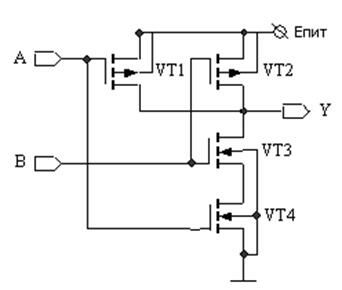

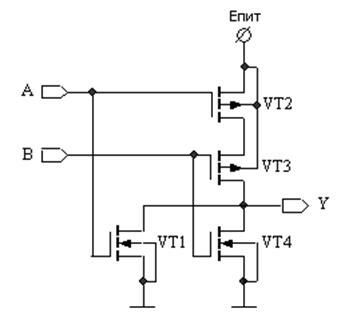

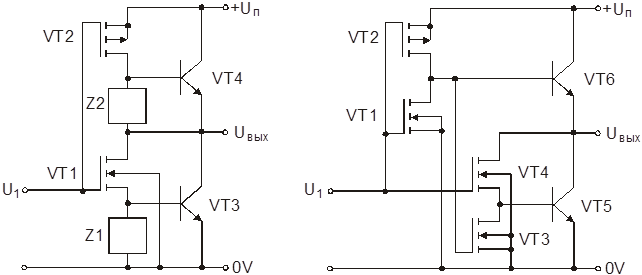

БиКМОП логика позволяет сочетать в интегральных схемах преимущество КМОП логики в малых потребляемых мощностях и преимущество биполярной логики в быстродействии. Логические функции в БиКМОП логике обычно реализуются в КМОП каскаде, который строится по принципам КМОП логики. Отличие БиКМОП от КМОП заключается в выходном каскаде, обычно включающем биполярные n-p-n транзисторы (рисунок 2.19, а). Использование n-p-n и p-n-p транзисторов не эффективно из-за большого расхождения их характеристик и, как следствие, различия в задержках включения и выключения БиКМОП схемы. Кроме того, это требует использования в одной схеме сразу четырех типов транзисторов, что создает существенные технологические сложности.

a) б)

Рис. 2.19. Электрическая принципиальная схема БиКМОП инвертора: R+R(а) и N+N

типа (б)

На рисунке 2.19, а транзистор VT4 предназначен для заряда емкости нагрузки и формирования выходного напряжения высокого уровня, транзистор VT3 предназначен для разряда емкости нагрузки и формирования выходного напряжения низкого уровня. Для разряда емкости базы транзисторов VT3 и VT4 используются элементы Z1 и Z2, в качестве которых могут выступать: резисторы (схема R+R типа), n-МОП транзисторы (N+N тип, рисунок 2.19, б), и сочетание резистора и n-МОП транзистора (R+N тип).

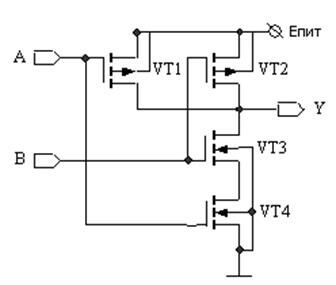

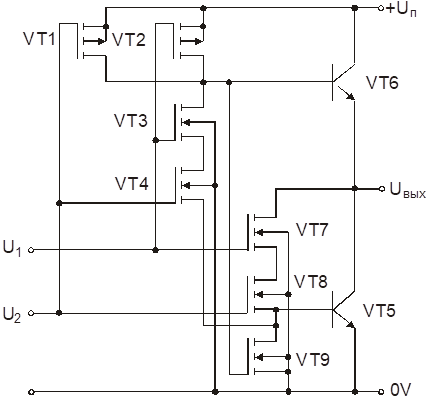

Рис. 2.20. Электрическая принципиальная схема

БиКМОП элемента И-НЕ.

Рассмотрим основные принципы функционирования БиКМОП схем на примере элемента И-НЕ N+N типа, разработанного фирмой Motorola. Положим, что на входе U2 высокий уровень напряжения и, соответственно, транзисторы VT8 и VT4 открыты, а транзистор VT1 закрыт. При низком уровне напряжения  на входе U1 n-МОП транзисторы VT3, VT7 закрыты, n-МОП транзистор VT9 открыт и удерживает в закрытом состоянии выходной n-p-n транзистор VT5. При этом открытый p-МОП транзистор VT2 удерживает в открытом состоянии выходной n-p-n транзистор VT6, который формирует на выходе высокий уровень напряжения

на входе U1 n-МОП транзисторы VT3, VT7 закрыты, n-МОП транзистор VT9 открыт и удерживает в закрытом состоянии выходной n-p-n транзистор VT5. При этом открытый p-МОП транзистор VT2 удерживает в открытом состоянии выходной n-p-n транзистор VT6, который формирует на выходе высокий уровень напряжения

.

.

При высоком уровне напряжения на входе U1  МОП-транзисторы VT2, VT9 закрыты, вследствие чего выходной n-p-n транзистор VT6 закрыт. Открытые n-МОП транзисторы VT3 и VT4 удерживают в базе выходного транзистора VT6 уровень, близкий к нулю, а открытые МОП транзистор VT7 и VT8 обеспечивают открытое состояние выходного n-p-n транзистора VT5. При этом на выходе схемы установится низкий уровень напряжения

МОП-транзисторы VT2, VT9 закрыты, вследствие чего выходной n-p-n транзистор VT6 закрыт. Открытые n-МОП транзисторы VT3 и VT4 удерживают в базе выходного транзистора VT6 уровень, близкий к нулю, а открытые МОП транзистор VT7 и VT8 обеспечивают открытое состояние выходного n-p-n транзистора VT5. При этом на выходе схемы установится низкий уровень напряжения

.

.

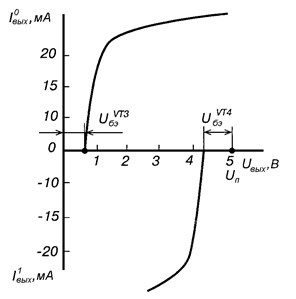

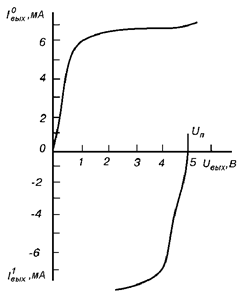

Выходная характеристика схемы приведена на рисунке 2.21, а, из которого видно, что БиКМОП схема имеет худшие значения выходных уровней UOL, UOH и меньшую помехозащищенность, чем КМОП.

а) б)

Рис.2.21. Выходная характеристика БиКМОП элемента типа N+N (а)

и КМОП элемента (б).

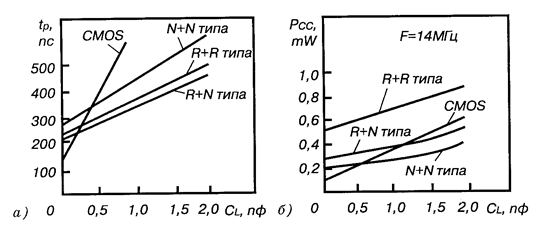

Среднее время задержки для БиКМОП схем по сравнению с КМОП больше при малых емкостях нагрузки, но значительно меньше при больших емкостях и равно

,

,

где CL - емкость нагрузки;

- ток стока n-МОП (p-МОП) транзистора;

- ток стока n-МОП (p-МОП) транзистора;

β - коэффициент усиления биполярных транзисторов.

БиКМОП схема типа N+N практически не потребляет ток в статическом состоянии. При низких уровнях напряжения на входах транзисторы VT3, VT4, VT7, VT8 и VT5 закрыты, транзисторы VT1, VT2, VT9 и VT6 открыты и цепь протекания тока между выводами +UCC и 0V отсутствует. Аналогична ситуация и при высоком потенциале на входе: транзисторы VT1, VT2, VT9 и VT6 закрыты, VT3, VT4, VT7, VT8, VT5 открыты и цепи протекания сквозного тока также нет. В динамическом режиме потребляемая мощность равна

Возбудитель сапа - лекция, которая пользуется популярностью у тех, кто читал эту лекцию.

,

,

где S - скважность импульсов;

f - частота переключения.

Схема типа R+N типа позволяет снизить выходное напряжение низкого уровня до значения близкого к нулю, а схема R+R типа позволяет получить выходные уровни  ,

,  . Однако эти типы схем отличаются по быстродействию, потреблению мощности, занимаемой площади и стабильности характеристик (номиналы резисторов) (рис. 2.22).

. Однако эти типы схем отличаются по быстродействию, потреблению мощности, занимаемой площади и стабильности характеристик (номиналы резисторов) (рис. 2.22).

Рис. 2.22. Сравнительные характеристики быстродействия (а) и динамической мощности потребления (б) различных типов БиКМОП схем от емкости нагрузки.