Основные узлы цифровых устройств

Глава III. Основные узлы цифровых устройств

§ 3.1 Назначение, классификация триггеров

Триггерами называют цифровые устройства, которые имеют два устойчивых состояния и мгновенно переходят из одного состояния в другое посредством управляющих сигналов. В термин мгновенное вкладывают смысл максимального быстродействия данного логического элемента. Триггеры являются основой для построения запоминающих устройств и способны хранить один вид информации.

В зависимости от функционального назначения, все триггеры подразделяют:

А) R-S-триггеры (R – С – S – триггеры) или триггеры с установочными входами. Они являются основой для построения статических запоминающих устройств, и нашли широкое применение для устранения эффекта «дребезга» контактов.

Б) Т-триггеры (счетные триггеры). Являются основой для построения двоичных счетчиков или используются в качестве делителей частоты.

В) D-триггеры (триггеры задержки). Используются в качестве построения регистров хранения и регистров сдвига. Являются неотъемлемой составляющей частью микропроцессора.

Г) J-K-триггеры (или универсальные триггеры). Свое название получили потому, что с помощью них можно создать любой из вышеперечисленных триггеров.

Основными характеристиками любого из триггеров являются:

Рекомендуемые материалы

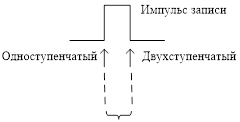

- одно- или двухступенчатые. Данный параметр определяет в какой момент по отношению к импульсу записи появляется информация на его выходе.

Момент, когда появляется информация на выходе триггера.

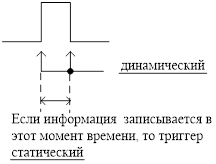

- динамический или статический триггер.

Динамический триггер – это триггер, если информация записывается в него в момент перепада импульса записи.

Статический триггер – если информация записывается в него по уровню импульса записи.

§ 3.2 R-S-триггеры. Синхронные R-S-триггеры

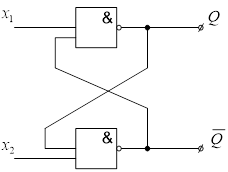

Данный класс триггеров является простейшим и так же является основой для построения всех других классов триггеров. Для построения R-S –триггеров достаточно двух элементов: ИЛИ-НЕ или И-НЕ.

Схемотехника их построения следующая:

А)

и

и  - установочные входы,

- установочные входы,

- выходы триггера.

- выходы триггера.

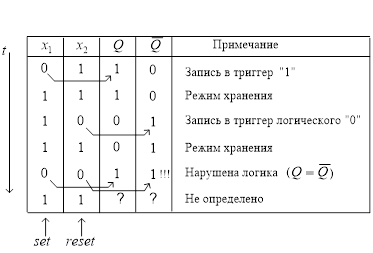

Рассмотрим работу такого устройства на примере таблицы истинности, привязанной к последовательности событий:

На основании двух последних выводов в таблице,  =

=  = 0 называется запрещенным состоянием.

= 0 называется запрещенным состоянием.

С помощью уровня запрещенного состояния определяется уровень логического 0, а именно, какой уровень входного сигнала осуществляет запись в триггер одного бита информации.

Как видно из таблицы, для данного триггера активным является уровень логического нуля.

Б) Триггер на элементах ИЛИ-НЕ.

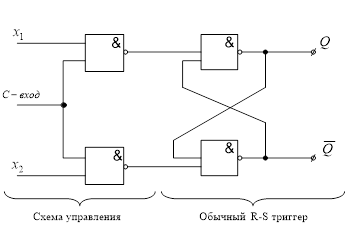

В) Синхронный R-S – триггер: в тех случаях, когда необходимо зафиксировать моменты записи в триггер информации, используют синхронные или синхронизируемые R-S-триггеры. В этом случае триггер состоит из двух составных частей и строится по следующей схеме:

В данном случае, при С=0, состояние входов  и

и  - безразлично, а встроенный R-S-триггер находится в режиме хранения. Т.е. в этот момент запись информации в триггер невозможна.

- безразлично, а встроенный R-S-триггер находится в режиме хранения. Т.е. в этот момент запись информации в триггер невозможна.

При С=1 активизируются установочные входы  и

и  и управление R-S – триггером становится невозможным. Но поскольку есть инверсии у элементов схемы управления, то изменяется на противоположный активный уровень R-S-триггера.

и управление R-S – триггером становится невозможным. Но поскольку есть инверсии у элементов схемы управления, то изменяется на противоположный активный уровень R-S-триггера.

А именно: при  =1,

=1,  = 0 – запись «1» → set;

= 0 – запись «1» → set;

при  =0,

=0,  = 1 – запись «0» → reset.

= 1 – запись «0» → reset.

Поэтому вход  - RESET,

- RESET,  - SET.

- SET.

Функционально вход С – вход записи.

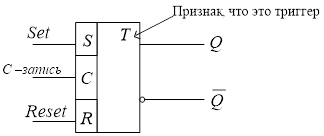

Графически: синхронный R-S-триггер образуется следующим образом:

Активный уровень – «1».

§ 3.3 Т-триггеры, D- триггеры и J-K-триггеры

Основой для построения данных классов триггеров является синхронный R-C-триггер.

I. Т-триггер (или счетный триггер) – предназначен для подсчета входных двоичных (прямоугольных) импульсов. Дополнительно их используют в качестве делителей частоты.

Различают одно- и двухступенчатые Т-триггеры.

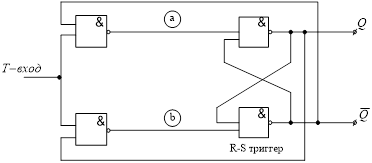

А) Схемотехника одноступенчатого:

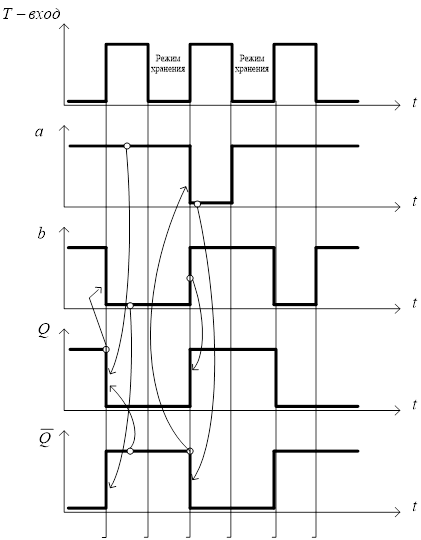

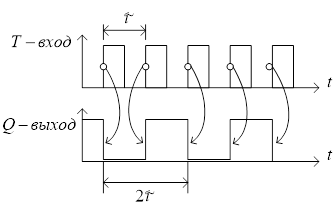

Рассмотрим временную диаграмму работы такого устройства:

Как видно из временных диаграмм, в данном случае Т-триггер – это устройство, которое меняет свое состояние на противоположное по фронту каждого входного импульса. Т.е. в потоке прямоугольных импульсов выполняется следующее условие:

Как видно из данных диаграмм, период следования выходных импульсов увеличивается ровно вдвое, следовательно частота выходных импульсов ровно вдвое уменьшается. Т.е. отдельно взятый Т-триггер является делителем частоты на два.

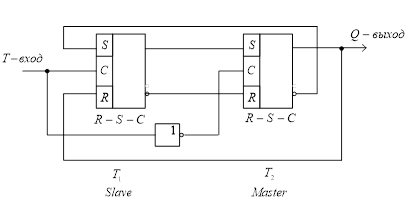

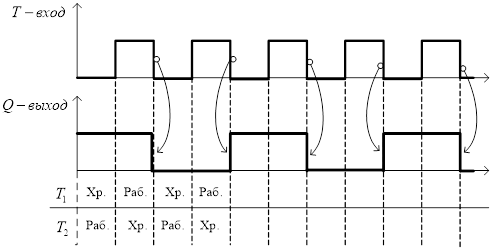

Б) При построении двоичных счетчиков, основу которых составляют Т-триггеры, желательно использование двухступенчатых Т-триггеров, схемотехника построения которых следующая:

В данном случае принцип работы Т-триггера аналогичен предыдущему, с тем отличием, что при Т=0,  - в режиме хранения, а

- в режиме хранения, а  - в рабочем режиме.

- в рабочем режиме.

=> ранее записанная в  информация перезаписывается в триггер

информация перезаписывается в триггер  .

.

При Т=1, наоборот,  - в рабочем состоянии, а

- в рабочем состоянии, а  - в режиме хранения.

- в режиме хранения.

=> инверсная информация с  переписывается в

переписывается в  .

.

Т.о. данное устройство также изменяет свое состояние на противоположное по каждому входному импульсу, но выполняет эту процедуру по срезу:

II. D-триггер (триггер задержки) – используется для формирования расчетов хранения.

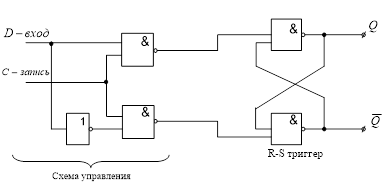

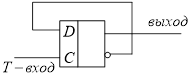

А) Одноступенчатый D-триггер:

D-триггер в счетном режиме включается так:

Наличие в схеме элемента НЕ автоматически устраняет возможность появления запрещенного состояния для R-S-триггера. В остальном работа устройства аналогична работе синхронного R-S-триггера.

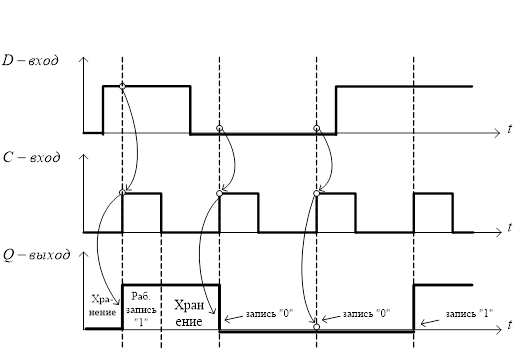

Т.е. реализуется следующая временная диаграмма:

Данное устройство осуществляет запись информации со входа D в триггер по фронту импульса С. В связи с этим вход С часто называют входом записи, а вход D – информационным входом.

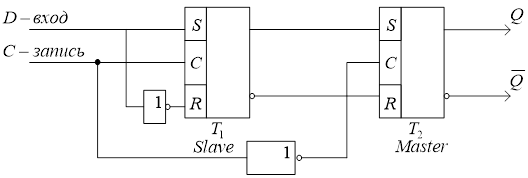

Б) Двухступенчатый D-триггер:

Принцип работы аналогичен одноступенчатому D-триггеру, с той лишь разницей, что по окончании импульса записи триггер  записывает в себя информацию с триггера

записывает в себя информацию с триггера  => на выходе переписанная с D-входа информация появится по окончании импульса записи.

=> на выходе переписанная с D-входа информация появится по окончании импульса записи.

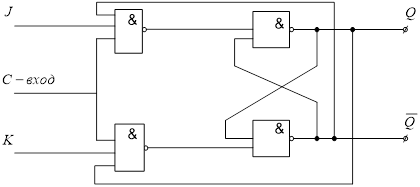

III. J-K-триггер (универсальный)

А) Одноступенчатый J-K-триггер:

С помощью анализа работы устройства легко доказать, что входы J и K эквивалентны входам R и S синхронного R-S-триггера. Вход J устанавливает «1», вход К – «0».

Если J=K = «1», то получаем классический одноступенчатый Т-триггер.

Если вход дополнить элементом НЕ:

, то получаем D-триггер.

, то получаем D-триггер.

Т.о. действительно J-K-триггер позволяет создать любой из ранее рассмотренных триггеров.

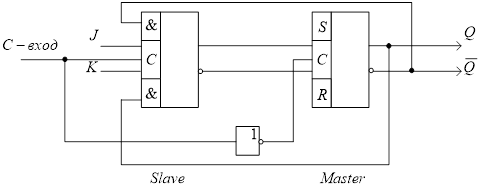

Б) Двухступенчатый J-K-триггер:

Наличие архитектуры Slave – Master указывает на то, что информация на выходе появится только по срезу (или по окончанию) импульса на С-входе (импульс записи).

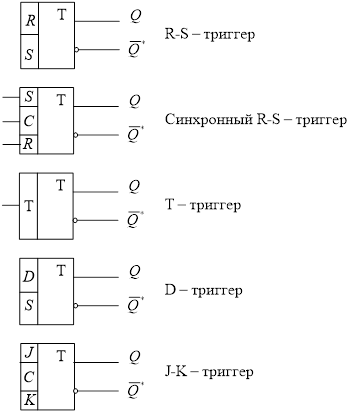

Графические обозначения:

- может отсутствовать.

- может отсутствовать.

§ 3.4 Классификация, назначение регистров

Регистры – это цифровые устройства, предназначенные для хранения нескольких бит информации одновременно. Как правило, количество бит, хранимых в регистрах, кратно четырем. При этом общепринята следующая метрика:

4 бит – тетрада

4 бит – тетрада

8 бит – байт

16 бит – слово

32 бит – двойное слово

64 бит – квадро слово

или х-разрядный регистр.

В зависимости от назначения, все регистры подразделяются:

А) Регистры хранения – предназначены для храненияопределенного количества бит одновременно.

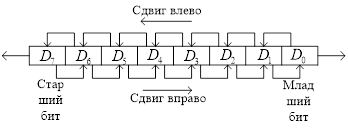

Б) Сдвиговые регистры – предназначены для записи и последующего сдвига информации вправо или влево. При этом термин вправо или влево носит условный характер.

Более точная терминология появилась с изобретением микропроцессора.

Рассмотрим на примере 8-разрядного регистра:

В) Универсальные регистры – предназначены для выполнения одновременно функций сдвигового регистра и регистра хранения.

Регистры являются основой для построения ЛЮБЫХ интеллектуальных устройств (микропроцессоры, микроконтроллеров, конверторов и т.д.), а так же являются оптимальными преобразователями двоичного кода из параллельного формата в последовательный. Основной характеристикой регистра является его информационная емкость или разрядность. Основой для построения регистров служат D-триггеры. Количество D – триггеров и определяет информационную емкость регистра.

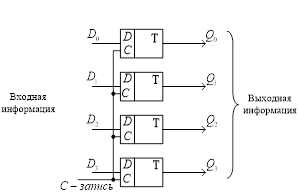

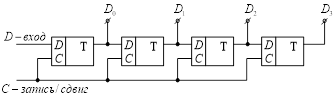

В качестве примера рассмотрим схемотехнику построения 4-разрядных регистров:

А) Регистр хранения:

Как видно из схемотехники, по приходу импульса записи С, информация со входа переписывается в регистр и хранится в нем до поступления следующего импульса записи.

Б) Сдвиговый регистр:

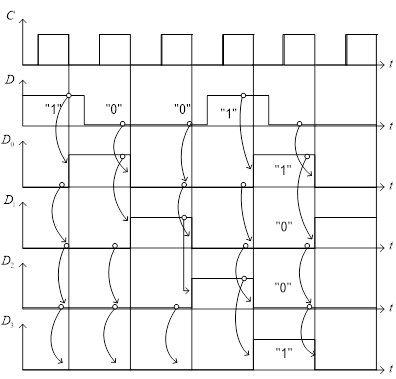

Рассмотрим работу данного устройства на примере временных диаграмм:

Пусть при t = 0 все  . Таким образом, данное устройство действительно выполняет запись и сдвиг информации одновременно. При этом если количество импульсов записи совпадает с разрядностью регистра, то автоматически осуществляется перевод информации из последовательного формата в параллельный.

. Таким образом, данное устройство действительно выполняет запись и сдвиг информации одновременно. При этом если количество импульсов записи совпадает с разрядностью регистра, то автоматически осуществляется перевод информации из последовательного формата в параллельный.

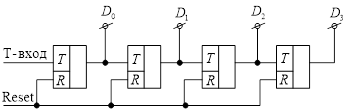

§ 3.5 Классификация, назначение двоичных счетчиков

Счетчики – цифровые устройства, которые предназначены для подсчета количества входных импульсов и выдачи информации об этом количестве в определенном входе.

В зависимости от назначения все счетчики подразделяются:

А) Суммирующие – увеличивают свое состояние на единицу по каждому очередному входному импульсу.

Б) Вычитающие – уменьшают свое состояние на единицу по каждому очередному входному импульсу.

В) Универсальные (или реверсивные) – одновременно могут выполнять функции суммирующего и вычитающего счетчиков.

Основной характеристикой счетчика является его максимальная информационная емкость. Основой для построения счетчиков служат Т-триггеры. Количество Т-триггеров как раз и определяет максимальную информационную емкость, а именно [емкость] =  , где n – количество Т-триггеров. В качестве примера рассмотрим схемотехнику и принцип работы 4-разрядного суммирующего счетчика:

, где n – количество Т-триггеров. В качестве примера рассмотрим схемотехнику и принцип работы 4-разрядного суммирующего счетчика:

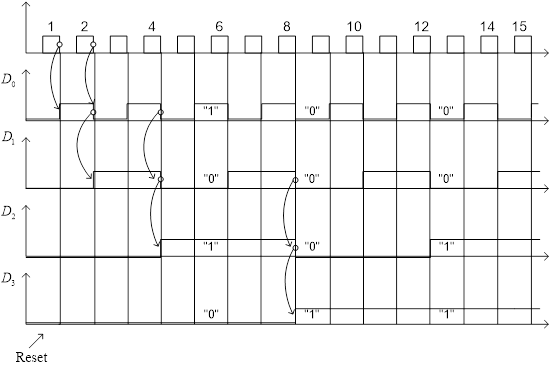

Рассмотрим временные диаграммы:

Сделаем несколько временных срезов: после 5 импульса, после 8 и после 12. Т.е. сколько импульсов поступило, ровно такую информацию, но в двоичном коде, мы снимаем. Как видно из временных диаграмм, действительно, на выходах  в двоичном коде отражается информация о количестве поступивших входных импульсов, т.е. данное устройство осуществляет их подсчет.

в двоичном коде отражается информация о количестве поступивших входных импульсов, т.е. данное устройство осуществляет их подсчет.

Для получения вычитающего счетчика, достаточно выход последующего Т-триггера соединить со входом предыдущего.

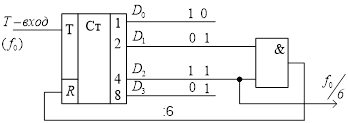

Особый класс представляют счетчики, которые используют в качестве делителей частоты с переменным коэффициентом деления. Типовая схема их включения следующая:

Для построения делителей с произвольным коэффициентом деления необходимо выводы двоичного счетчика, где присутствует единица для двоичного числа делителя, объединить по i, и выход элемента завести на Reset счетчика. Т.о. он просчитает количество периодов, равное коэффициенту деления и сбросится в исходное состояние.

§ 3.6 Назначение, классификация дешифраторов

Дешифратор – это комбинационное устройство, предназначенное для преобразования параллельного двоичного кода в унитарный, т.е. позиционный код. Обычно, указанный в схеме номер вывода дешифратора соответствует десятичному эквиваленту двоичного кода, подаваемого на вход дешифратора в качестве входных переменных, вернее сказать, что при подаче на вход устройства параллельного двоичного кода на выходе дешифратора появится сигнал на том выходе, номер которого соответствует десятичному эквиваленту двоичного кода. Отсюда следует, что в любой момент времени выходной сигнал будет иметь место только на одном выходе дешифратора. В зависимости от типа дешифратора, этот сигнал может иметь как уровень логической единицы (при этом на всех остальных выходах уровень логического 0), так и уровень логического 0 (при этом на всех остальных выходах уровень логической 1).

В дешифраторах каждой выходной функции соответствует только один минтерм, а количество функций определяется количеством разрядов двоичного числа. Если дешифратор реализует все минтермы входных переменных, то он называется полным дешифратором (в качестве примера неполного дешифратора можно привести дешифратор двоично-десятичных чисел).

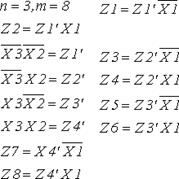

Рассмотрим пример синтеза дешифратора (полного), количество разрядов двоичного числа - 3, количество выходов - 8.

Таблица состояний дешифратора:

Х3 Х2 Х1

0 0 0

0 0 1

0 1 0

0 1 1

1 0 0

1 0 1

1 1 0

1 1 1

Z0 Z1 Z2 Z3 Z4 Z5 Z6 Z7

1 0 0 0 0 0 0 0

0 1 0 0 0 0 0 0

0 0 1 0 0 0 0 0

0 0 0 1 0 0 0 0

0 0 0 0 1 0 0 0

0 0 0 0 0 1 0 0

0 0 0 0 0 0 1 0

0 0 0 0 0 0 0 1

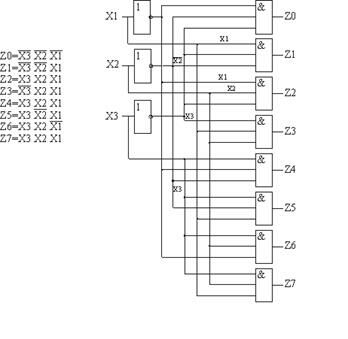

Как следует из таблицы состояния, каждой функции соответствует только один минтерм, следовательно, не требуется минимизировать эти функции (рис. 3.6.1).

Из полученных уравнений и схемы дешифратора следует, что для реализации полного дешифратора на m входов (переменных) потребуются n = 2m элементов конъюнкции (количество входов каждого элемента “И” равно m) и m элементов отрицания.

Пирамидальные дешифраторы. Пирамидальные дешифраторы позволяют реализовать схему на базе только двухвходовых элементов логического умножения (конъюнкции). Рассмотрим пример реализации дешифратора 3-8:

Рис. 3.6.1

Для построения такого дешифратора потребуется 12 двухвходовых элементов 2И и три инвертора. Пирамидальные дешифраторы при больших количествах входных переменных позволяют несколько упростить конструкцию устройства, т.е. уменьшить количество интегральных микросхем.

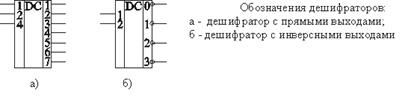

Промышленностью стран СНГ, в том числе и России, выпускаются различные модификации дешифраторов в интегральном исполнении. Обозначение дешифраторов на принципиальных схемах показано на рис. 3.6.2:

Рис. 3.6.2

§ 3.7 Мультиплексоры

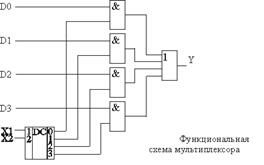

Мультиплексор - коммутатор цифровых сигналов. Мультиплексор представляет собой комбинационное устройство с m информационными, n управляющими входами и одним выходом. Функционально мультиплексор состоит из m элементов конъюнкции, выходы которых объединены дизъюнктивно с помощью элемента ИЛИ с m входами. На одни входы всех элементов конъюнкции подаются информационные сигналы, а другие входы этих элементов соединены с соответствующими выходами дешифратора с n входами.

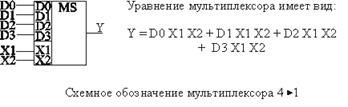

Функциональная схема мультиплексора приведена на рис. 3.7.1:

Рис. 3.7.1

Из рисунка следует, что мультиплексор содержит дешифратор на соответствующее число выходов (число выходов дешифратора определяется числом информационных входов мультиплексора), элементы конъюнкции на два или на три входа каждый и элемент дизъюнкции с числом входов, равным количеству информационных линий D0 . . . Dm. Число входов элементов И может быть равным только двум, однако, во многих случаях возникает необходимость стробирования выходного сигнала мультиплексора импульсами независимого источника. В таких случаях в структуре мультиплексора используются элементы И с тремя входами. Одни из входов всех элементов конъюнкции, в последнем случае, объединяются, и по этой линии подается сигнал разрешения работы мультиплексора (стробирующий сигнал). Наличие дополнительного управляющего входа расширяет функциональные возможности мультиплексора и позволяет проще реализовать методы борьбы с гонками.

Рис. 3.7.2

На рисунке 3.7.2 показано обозначение мультиплексора на принципиальных и функциональных электрических схемах.

Из уравнения мультиплексора видно, что на его выход будет передаваться сигнал только с одного входа, номер которого совпадает с числом, соответствующим кодовой комбинации Х1 и Х2. Если Х1=Х2=0, на выход мультиплексора будет передаваться сигнал с входа D0. Когда на адресных (управляющих) входах Х1=1 и Х2=0, то на выход будет передаваться сигнал с входа D1 и т.д.

Мультиплексоры нашли широкое применение в вычислительной технике в качестве коммутаторов цифровых сигналов. Они используются в компьютерах и микропроцессорных контроллерах для коммутации адресных входов динамических оперативных запоминающих устройств, в узлах объединения или разветвления шин и т.д. На базе мультиплексоров можно построить различные комбинационные устройства с минимальным числом дополнительных элементов логики. Следует отметить, что мультиплексоры хотя, и предназначены для коммутации цифровых сигналов, но с помощью мультиплексоров, изготовленных по КМОП технологии, можно коммутировать и аналоговые сигналы.

§ 3.8 Назначение, классификация сумматоров

Сумматор — логический операционный узел, выполняющий арифметическое сложение кодов двух чисел. При арифметическом сложении выполняются и другие дополнительные операции: учёт знаков чисел, выравнивание порядков слагаемых и тому подобное. Указанные операции выполняются в арифметическо-логических устройствах (АЛУ) или процессорных элементах, ядром которых являются сумматоры.

Сумматоры классифицируют по различным признакам.

В зависимости от системы счисления различают: двоичные; двоично-десятичные (в общем случае двоично-кодированные); десятичные; прочие (например, амплитудные).

По количеству одновременно обрабатываемых разрядов складываемых чисел: одноразрядные, многоразрядные.

По числу входов и выходов одноразрядных двоичных сумматоров: 1) четвертьсумматоры (элементы “сумма по модулю 2”; элементы “исключающее ИЛИ”), характеризующиеся наличием двух входов, на которые подаются два одноразрядных числа, и одним выходом, на котором реализуется их арифметическая сумма; 2) полусумматоры, характеризующиеся наличием двух входов, на которые подаются одноимённые разряды двух чисел, и двух выходов: на одном реализуется арифметическая сумма в данном разряде, а на другом — перенос в следующий (более старший разряд); 3) полные одноразрядные двоичные сумматоры, характеризующиеся наличием трёх входов, на которые подаются одноимённые разряды двух складываемых чисел и перенос из предыдущего (более младшего) разряда, и двумя выходами: на одном реализуется арифметическая сумма в данном разряде, а на другом — перенос в следующий (более старший разряд).

По способу представления и обработки складываемых чисел многоразрядные сумматоры подразделяются на: последовательные, в которых обработка чисел ведётся поочерёдно, разряд за разрядом на одном и том же оборудовании; параллельные, в которых слагаемые складываются одновременно по всем разрядам, и для каждого разряда имеется своё оборудование.

По способу организации межразрядных переносов параллельные сумматоры, реализующие структурные методы, делят на сумматоры: с последовательным переносом;

с параллельным переносом; с групповой структурой; со специальной организацией цепей переноса.

Сумматоры, которые имеют постоянное время, отводимое для суммирования, независимое от значений слагаемых, называют синхронными.

По способу выполнения операции сложения и возможности сохранения результата сложения можно выделить три основных вида сумматоров: комбинационный, выполняющий микрооперацию “S = A плюс B”, в котором результат выдаётся по мере его образования (это комбинационная схема в общепринятом смысле слова); сумматор с сохранением результата “S = A плюс B”; накапливающий, выполняющий микрооперацию “S = S плюс B”.

Последние две структуры строятся либо на счётных триггерах (сейчас практически не используются), либо по структуре “комбинационный сумматор – регистр хранения” (сейчас наиболее употребляемая схема). Важнейшими параметрами сумматоров являются:

разрядность; статические параметры: Uвх, Uвх, Iвх и так далее, то есть обычные параметры интегральных схем; динамические параметры.

Сумматоры характеризуются четырьмя задержками распространения:

от подачи входного переноса до установления всех выходов суммы при постоянном уровне на всех входах слагаемых;

от одновременной подачи всех слагаемых до установления всех выходов суммы при постоянном уровне на входе переноса;

от подачи входного переноса до установления выходного переноса при постоянном уровне на входах слагаемых;

от подачи всех слагаемых до установления выходного переноса при постоянном уровне на входах слагаемых.

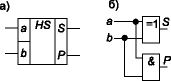

Полусумматор (рис. 3.8.1) имеет два входа a и b для двух слагаемых и два выхода: S — сумма, P — перенос. Обозначением полусумматора служат буквы HS (half sum — полусумма):

Рис. 3.8.1

Работу его отражает таблица истинности, а соответствующие уравнения (1) имеют вид:

| a | b | P | S |

| 0 | 0 | 0 | 0 |

| 0 | 1 | 0 | 1 |

| 1 | 0 | 0 | 1 |

| 1 | 1 | 1 | 0 |

(1)

(1)

Из уравнений (1) следует, что для реализации полусумматора требуется один элемент “исключающее ИЛИ” и один двухвходовый вентиль И (рис. 3.8.1 б).

§ 3.9 Полный сумматор. Многоразрядный сумматор

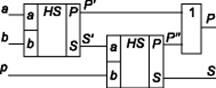

Полный одноразрядный двоичный сумматор (рис. 3.9.1) имеет три входа: a, b — для двух слагаемых и p — для переноса из предыдущего (более младшего) разряда и два выхода: S — сумма, P — перенос в следующий (более старший) разряд. Обозначением полного двоичного сумматора служат буквы SM.

Рис. 3.9.1

Работу его отражает следующая таблица истинности:

| № наб. | a | b | p | P | S |

| 0 | 0 | 0 | 0 | 0 | 0 |

| 1 | 0 | 0 | 1 | 0 | 1 |

| 2 | 0 | 1 | 0 | 0 | 1 |

| 3 | 0 | 1 | 1 | 1 | 0 |

| 4 | 1 | 0 | 0 | 0 | 1 |

| 5 | 1 | 0 | 1 | 1 | 0 |

| 6 | 1 | 1 | 0 | 1 | 0 |

| 7 | 1 | 1 | 1 | 1 | 1 |

Отметим один момент: в таблице выходные сигналы P и S не случайно расположены именно в такой последовательности. Это подчеркивает, что PS рассматривается как двухразрядное двоичное число, например, 1 + 1 = 210 = 102 , то есть P = 1, а S = 0 или 1 + 1 + 1 = 310 = 112, то есть P = 1, а S = 1. Уравнения, описывающие работу полного двоичного сумматора, представленные в совершенной дизъюнктивной нормальной форме (СДНФ), имеют вид:

(1)

(1)

Уравнение для переноса может быть минимизировано:

P = ab + ap + bp. (2)

При практическом проектировании сумматора уравнения (1) и (2) могут быть преобразованы к виду, удобному для реализации на заданных логических элементах с некоторыми ограничениями (по числу логических входов и др.) и удовлетворяющему предъявляемым к сумматору требованиям по быстродействию.

Например, преобразуем уравнения (1) следующим образом:

(3)

(3)

Из выражений (3) следует, что полный двоичный сумматор может быть реализован на двух полусумматорах и одном двухвходовом элементе ИЛИ. Соответствующая схема приведена на рис. 3.9.2:

Цвет и шрифты - лекция, которая пользуется популярностью у тех, кто читал эту лекцию.

Рис. 3.9.2

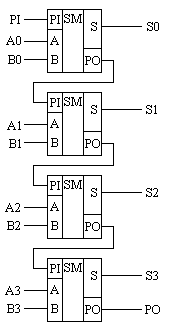

Для того чтобы получить многоразрядный сумматор, достаточно соединить входы и выходы переносов соответствующих двоичных разрядов. Схема соединения одноразрядных сумматоров для реализации четырехразрядного сумматора приведена на рисунке 3.9.3:

Рис. 3.9.3

Одноразрядные сумматоры практически никогда не использовались, так как почти сразу же были выпущены микросхемы многоразрядных сумматоров. Полный двоичный четырехразрядный сумматор изображается на схемах как показано на рисунке 3.9.4:

Рис. 3.9.4

Рис. 3.9.4