Цифровые запоминающие устройства

Лекция 17. Цифровые запоминающие устройства

Основные понятия и виды запоминающих устройств. Цифровые запоминающие устройства предназначены для записи, хранения и выдачи информации, представленной в виде цифрового кода. Основными характеристиками запоминающих устройств являются: их информационная емкость, быстродействие и время хранения информации.

Классификацию цифровых запоминающих устройств можно выполнять по ряду признаков.

• функциональному назначению;

• способу хранения информации;

• технологическому исполнению;

• способу обращения к массиву элементов памяти.

В основу технической классификации запоминающих устройств (ЗУ) положено их функциональное назначение. По функциональному назначению все виды ЗУ можно разделить на следующие группы:

• оперативные запоминающие устройства (ОЗУ, или RAM) — устройства памяти цифровой информации, объединенные со схемами управления, обеспечивающими режимы записи, хранения и считывания цифровой (двоичной) информации в процессе ее обработки;

Рекомендуемые материалы

• постоянные запоминающие устройства (ПЗУ, или ROM) — матрицы пассивных элементов памяти со схемами управления, предназначенные для воспроизведения неизменной информации, заносимой в матрицу при изготовлении ( в режиме хранения информации энергия не потребляется);

• программируемые постоянные запоминающие устройства (ППЗУ, или PROM) — постоянные запоминающие устройства с возможностью однократного электрического программирования; они отличаются от ПЗУ тем, что позволяют в процессе применения микросхемы однократно изменить состояние запоминающей матрицы электрическим путем по заданной программе;

• репрограммируемые постоянные запоминающие устройства (РПЗУ, или EEPROM) — постоянные запоминающие устройства с возможностью многократного электрического перепрограммирования; они отличаются от ППЗУ тем, что допускают многократную электрическую запись информации, но число циклов записи и стирания ограничено (до 104 циклов);

• репрограммируемые постоянные запоминающие устройства с ультрафиолетовым стиранием и электрической записью информации (РПЗУ УФ, или EPROM); они отличаются от РПЗУ только способом стирания информации с помощью ультрафиолетового освещения, для чего в корпусе микросхемы имеется специальное окно;

• ассоциативные запоминающие устройства (АЗУ, или САМ) — «безадресные» ЗУ, в которых поиск и выборка информации осуществляется по содержанию произвольного количества разрядов хранящихся в АЗУ чисел, независимо от физических координат ячеек памяти. Перечисленный ряд запоминающих устройств не является исчерпывающим. Эта область электроники в настоящее время бурно развивается и появляются новые разновидности ЗУ с иными принципами функционирования. Например, имеются программируемые логические матрицы (ПЛМ), отличающиеся от ППЗУ ограниченным набором входных сигналов. Также имеются РПЗУ, в которых допускается избирательное стирание информации в любом отдельном элементе памяти (EAROM).

По способу хранения информации ЗУ делятся на статические и динамические. Элементы памяти статических ЗУ представляют собой бистабильные ячейки, что определяет потенциальный характер управляющих сигналов и возможность чтения информации без ее разрушения.

В динамических ЗУаля хранения информации используются инерционные свойства реактивных элементов (например, конденсаторов), что требует периодического восстановления (регенерации) состояния элементов памяти в процессе хранения информации. В большинстве динамических ЗУ регенерация совмещается с обращением к элементам памяти. Для обеспечения синхронизации работы динамических ЗУ используются потенциально-импульсные сигналы управления.

Некоторые типы динамических ЗУ имеют встроенную систему регенерации и синхронизации. По внешним сигналам управления они не отличаются от полностью статических ЗУ и поэтому их часто называют квазистатическими ЗУ.

Статические ЗУ бывают синхронными и асинхронными. Синхронные статические ЗУ имеют статический накопитель (матрицу элементов памяти) и динамические цепи управления, требующие синхронизации, аналогично динамическим ЗУ.

По технологии выполнения ЗУ можно разделить на следующие виды:

• полупроводниковые ЗУ на основе биполярных структур, использующие схе-мотехнику ТТЛ, ЭСЛ и др.;

• полупроводниковые ЗУ на основе полевых транзисторов с изолированным затвором: р-МОП, и-МОП и КМОП;

• полупроводниковые ЗУ на основе приборов с зарядовой связью;

• магнитные ЗУ на основе цилиндрических магнитных доменов. Следует отметить, что» независимо от технологии изготовления ЗУ уровни их входных и выходных сигналов обычно приводятся к уровням стандартных серий элементов ТТЛ, ЭСЛ или КМОП. Для использования в РПЗУ разработаны специальные структуры:

« с лавинной инжекцией заряда и плавающим затвором (ЛИПЗ МОП), которые применяются в РПЗУ УФ;

• со структурой металл — нитрид кремния — окисел кремния — полупроводник (МНОП), которые используются в РПЗУ с электрическим стиранием, в том числе и с избирательным стиранием.

По способу обращения к массиву памяти все ЗУ делятся на адресные и безадресные (ассоциативные). Большинство видов ЗУ относятся к адресным ЗУ, в которых обращение к элементам памяти производится по их физическим координатам, задаваемым внешним двоичным кодом-адресом. Адресные ЗУ бывают следующих типов:

• с произвольным обращением, которые допускают любой порядок следования адресов;

• с последовательным обращением, в которых выборка элементов пямяти возможна только в порядке возрастания или убывания адресов (обычно такие ЗУ выполняются на регистрах сдвига).

Ассоциативные ЗУ не имеют входов адресных сигналов: поиск и выборка информации в таких ЗУ осуществляется по ее содержанию и не зависит от физических координат элементов памяти.

Основные электрические параметры ЗУ. Все параметры ЗУ можно разделить на статические и динамические. Статические параметры ЗУ характеризуют его работу в установившемся режиме. Система статических параметров ЗУ представляет собой совокупность некоторых контрольных точек его вольт-амперных характеристик. Динамические параметры ЗУ определяются происходящими в нем временньши процессами Систему динамических параметров ЗУ составляет совокупность временных переходов входных и выходных сигналов, соответствующих границам правильного функционирования ЗУ

Кроме этого используются также специальные классификационные параметры ЗУ, по которым выполняют их разделение по группам в соответствующих сериях ИМС ЗУ. В качестве классификационных параметров могут использоваться также некоторые статические и динамические параметры. В табл. 17.1 приведены основные классификационные параметры ЗУ

Статические параметры ЗУ можно разделить на общие, входные и выходные. В табл. 17.2 приведены некоторые статические параметры ЗУ. К динамическим параметрам относятся основные временные характеристики ЗУ, такие как время выбора микросхемы tcs, время выбора адреса 1д, время выборки сигнала г^д и некоторые другие

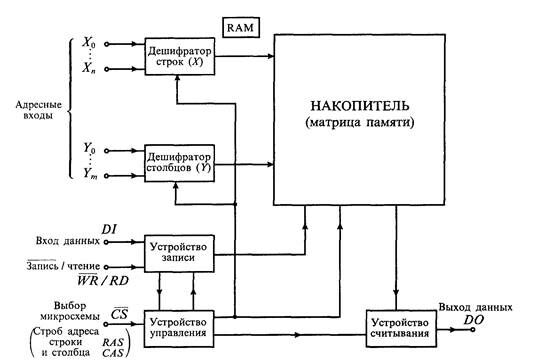

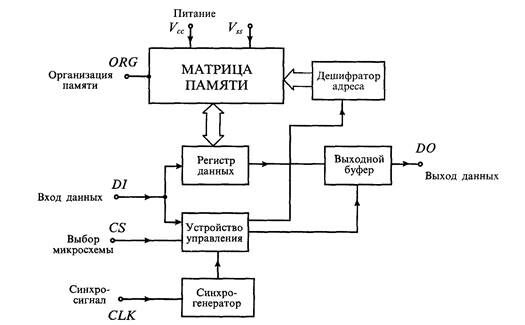

Статические ОЗУ. Структурная схема статического ОЗУ приведена на рис. 17 1 Основой статического ОЗУ является накопитель или матрица памяти, состоящая из отдельных запоминающих (бистабильных) ячеек. Обычно в качестве этих ячеек используются различного рода триггеры Двоичная информация, записанная в такую ячейку, может сохраняться в этой ячейке до тех пор, пока не будет заменена другой или не будет снято напряжение питания

Таблица 17 1 Основные классификационные параметры ЗУ

| Параметр | Обозначение | Определение |

| Информационная емкость | N | Число бит памяти в накопителе ЗУ |

| Число слов в ЗУ | п | Число адресов слов в накопителе ЗУ |

| Разрядность | т | Число разрядов в накопителе ЗУ |

| Коэффициент разветвления по выходу | К i> | Число единичных нагрузок (входов других ИМС), которые можно одновременно подключить к выходу ЗУ |

| Число циклов перепрограммирования | ncy | Число циклов запись-стирание, при котором сохраняется работоспособность ЗУ |

| Потребляемая мощность | рос | Потребляемая ЗУ мощность в установленном режиме работы |

| Потребляемая мощность в режиме хранения | pccs | Мощность, потребляемая ЗУ при хранении информации в режиме невыбора |

| Время хранения информации | 1^ | Интервал времени, в течение которого ЗУ в заданном режиме сохраняет информацию |

Таблица 17 2 Статические параметры ЗУ

| Параметр | Обозначение | Определение |

| Напряжение питания | Ucc | Напряжение источника питания ЗУ |

| Ток потребления | ^с | Ток, потребляемый ЗУ от источника питания в заданном режиме |

| Напряжение питания в режиме хранения | Uccs | Напряжение питания ЗУ в режиме хранения информации |

| Ток потребления в режиме хранения | 'ccs | Ток, потребляемый ЗУ в режиме хранения информации |

| Напряжение логической «I» | и„ | Напряжение сигнала на входе или на выходе, соответствующее логической единице |

| Напряжение логического «О» | ^ | Напряжение сигнала на входе или на выходе, соответствующее логическому нулю |

Рис 17.1. Структурная схема статического ОЗУ

При использовании такого накопителя приходится решать две задачи.

• выбор конкретной ячейки накопителя, в которую будет записана или из которой будет считана информация;

• что нужно сделать — записать или прочитать информацию в ячейке.

Первая задача решается с помощью адресации всех ячеек накопителя. Вторая задача решается переводом ячейки памяти в режим записи или считывания по сигналу на входе схемы управления.

Накопитель или матрица памяти состоит из п строк. В состав каждой строки входят m запоминающих ячеек, образующих w-разрядное слово. Информационная емкость накопителя равна N'=nm, где п — число строк (или слов), т — число столбцов (или разрядов). Соответствующие шины в накопителе управляются от дешифраторов строк (X) и столбцов (У), на входы которых поступают адресные сигналы Ay ..Ац. При записи и считывании осуществляется обращение (выборка) к одной или нескольким запоминающим ячейкам одновременно. Дешифраторы строк и столбцов выполняют выбор требуемых ячеек памяти с помощью адресных сигналов ао -Уп и Ко... К„

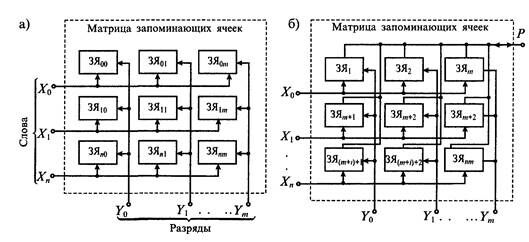

Такая матрица запоминающих ячеек (ЗЯ) может работать в двух режимах пословном и двухкоординатном Структура пословной матрицы приведена на рис 17 2 а. Как видно из схемы, адресные шины Хц...Хп электрически связаны с каждой ЗЯ одного слова, в то время как рязрядные шины Yy Уд, имеют связь с ЗЯ одноименного разряда всех слов. При наличии в адресной шине X, сигнала выбора ;-го слова, соответствующего высокому уровню, состояние каждой ячейки в этом слове может быть считано по разрядным шинам Yy Y^,. Если необходимо записать информацию по выбранному адресу Х„ то на разрядные шины Уо Ym подаются соответствующие электрические сигналы, которые подводятся ко всем ЗЯ 1-й. строки (слова).

Рис 17.2 Структура матриц запоминающих ячеек при пословной (а) и двухкоординатнои (б) организации

При работе матрицы ЗЯ в двухкоординатном режиме с помощью шин строк и столбцов выбирается любая ячейка матрицы. В этом случае разрядная шина Р, которая является общей для всех ЗЯ, используется как для записи, так и для считывания информации в адресованных ЗЯ.

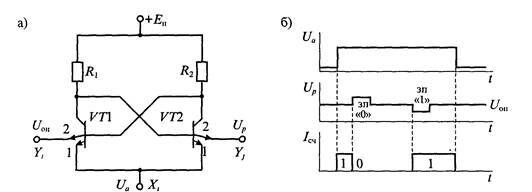

Простейшей ЗЯ является схема ^-триггера, построенная на двух многоэмит-терных биполярных транзисторах VT и VT2, изображенная на рис. 17.3 а. Первые эмиттеры обоих транзисторов соединены с адресной шиной Х„ потенциал которой U„ в установившемся состоянии должен быть самым низким. Вторые эмиттеры этих транзисторов присоединены к разрядным шинам Y, и У,. На разрядной шине У, установлено опорное напряжение С/оп, а на шину У, подается напряжение Up. Режим работы схемы зависит от соотношения между напряжениями ^о,„ V, и U,.

В режиме хранения информации выполняется условие Ua<Uo„=Up. В этом случае схема находится в одном из устойчивых состояний, при котором открытым может быть транзистор VT2 или VT. Ток протекает по первому эмиттеру открытого транзистора, а вторые эмиттеры обесточены. Например, если в триггер записана логическая 1, то транзистор VT2 открыт, а транзистор VT закрыт. В этом случае за логическую единицу принимается наличие тока в транзисторе VT2.

В режиме считывания с помощью адресного сигнала X, на шине устанавливается напряжение U^Uoa^-Up. Если в триггер записана логическая 1, то ток открытого транзистора VT2 потечет в разрядную шину У,. Наличие тока в разрядной шине соответствует считыванию 1, а его отсутствие соответствует логическому 0.

Условия режима записи зависят от состояния, в которое необходимо установить ЗЯ. Если триггер находился в состоянии 1 (транзистор VT2 открыт, транзистор VT — закрыт), то для записи 0 необходимо по разрядной шине У, подать напряжение Up> t/o„, сохраняя условие [/д> Up. При этом триггер перейдет в новое состояние, при котором транзистор VT2 закроется, а транзистор VT откроется. Для записи в ЗЯ логической 1 на шину Y, следует подать напряжения Up<U^ и обеспечить условие {/„> Uy„. Временные диаграммы работы ЗЯ в режимах записи логического нуля или единицы приведены на рис. 17.3 б.

Рис. 17.3. Схема запоминающей ячейки на многоэмиттерных биполярных транзисторах (а) и графики ее работы в режиме записи (б)

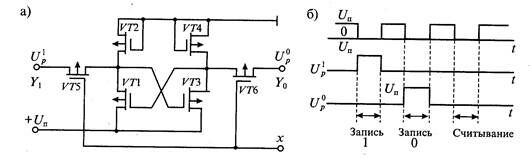

Запомнающая ячейка на /?5'-триггере, выполненном на ^-канальных МОП транзисторах, приведена на рис. 17.4 а. Триггер образован транзисторами VT,..., УТ4. Переключение триггера для записи и считывания выполняется транзисторами VT5 и VT6. Временные диаграммы работы триггера изображены на рис. 17.46.

В исходном состоянии напряжения на разрядных шинах U], и U°p равны нулю, а на шине слова Х установлено напряжение питания £n. При этом транзисторы VT5 и VT6 закрыты, так как напряжение между затворами и истоками меньше порогового напряжения, и триггер находится в одном из устойчивых состояний, например, транзистор VTb открыт, а транзистор VT закрыт.

Для записи логической 1 в ЗЯ на шину слова подается отрицательный сигнал, изменяющий напряжение в ней до нуля. Одновременно в разрядную шину Y подается положительный сигнал, изменяющий напряжение в ней до напряжения питания Uy. При этом транзистор VT5 открывается и положительный сигнал подается на затвор VT3, запирая его. После запирания транзистора VT3 отпирается транзистор VT и на его стоке устанавливается положительное напряжение, что соответствует состоянию логической 1.

Для записи логического нуля в ЗЯ на шине слова устанавливается нулевое напряжение, а напряжение питания подается на разрядную шину Yy. При этом транзистор VT6 открывается и положительное напряжение через него подается на затвор VTI, запирая его, что приводит к отпиранию транзистора VT3.

Для считывания информации, записанной в ЗЯ, нужно подать отрицательный сигнал только на шину слова, изменив в ней напряжение до нуля. При этом оба транзистора VT5 и VT6 открываются и через транзистор, подключенный к триггеру с положительным напряжением, протекает ток, поступающий в соответствующую разрядную шину.

Устройство управления определяет режим работы схемы ОЗУ. По сигналу CS разрешаются или запрещаются операции записи и считывания. Сигнал CS позволяет выбрать требуемую микросхему памяти в ЗУ, состоящем из ряда микросхем. Подача сигнала на вход WR/RD при наличии сигнала CS=0 выбора микросхемы позволяет выбрать режим записи, если WR/RD = 0, или считывания, если WR/RD=.

Рис. 17.4. Схема запоминающей ячейки на ^-канальных МОП транзисторах (а) и графики ее работы (б) Запомнающая ячейка на /?5'-триггере, выполненном на ^-канальных МОП транзисторах, приведена на рис. 17.4 а. Триггер образован транзисторами VT,..., УТ4. Переключение триггера для записи и считывания выполняется транзисторами VT5 и VT6. Временные диаграммы работы триггера изображены на рис. 17.46.

В исходном состоянии напряжения на разрядных шинах U], и U°p равны нулю, а на шине слова Х установлено напряжение питания £n. При этом транзисторы VT5 и VT6 закрыты, так как напряжение между затворами и истоками меньше порогового напряжения, и триггер находится в одном из устойчивых состояний, например, транзистор VTb открыт, а транзистор VT закрыт.

Для записи логической 1 в ЗЯ на шину слова подается отрицательный сигнал, изменяющий напряжение в ней до нуля. Одновременно в разрядную шину Y подается положительный сигнал, изменяющий напряжение в ней до напряжения питания Uy. При этом транзистор VT5 открывается и положительный сигнал подается на затвор VT3, запирая его. После запирания транзистора VT3 отпирается транзистор VT и на его стоке устанавливается положительное напряжение, что соответствует состоянию логической 1.

Для записи логического нуля в ЗЯ на шине слова устанавливается нулевое напряжение, а напряжение питания подается на разрядную шину Yy. При этом транзистор VT6 открывается и положительное напряжение через него подается на затвор VTI, запирая его, что приводит к отпиранию транзистора VT3.

Для считывания информации, записанной в ЗЯ, нужно подать отрицательный сигнал только на шину слова, изменив в ней напряжение до нуля. При этом оба транзистора VT5 и VT6 открываются и через транзистор, подключенный к триггеру с положительным напряжением, протекает ток, поступающий в соответствующую разрядную шину.

Устройство управления определяет режим работы схемы ОЗУ. По сигналу CS разрешаются или запрещаются операции записи и считывания. Сигнал CS позволяет выбрать требуемую микросхему памяти в ЗУ, состоящем из ряда микросхем. Подача сигнала на вход WR/RD при наличии сигнала CS=0 выбора микросхемы позволяет выбрать режим записи, если WR/RD = 0, или считывания, если WR/RD=.

Рис. 17.4. Схема запоминающей ячейки на ^-канальных МОП транзисторах (а) и графики ее работы (б)

Данные, подлежащие записи, поступают на вход DI, а данные, подлежащие чтению, снимаются с выхода DO. Устройства записи и считывания обеспечивают прием и выдачу сигналов информации с уровнями, согласующимися с серийными цифровыми микросхемами

По режиму питания статические ОЗУ можно разделить на группы с активным и активно-пассивным режимами питания. При активном режиме питания накопитель и схема управления потребляют практически одинаковую мощность при всех операциях- записи, считывания и хранения информации. При активно-пассивном режиме питания некоторые узлы переходят в режим малого потребления или полностью отключаются, если микросхема находится в режиме хранения информации. В результате при хранении информации потребляемая микросхемой мощность уменьшается. При переходе в режим записи или считывания напряжения и токи питания восстанавливаются до номинальных значений. Использование активно-пассивного режима питания в несколько раз уменьшает среднюю мощность, потребляемую микросхемой. По этой причине большинство микросхем ОЗУ используют такой режим.

Динамические ОЗУ. Для увеличения информационной емкости широко используются динамические ОЗУ, в кото'рых информация хранится в виде заряда соответствующих емкостей. При токе утечки обратно смещенного ^-«-перехода около 10'° А и емкости хранения 0,1пФ время хранения не превышает 1мс. В связи с этим необходимо восстановление (регенерация)хранимой информации с периодом не более 1 мс. Емкостные ячейки памяти выполняются или на биполярных, или на МОП транзисторах.

Для динамических ОЗУ характерны некоторые особенности, которые существенно отличают их от статических: динамические ЗЯ не требуют источника питания, для выполнения регенерации заряда необходимы соответствующие блоки, малая потребляемая мощность; для управления динамическим ОЗУ необходимы последовательности импульсов, которые обычно формируются специальными генераторами.

По способу регенерации микросхемы динамических ОЗУ делятся на адресные и безадресные При адресной регенерации производится перебор регенерируемых ячеек с тем, чтобы за период регенерации восстановить заряды во всех ячейках. При безадресной регенерации заряды восстанавливаются во всех ячейках при помощи специальных тактовых импульсов.

Отличительной особенностью микросхем динамических ОЗУ является их адресация. Схемы динамических ОЗУ отличаются от схем статических ОЗУ использованием последовательной адресации. Вначале на адресный вход подается строб адреса строки RAS, а затем строб адреса столбца CAS. Для этих стробов имеются специальные выводы микросхемы, которые показаны на структурной схеме рис. 17 1. Адресные сигналы поступают в регистры-фиксаторы, а затем на дешифраторы адресов.

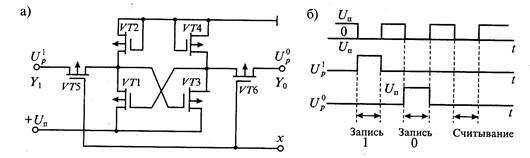

Устройство типовой ячейки памяти динамического ОЗУ приведено на рис. 17 5 Хранение информации происходит в емкости Сед (затвор — исток) полевого транзистора, а транзистор VTI выполняет роль ключа выборки. Сохранность информации при выборке и хранении обеспечивается при помощи Данные, подлежащие записи, поступают на вход DI, а данные, подлежащие чтению, снимаются с выхода DO. Устройства записи и считывания обеспечивают прием и выдачу сигналов информации с уровнями, согласующимися с серийными цифровыми микросхемами

По режиму питания статические ОЗУ можно разделить на группы с активным и активно-пассивным режимами питания. При активном режиме питания накопитель и схема управления потребляют практически одинаковую мощность при всех операциях- записи, считывания и хранения информации. При активно-пассивном режиме питания некоторые узлы переходят в режим малого потребления или полностью отключаются, если микросхема находится в режиме хранения информации. В результате при хранении информации потребляемая микросхемой мощность уменьшается. При переходе в режим записи или считывания напряжения и токи питания восстанавливаются до номинальных значений. Использование активно-пассивного режима питания в несколько раз уменьшает среднюю мощность, потребляемую микросхемой. По этой причине большинство микросхем ОЗУ используют такой режим.

Динамические ОЗУ. Для увеличения информационной емкости широко используются динамические ОЗУ, в кото'рых информация хранится в виде заряда соответствующих емкостей. При токе утечки обратно смещенного ^-«-перехода около 10'° А и емкости хранения 0,1пФ время хранения не превышает 1мс. В связи с этим необходимо восстановление (регенерация)хранимой информации с периодом не более 1 мс. Емкостные ячейки памяти выполняются или на биполярных, или на МОП транзисторах.

Для динамических ОЗУ характерны некоторые особенности, которые существенно отличают их от статических: динамические ЗЯ не требуют источника питания, для выполнения регенерации заряда необходимы соответствующие блоки, малая потребляемая мощность; для управления динамическим ОЗУ необходимы последовательности импульсов, которые обычно формируются специальными генераторами.

По способу регенерации микросхемы динамических ОЗУ делятся на адресные и безадресные При адресной регенерации производится перебор регенерируемых ячеек с тем, чтобы за период регенерации восстановить заряды во всех ячейках. При безадресной регенерации заряды восстанавливаются во всех ячейках при помощи специальных тактовых импульсов.

Отличительной особенностью микросхем динамических ОЗУ является их адресация. Схемы динамических ОЗУ отличаются от схем статических ОЗУ использованием последовательной адресации. Вначале на адресный вход подается строб адреса строки RAS, а затем строб адреса столбца CAS. Для этих стробов имеются специальные выводы микросхемы, которые показаны на структурной схеме рис. 17 1. Адресные сигналы поступают в регистры-фиксаторы, а затем на дешифраторы адресов.

Устройство типовой ячейки памяти динамического ОЗУ приведено на рис. 17 5 Хранение информации происходит в емкости Сед (затвор — исток) полевого транзистора, а транзистор VTI выполняет роль ключа выборки. Сохранность информации при выборке и хранении обеспечивается при помощи

усилителя-регенератора. Режим хранения обеспечивается периодической регенерацией заряда емкости Cos с частотой около сотни герц. В процессе регенерации уменьшение заряда на емкости Cgs компенсируется усилителем регенератором.

Рис. 17.5. Запоминающая ячейка динамического ОЗУ

Динамические ОЗУ имеют малую потребляемую мощность (50... 500 мВт) при увеличении информационной емкости по сравнению со статическим ОЗУ почти на порядок. Это объясняется тем, что для хранения информации почти не потребляется энергия, и все структу-

t ----- -——-д---———, —— __»» ~-^J^»»J-

ры работают в импульсном (ключевом) режиме.

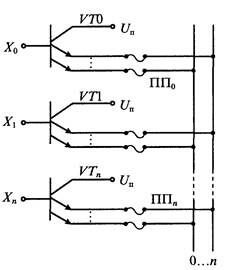

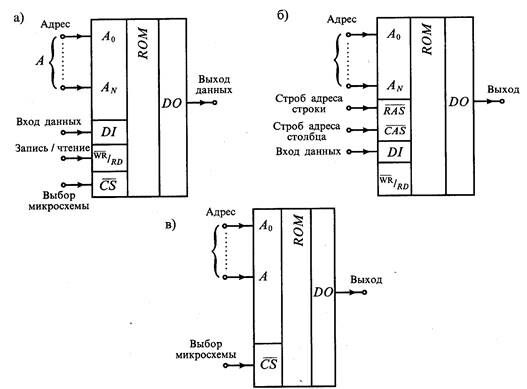

Постоянные запоминающие устройства. Микросхемы ПЗУ можно разделить на две группы: однократно программируемые и перепрограммируемые. В первом типе ПЗУ информация после записи меняться не может, и микросхема работает только в режиме считывания. Структурная схема ПЗУ приведена на рис. 17.6. От схемы ОЗУ, приведенной на рис. 17.1, эта схема отличается отсутствием устройства записи и линий, которые его обслуживают. Кроме того, изменяется выполнение накопителя (матрицы памяти). В настоящее время находят применение два типа накопителей ПЗУ: масочньге и программируемые.

Рис. 17.6 Структурная схема постоянного запоминающего устройства

В масочных ПЗУ (МПЗУ) накопитель программируется на стадии изготовления, когда информация, записываемая в него, определяется построением одного из слоев схемы при помощи специального фотошаблона.

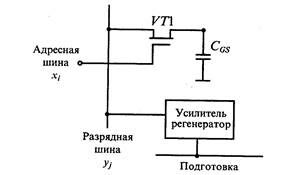

В программируемых ПЗУ (ППЗУ) накопитель выполняют на базе ЗЯ с плавкими перемычками; их упрощенная схема приведена на рис. 17.7. При программировании эти плавкие перемычки пережигают с помощью специального программирующего устройства. Сами плавкие перемычки изготовляют из нихрома или других тугоплавких материалов и защищают специальным диэлектриком, обеспечивающим надежность в условиях повышенной влажности. Процесс записи информации в схему представляет собой избирательное разрушение плавких перемычек током, обеспечиваемым устройством-программирования. На рис. 17.7 плавкие перемычки ПП показаны в виде предохранителей, включенных в эмиттеры многоэмиттерных транзисторов VTy...VTn. Программируемые элементы включены между эмиттерами транзисторов матриц и разрядными шинами. Наличие перемычки соответствует логическому 0 на выходе усилителя считывания, а отсутствие перемычки — логической единице. Пережигание перемычек в режиме программирования выполняется серией импульсов по специальной программе.

Для повышения надежности работы ПЗУ методика программирования предусматривает подачу серии 40... 100 импульсов после фиксации момента пережигания перемычки, а также обязательную термотренировку запрограммированного ПЗУ при определенной температуре (около 100°С) в заданном электрическом режиме.

Репрограммируемые ПЗУ (РПЗУ). Репрограммируемые ПЗУ делятся на две группы: 1) с электрическим программированием и ультрафиолетовым стиранием EPROM; 2) с электрическим программированием и электрическим стиранием EEPROM. К последней группе также относятся РПЗУ с избирательным стиранием EAROM.

Запоминающие ячейки РПЗУ строятся на п-МОП или КМОП транзисторах. Для построения ЗЯ используются различные физические явления хранения заряда на границе между двумя различными диэлектрическими средами или проводящей и диэлектрической средой.

В первом случае диэлектрик под затвором МОП транзистора делают из двух слоев: из нитрида кремния и двуокиси кремния. Такая структура называется МНОП: металл — нитрид кремния —окисел — полупроводник. В такой структуре при высоком напряжении на затворе (около 30 В) происходит туннельное перемещение носителей заряда через слой двуокиси кремния, который делается очень тонким (до 10 нм), к границе двух диэлектриков, вблизи которой имеется много ловушек

Рис. 17 7. Схема ячейки ПЗУ с плавкими перемычками

Рис. 17 8 Структурная схема ПЗУ с электрическим программированием

для носителей заряда. В результате внутри МОП структуры образуется некоторый заряженный слой, который приводит к изменению порогового напряжения МОП транзистора. При постоянном напряжении на затворе в режиме считывания информации это приводит к изменению тока считывания.

Во втором случае затвор МОП транзистора делают плавающим, т е. не связанным с другими элементами схемы Такой затвор заряжается током лавинной инжекции при подаче на сток транзистора высокого напряжения (также около ЗОВ). В результате плавающий затвор начинает влиять на ток стока, что и используется при считывании информации. Такие РПЗУ обычно называют выполненными по структуре ЛИПЗ (лавинно-инжекционные с плавающим затвором).

Поскольку затвор транзистора со всех сторон окружен изолирующим слоем, ток утечки очень мал и хранение информации достаточно длительное (десятки лет). Для стирания информации в таких приборах пользуются облучением кристалла через специальное прозрачное окно в корпусе микросхемы ультрафиолетовым светом. Облучение ультрафиолетовыми лучами приводит к резкому увеличению тока утечки, что способствует рассасыванию носителей заряда. Такие микросхемы получили название РПЗУ УФ или EPROM

"3 Основы синтеза цифровых устройств" - тут тоже много полезного для Вас.

Другой способ перезаписи информации используется в РПЗУ с электрическим программированием. Он основан на размещении над плавающим затвором второго — управляющего — затвора. Подача напряжения на управляющий затвор приводит к рассасыванию заряда за счет туннельного эффекта. Эти РПЗУ называются EEPROM и имеют несомненные преимущества перед РПЗУ УФ, так как

Рис. 17.9. Условные схематичные изображения статического ОЗУ (а), динамического ОЗУ (б) и ПЗУ (в)

не требуют при перепрограммировании специальных источников ультрафиолетового света. Структурная схема такого РПЗУ с шинным управлением приведена на рис. 17.8.

Интегральные микросхемы ЗУ. Промышленность выпускает большое количество различных микросхем ЗУ, отличающихся информационной емкостью, организацией, технологией изготовления. Условное схематичное изображение микросхемы статического ОЗУ приведено на рис. 17.9 а. Функциональное назначение ИМС указывается обозначением RAM.

Отдельные типы микросхем ОЗУ могут иметь выходные каскады с тремя состояниями или с открытым коллектором. Для обозначения выхода с тремя со-стояниями используется знак ^. Микросхемы, имеющие выход с открытым коллектором, обозначаются индексом <С>, а с открытым эмиттером — знаком <^. Применение микросхем с тремя состояниями выхода или с открытым коллектором (открытым эмиттером) позволяет создавать модули ЗУ с различными параметрами.

Условные схематичные изображения динамического ОЗУ и ПЗУ приведены на рис. 17.9 б и в. Раздел 4 ЛИНЕЙНЫЕ ЭЛЕКТРОННЫЕ УСТРОЙСТВА