Типовые функциональные узлы комбинационных логических устройств

3. Типовые функциональные узлы комбинационных логических устройств.

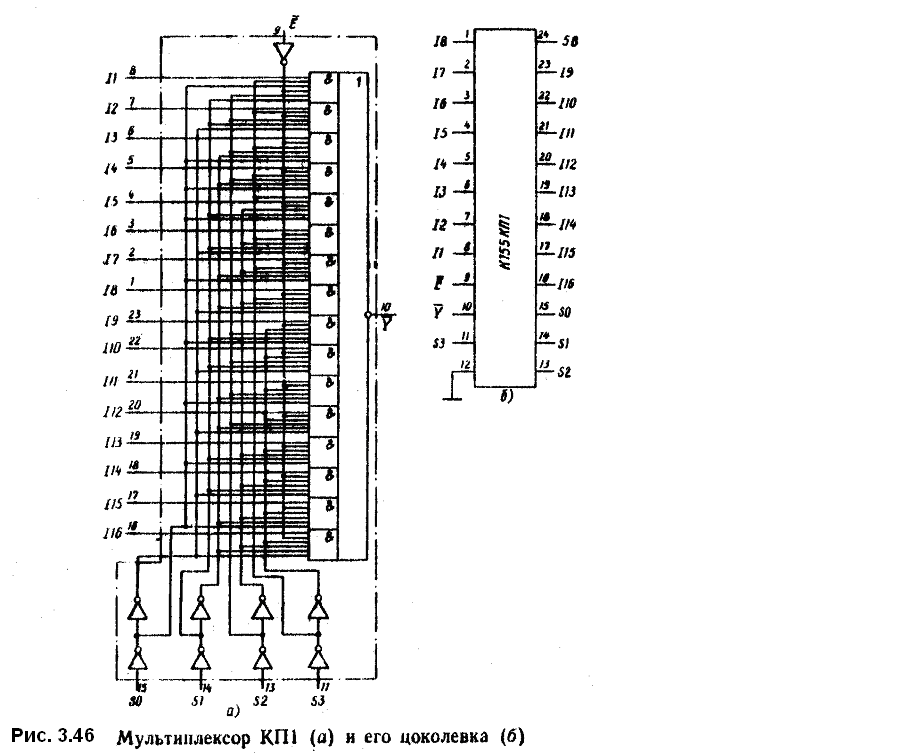

3.1 Мультиплексоры.

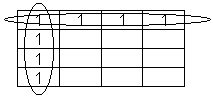

Мультиплексором называется комбинационное логическое устройство, предназначенное для управляемой передачи данных от нескольких источников информации в один выходной канал.

D0

D0

Мультиплексор имеет один выход и две

группы входов: информационные и адресные.

D1 А0,А1

D1 А0,А1

входы Q

входы Q

Рекомендуемые материалы

D2

D2

Выход Рис. 3.1

Выход Рис. 3.1

D3

D3

Код подаваемый на адресные входы определяет, какой из информационных входов в данный момент подключен к выходному выводу.

Поскольку n-разрядный двоичный код может принимать 2n значений, то, если число адресных входов мультиплексора равно n, число его информационных входов должно равняться 2n.

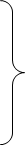

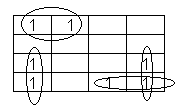

Рис 3.2 Мультиплексор

Q=D0

+D1

+D1 A0+D2A1

A0+D2A1 +D3A1A0

+D3A1A0

Таблица 3.1

| A1 | A0 | Q |

| 0 | 0 | D0 |

| 0 | 1 | D1 |

| 1 | 0 | D2 |

| 1 | 1 | D3 |

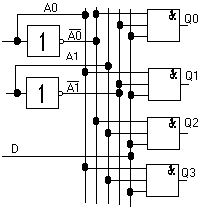

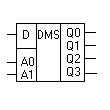

3.2 Демультиплексоры

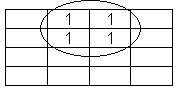

Демультиплексором называется комбинационное логическое устройство, предназначенное для управляемой передачи данных от одного источника информации в несколько выходных каналов.

Согласно данному определению, демульплексор в общем случае имеет один информационный вход, n адресных входов и 2n выходов.

|

Q0

Q0

D A0A1 Q1

D A0A1 Q1

вход Выход Рис. 3 3

вход Выход Рис. 3 3

Q2

Q2

|

Q3

Q3

Таблица 3.2

| A1 | A0 | Q0 | Q1 | Q2 | Q3 |

| 0 | 0 | D | 0 | 0 | 0 |

| 0 | 1 | 0 | D | 0 | 0 |

| 1 | 0 | 0 | 0 | D | 0 |

| 1 | 1 | 0 | 0 | 0 | D |

Q0=D

Q1=D A0

A0

Q2=DA1

Q3=DA1A0

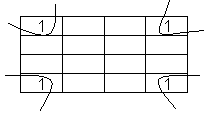

Рис 3.4 Демультиплексор

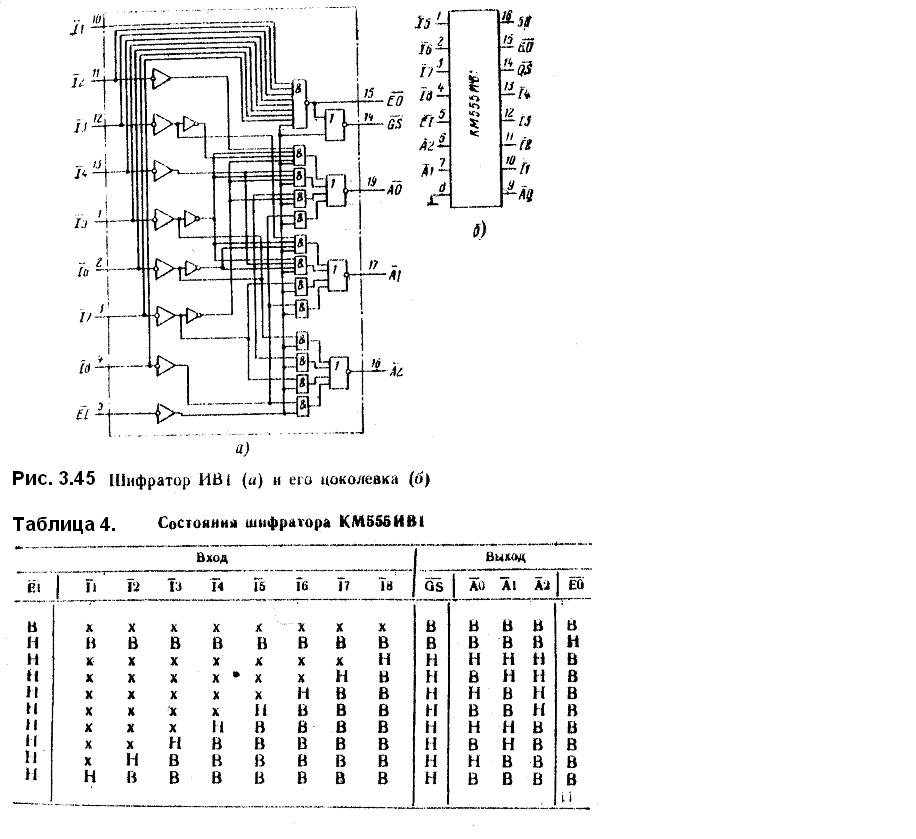

3.3 Шифраторы

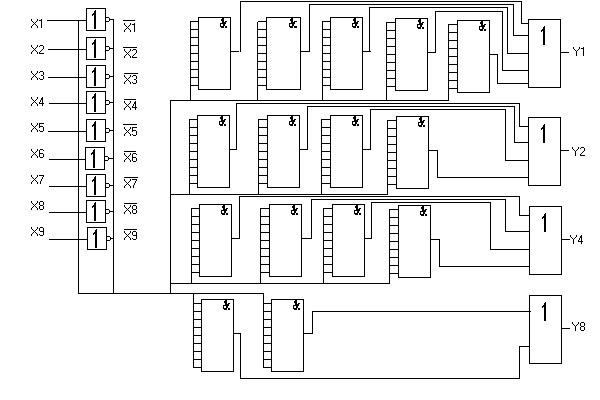

Шифратором называется комбинационное устройство, для преобразования чисел из десятичной системы исчисления в двоичную. Рис. 3.5

Таблица 3.3

Таблица 3.3

| X1 | X2 | X3 | X4 | X5 | X6 | X7 | X8 | X9 | Y1 | Y2 | Y4 | Y8 |

| 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 0 | 0 |

| 0 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 0 |

| 0 | 0 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 1 | 0 | 0 |

| 0 | 0 | 0 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 0 |

| 0 | 0 | 0 | 0 | 1 | 0 | 0 | 0 | 0 | 1 | 0 | 1 | 0 |

| 0 | 0 | 0 | 0 | 0 | 1 | 0 | 0 | 0 | 0 | 1 | 1 | 0 |

| 0 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 0 | 1 | 1 | 1 | 0 |

| 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 0 | 0 | 0 | 1 |

| 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 1 | 0 | 0 | 1 |

Y1=X1

+

+

X3

X3

+

+

X5

X5

+

+

X7

X7

+

+

X9

X9

Y2= X2

X2

+

+

X3

X3

+

+

X6

X6

+

+

X7

X7

Y4=

X4

X4

+

+

X5

X5

+

+

X6

X6

+

+

X7

X7

Y8=

X8

X8 +

+

X9

X9

3.4 Дешифратор

3.4 Дешифратор

Дешифратором называется комбинационное логическое устройство для преобразования чисел из двоичной системы исчисления в десятичную.

|  | ||||

| |||||

20 A1 DC Q1

20 A1 DC Q1

Q2

Q2

21 A2 Q3

21 A2 Q3

вход Q4

вход Q4

22 A4 Q5 выход Q

22 A4 Q5 выход Q

Q6

Q6

23 A8 Q7

23 A8 Q7

Q8

Q8

Q9 Рис. 3.7

Q9 Рис. 3.7

Таблица 3.4

| счет | входной код А | выходной код Q | |||||||||||

| А1 | А2 | А4 | А8 | Q1 | Q2 | Q3 | Q4 | Q5 | Q6 | Q7 | Q8 | Q9 | |

| 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| 1 | 1 | 0 | 0 | 0 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| 2 | 0 | 1 | 0 | 0 | 0 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| 3 | 1 | 1 | 0 | 0 | 0 | 0 | 1 | 0 | 0 | 0 | 0 | 0 | 0 |

| 4 | 0 | 0 | 1 | 0 | 0 | 0 | 0 | 1 | 0 | 0 | 0 | 0 | 0 |

| 5 | 1 | 0 | 1 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 0 | 0 | 0 |

| 6 | 0 | 1 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 0 | 0 |

| 7 | 1 | 1 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 0 |

| 8 | 0 | 0 | 0 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 0 |

| 9 | 1 | 0 | 0 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 |

Q1=A1

Q2= A2

A2

Q3=A1A2

Q4=

A4

A4

Q5=A1 A4

A4

Q6= A2A4

A2A4

Q7=A1A2A3

Q8=

A8

A8

Q9=A1

A8

A8

Рис 3.8 Схема Дешифратора

3.5 Преобразователь кодов, дешифратор двоичного кода в семисегментный.

Преобразователем кода называется комбинационное логическое устройство, предназначенное для преобразования вида кодированной информации.

a

a

А1 DC a

А1 DC a

входной код А2 b f b

входной код А2 b f b

А4 c g

А4 c g

А8 d c

А8 d c

e выход e

e выход e

f ной d

f ной d

g код

g код

Рис. 3.9

Рис. 3.9

Таблица 3.5

| Входной код | выходной код |

| |||||||||

| счет | A1 | A2 | A4 | A8 | a | b | c | d | E | f | g |

|

| 0 | 0 | 0 | 0 | 1 | 1 | 1 | 1 | 1 | 1 | 0 |

| 1 | 1 | 0 | 0 | 0 | 0 | 1 | 1 | 0 | 0 | 0 | 0 |

| 2 | 0 | 1 | 0 | 0 | 1 | 1 | 0 | 1 | 1 | 0 | 1 |

| 3 | 1 | 1 | 0 | 0 | 1 | 1 | 1 | 1 | 0 | 0 | 1 |

| 4 | 0 | 0 | 1 | 0 | 0 | 1 | 1 | 0 | 0 | 1 | 1 |

| 5 | 1 | 0 | 1 | 0 | 1 | 0 | 1 | 1 | 0 | 1 | 1 |

| 6 | 0 | 1 | 1 | 0 | 1 | 0 | 1 | 1 | 1 | 1 | 1 |

|

| 1 | 1 | 1 | 0 | 1 | 1 | 1 | 0 | 0 | 0 | 0 |

| 8 | 0 | 0 | 0 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 |

| 9 | 1 | 0 | 0 | 1 | 1 | 1 | 1 | 1 | 0 | 1 | 1 |

a=

+

+ A2

A2

+A1A2

+A1A2

+A1

+A1 A4

A4 +

+ A2A4

A2A4 +

+

A8+

A8+

A1A2A4

b=

+A1

+A1

+

+ A2

A2

+ A1A2

+ A1A2

+

+

A4

A4 + A1A2A4

+ A1A2A4 +

+

A8+

A8+ A2A4

A2A4

c=

+ A1

+ A1

+ A1A2

+ A1A2

+

+

A4

A4 + A1

+ A1 A4

A4 +

+ A2A4

A2A4 +

+

A1A2A4 +

+

A8+ A1

A8+ A1

A8

A8

d=

+

+ A2

A2

+ A1A2

+ A1A2

+

+

A4

A4 +

+ A2A4

A2A4 +

+

A8+

A8+

A1

A8

A8

e=

+

+ A2

A2

+

+ A2A4

A2A4 +

+

A8

A8

f=

+

+

A4

A4 + A1

+ A1 A4

A4 +

+ A2A4

A2A4 +

+

A8+ A1

A8+ A1

A8

A8

g= A2

A2

+ A1A2

+ A1A2

+

+

A4

A4 + A1

+ A1 A4

A4 +

+ A2A4

A2A4 +

+

A8+

A8+

A1

A8

A8

Рис. 3.10

Рис. 3.10

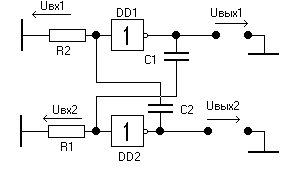

3.6 Генераторы на логических элементах, таймеры.

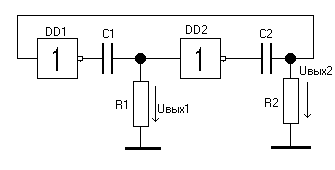

Автогенератор на основе двух инверторов.

Автогенератор на основе двух инверторов.

Рис 3.11 Схема автогенератора на основе двух инвертеров

Рис. 3.12

Tr=1,4R1C1

R1=R2 C1=C2

Рис. 3.13

Рис 3.6 Схема автогенератора на основе двух инвертеров в ином виде

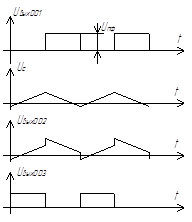

Автогенератор с времязадающей RC цепью

Автогенератор с времязадающей RC цепью

Tr=3RC Рис. 3.14

Tr=3RC Рис. 3.14

Рис 3.15 Схема автогенератора с времязадающей RC цепью

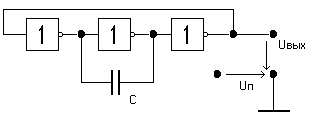

Автогенератор с одним времязадающим конденсатором и тремя инверторами.

Tr=CRэкв[lnUп/(Uп-Uпф)+Uпф/ (Uп-Uпф)]

Рис. 3.16

Рис 3.17 Автогенератор с одним времязадающим конденсатором и тремя инверторами

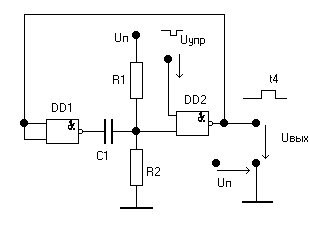

Одновибратор на основе двух инверторов.

Рис. 3.18

Рис. 3.18

Рис 3.19 Схема одновибратора на основе двух инверторов.

t4=RCln[(Uп-U0)/(Uп-Uпф)]

Условные обозначения микросхем преобразователей кодов, мультиплексоров, демультиплексоров, генераторов.

Таблица 3.6

| Обозначение | Вид микросхемы |

| Шифраторы | ИВ |

| Дешифраторы демультиплексоры | ИД |

| Мультиплексоры | КП |

| Преобразователи кодов | ПП |

| Генераторы прямоуг. сигнала | ГГ, ГФ |

| Формирователи прямоуг. импульса | АГ |

3.7 Алгебра логики.

Основные теоремы алгебры Буля.

Джордж Буль(1815-1864).

Англйский математик

Теоремы для одной переменной

1. x+0=x 4.  7. x

7. x =0

=0

2. x+1=1 5. x 0=0 8. x

0=0 8. x x=x

x=x

3. x+x=x 6. x 1=x 9.

1=x 9.  =x

=x

Теоремы для двух и более переменных

10. Переместительные законы:

a) x+y=y+x

b) x*y=y*x

11.Сочетательные законы:

a) x+y+z=x+(y+z)=(x+y)+z

b) x*y*z=x*(y*z)=(x*y)*z

12. Распределительный закон

a) x*(y+z)=x*y+x*z

b) x+y*z=(x+y)*(x+z)

13. Закон поглащения

a) x+x*y=x

b) x*(x+y)=x

14.

a) (x+ )*y=x*y

)*y=x*y

b) x* +y=x+y

+y=x+y

15. Закон склеивания

a) x*y+ *y=y

*y=y

b) (x+y)*( +y)=y

+y)=y

16.Теорема Моргана (1806-1871 Шотландский математик

a)  =

=

b)  =

=

3.8 Способы построения логических функций.

Графический Алгебраический

X1

X1

1

1

|

0

0

t

t

X2

X2

|  |

1

1

|

0

0

t

t

Y

Y

1 1 1

0 0

t

Рис.3.20

Переход к логической схеме.

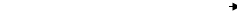

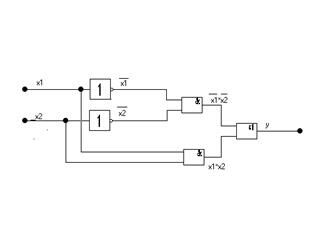

ДНФ Рис. 3.21 КНФ Рис. 3.22

| |||

|

3.9 Минимизация логических функций.

С помощью алгебраических преобразований

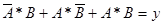

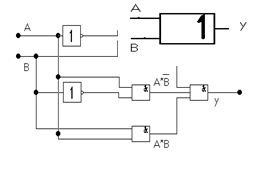

Пример 1:

a)  Рис.3.23

Рис.3.23

b)

|

Рис.3.24

A+B=y

A+B=y

| A | B | Y |

| 0 | 0 | 0 |

| 0 | 1 | 1 |

| 1 | 0 | 1 |

| 1 | 1 | 1 |

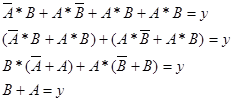

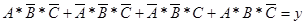

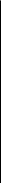

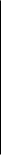

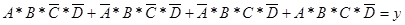

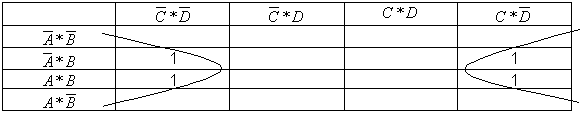

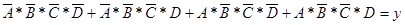

Пример 2:

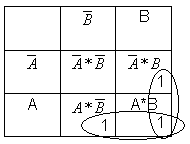

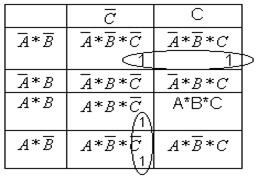

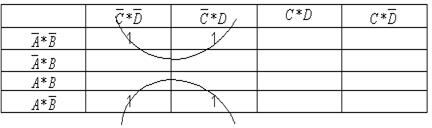

3.10. Использование карт Карно.

Карно (1753-1823) Французский математик

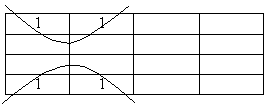

Карта Карно представляет собой прямоугольник, разбитый на квадраты, число которых равно общему числу наборов для данной функции n переменных, т.е. оно равно 2n.

n=2

n=3

|

| B | |

|

|

|

|

| A |

| A*B |

|

| C | |

|

|

|

|

|

|

|

|

|

|

| A*B*C |

|

|

|

|

n=4

|

|

|

|

| |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

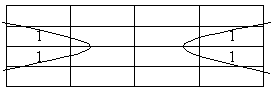

Правила применения карт Карно.

1) Если единицами заполнены две соседние строки(1) или два соседних столбца(2), либо две строки или два столбца, расположенные по краям карты(3), то восемь слагаемых четвертого ранга можно заменить слагаемыми третьего ранга, у которых общие переменные.

(1)

(1)

(2)

(2)

|

|

(3)

2) Если единицами заполнена одна строка или один столбец или четыре угловых квадрата или четыре квадрата, которые, в свою очередь, составляют квадрат, то соответствующие четыре слагаемых четвертого ранга заменяются одним слагаемым второго ранга, в которое входят переменные, общие для этих квадратов.

| |||||||

|  | ||||||

| |||||||

Четыре квадрата, которые, в свою очередь, составляют квадрат

Одна строка или один столбец

Четыре угловых квадрата

3) Если единицы расположены в двух соседних квадратах, в том числе и находящиеся на концах строки, то соответствующие два слагаемых четвертого ранга склеиваются, превращаясь в одно слагаемое третьего ранга.

| |||

|

Примеры

1.

|  | ||

|  |

2.

|  | ||

3.

| ||||||||

|  | |||||||

|  |

|

4.

|  |

|

5.

|

6.

|

| |||

| |||

3.11 Домашнее задание по комбинационным устройствам.

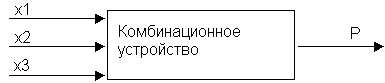

Спроектировать комбинационное устройство цифровой электронной техники для автомата управления технологической операцией.

На вход комбинационного устройства поступают сигналы от трех датчиков. На выходе формируется выходной сигнал P=1 при десятичных кодах входных величин 0,2,3,7. При остальных кодах P=0.

|

Рис. 3.24

Составляем таблицу истинности.

22 21 20

| X3 | X2 | X1 | P | |

| 0 | 0 | 0 | 1 | 0 |

| 0 | 0 | 1 | 0 | 1 |

| 0 | 1 | 0 | 1 | 2 |

| 0 | 1 | 1 | 1 | 3 |

| 1 | 0 | 0 | 0 | 4 |

| 1 | 0 | 1 | 0 | 5 |

| 1 | 1 | 0 | 0 | 6 |

| 1 | 1 | 1 | 1 | 7 |

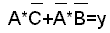

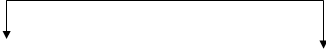

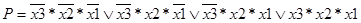

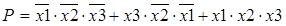

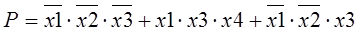

Записываем логическое уравнение, связывающее входные и выходные параметры в ДНФ:

|  | ||

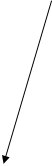

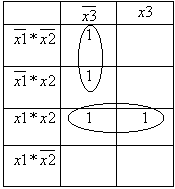

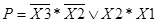

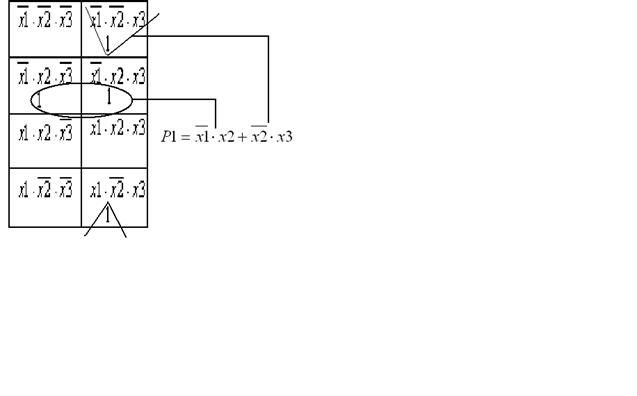

Минимизация логического уравнения с использованием карты Карно.

Проверочная таблица истинности

| X3 | X2 | X1 | P |

| 0 | 0 | 0 | 1 |

| 0 | 0 | 1 | 0 |

| 0 | 1 | 0 | 1 |

| 0 | 1 | 1 | 1 |

| 1 | 0 | 0 | 0 |

| 1 | 0 | 1 | 0 |

| 1 | 1 | 0 | 0 |

| 1 | 1 | 1 | 1 |

.

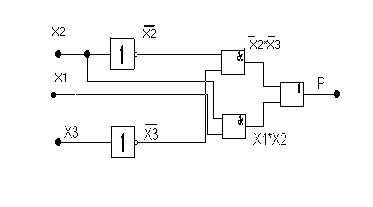

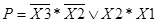

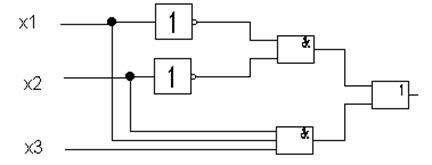

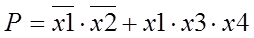

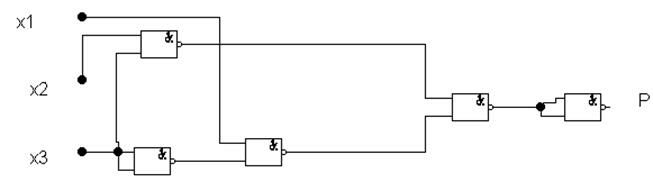

Построение логической схемы.

Рис. 3.25

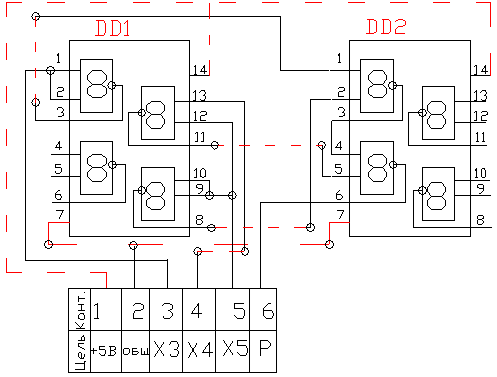

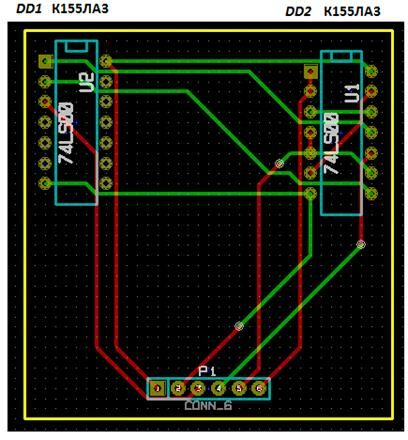

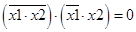

Преобразуем уравнение по теореме Де Моргана.

(для перехода в одну логическую систему И-НЕ)

(DD1,DD2 – KI55ЛА3, И-НЕ – 2-е микросхемы). Рис. 3.26

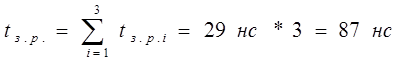

Расчет задержки выходного сигнала P.

Входной сигнал проходит по линии, включающей в себя три последовательно соединенных логических элемента KI55ЛА3.

Проектирование печатной платы.

|

Рис. 3.27

,

3.12 Семинар №1

Семинар №1

Задача 1.1.

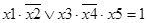

Вычислить значения логических переменных Р по уравнениям для значений х1=1 и х2=0

Р1=х1 х2×

х2×

х2=1 Р4=

х2=1 Р4=

Р2=(х1 х2) ×

х2) ×

х2=0 Р5=

х2=0 Р5=

Р3= (х1 x2) ×(

x2) ×(

х2)=0

х2)=0

Задача 1.2.

Изобразить логические схемы , соответствующие заданным в задаче 1.1 логическим уравнениям.

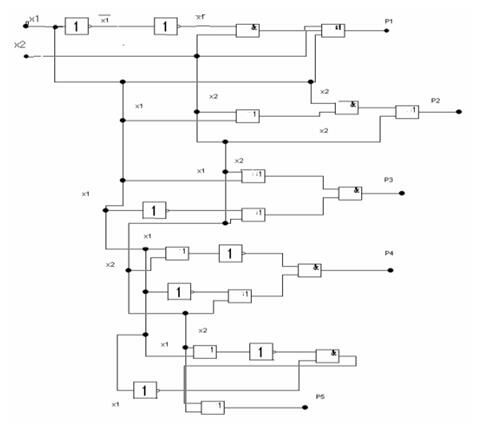

Рис. 3.28

Задача 1.3.

Для графиков функционирования автомата управления технологическим процессом, задающих логическую связь В=f(х1,х0) рис.1.3 составить таблицу истинности, записать логическое уравнение и составить логическую схему ,реализующую эту связь.

Рис.3.29

|

Х1 |

Х2 |

В |

| 0 1 1 0 | 0 0 1 1 | 1 0 1 0 |

Рис. 3.30

Рис. 3.30

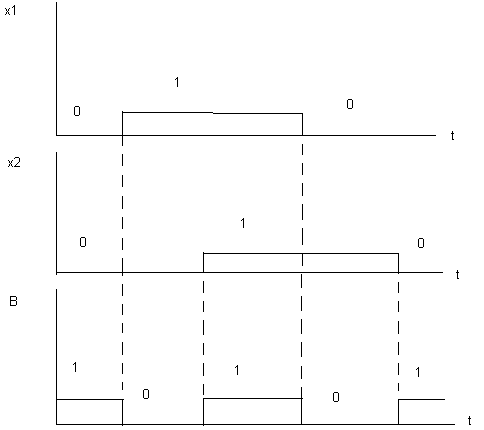

Задача 1.4.

Определить значение Р при значениях аргументов х1=1,х2=0,х3=1,х4=0,х5=1.

х1=1,х2=0,х3=1,х4=0,х5=1

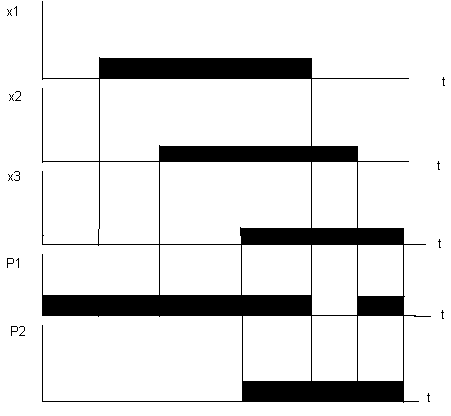

Задача 1.5.

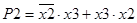

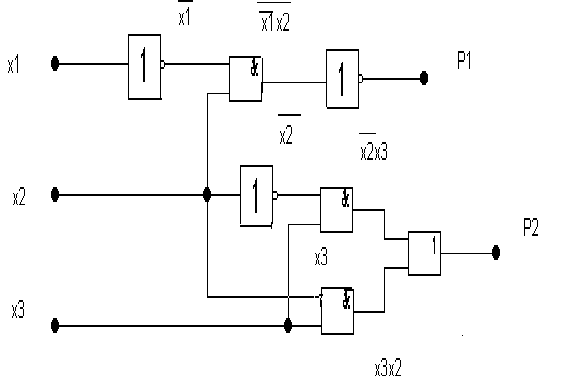

По графикам входных сигналов х1,х2,х3 построить графики выходных сигналов Р1 иР2.

Рис. 3.31

=

=

Рис. 3.32

Рис. 3.32

| Х1 | Х2 | Р1 |

| 0 1 0 1 | 0 0 1 1 | 1 1 0 1 |

Задача 1.6

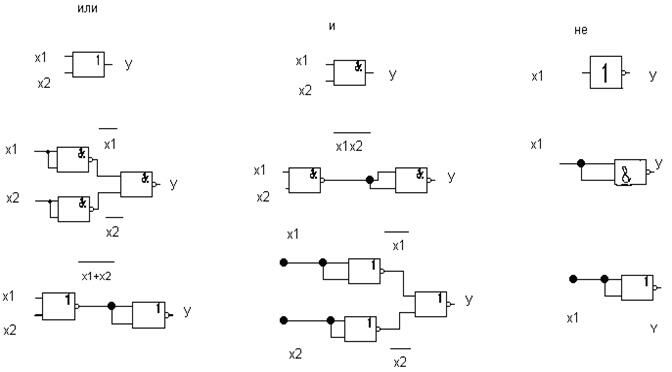

Построить схемы, реализующие операции ИЛИ, И, НЕ применением элементов И-НЕ, ИЛИ-НЕ.

Рис. 3.33 Рис. 3.34 Рис 3.35

3.13 Семинар№2.Проектирование комбинационных устройств.

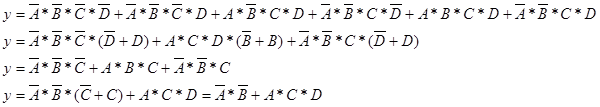

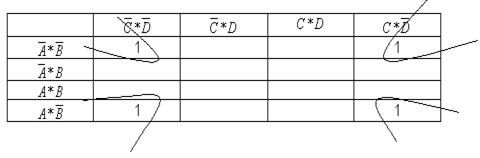

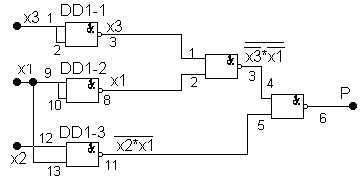

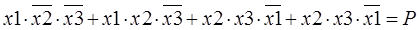

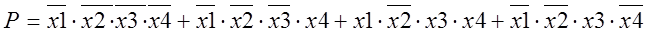

Задача 2.1

По заданной таблице истинности комбинационного устройства записать уравнение ДНФ, минимизировать его. По минимизированному уравнению рассчитать значения Р для всех сочетаний входных сигналов. Построить логическую схему, реализующую это комбинационное устройство.

| Х3 | Х2 | Х1 | Р |

| 0 0 0 0 1 1 1 1 | 0 0 1 1 0 0 1 1 | 0 1 0 1 0 1 0 1 | 0 1 0 1 0 0 1 1 |

Неминимизированное уравнение:

Карта Карно.

Рис. 3.36

Рис. 3.36

Логическая схема

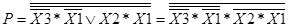

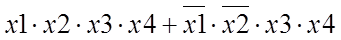

Задача 2.2

По заданной таблице истинности получить минимальную ДНФ. Составить логическую схему, реализующую заданную логическую связь.

| Х3 | Х2 | Х1 | Р |

| 0 0 0 0 1 1 1 1 | 0 0 1 1 0 0 1 1 | 0 1 0 1 0 1 0 1 | 1 0 0 0 1 0 0 1 |

- неминимизированное уравнение

|

|

| |

|

| 1 | 1 |

|

| ||

|

| 1 | |

|

|

- минимизированное уравнение

- минимизированное уравнение

Рис. 3.37

Логическая схема

Задача 2.3

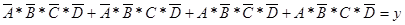

Минимизировать логическое уравнение:

Задача 2.4

Минимизировать логическое уравнение, представленное в карте Карно.

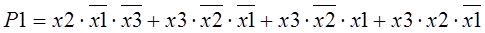

2.5 Комбинационное устройство имеет три входных и два выходных сигнала. Логическая связь входных и выходных сигналов задана таблицей истинности. Получить систему уравнений и минимизовать ДНФ для выходных сигналов. Построить логическую схему.

Задача 2.5

Логическую схему задачи 2.1 выполнить в базисе И-НЕ.

Рис. 3.38

Задача 2 .6

Комбинационное устройство имеет три входных и два выходных вывода. Логическая связь входных и выходных сигналов задана таблицей истинности. Получить систему уравнений в минимизированной ДНФ для выходных сигналов. Построить логическую схему применив декомпозицию.

| Х3 | Х2 | Х1 | Р1 | Р2 |

| 0 0 0 0 1 1 1 1 | 0 0 1 1 0 0 1 1 | 0 1 0 1 0 1 0 1 | 0 0 1 0 1 1 1 0 | 0 0 1 1 1 1 1 0 |

P1

P2

Задача 2.7

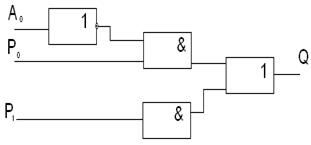

Построить логическую схему двухвходного мультиплексора(2:1).

Сколько строк будет содержать таблица истинности мультиплексоров 4:1,8:1,16:1?

Рис. 3.39

| A0 | Q |

| 0 | P0 |

| 1 | P1 |

Задача 2.8

Построить логическую схему демультиплексора 1:4.

Рис. 3.40

Рис. 3.40

| A0 | A1 | Q0 | Q1 | Q2 | Q3 |

| 0 | 0 | P0 | 0 | 0 | 0 |

| 1 | 0 | 0 | P0 | 0 | 0 |

| 0 | 1 | 0 | 0 | P0 | 0 |

| 1 | 1 | 0 | 0 | 0 | P0 |

Q0=P0*A0*A1; Q1=P0*A0*A1; Q2=P0*A0*A1; Q3=P0*A0*A1

Рис. 3.41 Логическая схема демультиплексора

3.14 Лабораторная работа “Логические элементы”.

Авторы Атаманов В.Н, Лаврентьев В.В.

- ОПИСАНИЕ ЛАБОРАТОРНОГО СТЕНДА

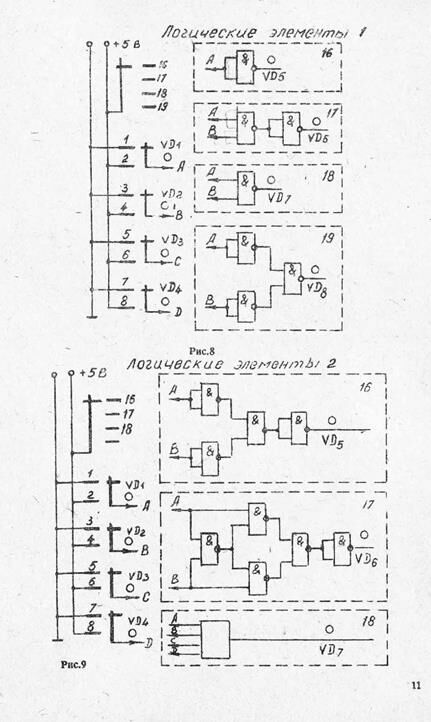

На рис. 3.42,3.43 представлены лабораторные установки стенд 1, стенд 2 для исследования логических элементов

Рис.3.42. Лабораторная установка стенд 1

Лабораторный стенд2, внешний вид которого представлен на рис. 3.42, содержит источник питания, контрольные точки, измерительные приборы и разъем для присоединения исследуемого электронного устройства. Исследуемые электронные устройства размещены в кассетах, на лицевых панелях которых изображены принципиальные схемы. Набор логических схем , исследуемых в данной работе, размещен в двух кассетах: "логические элементы 1, "логические элементы 2".

Рис. 3.43

Рис. 3.43

Нумерация переключаемых контактов на приведенных рисунках соответствует нумерации контактов переключателей, нанесенной на панели лабораторного стенда.

Переключатели S1 (контакты 1,2), S2 (контакты 3,4), S3 (контакты 5,6), S4 (контакты 7,8) служат для установления логических нуля или единицы на соответствующих входах А, В, С, Д логических элементов. Переключатель S7 (контакты 16, 17, 18, 19) служит для подключения исследуемого элемента к источнику питания.

Наличие логических нуля или единицы на входах и выходах логических элементов индицируется светодиодами VDl... VD8. Свечение светодиода свидетельствует о наличии логической единицы на соответствующих входе или выходе, отсутствие свечения - наличие логического нуля.

Общее подключение лабораторного стенда к питающей сети осуществляемся выключателем SS (см. рис. 3.42).

ПРАВИЛА ТЕХНИКИ БЕЗОПАСНОСТИ

1. Работы выполняются строго в соответствии с заданиями и указаниями по их выполнению.

2. Перед включением стенда необходимо знать функциональное назначение всех элементов коммутации (выключателей, переключателей и т.п.) и убедиться, что все исследуемые в работе устройства отключены от источника электропитания.

3. После вылолнения работы необходимо выключить электропитание всех исследованных устройств.

4. При выполнении работ запрещается:

а) включать схемы без разрешения преподавателя;

б) пользоваться неисправными приборами и устройствами.

Соблюдение указаных правил каждым студентом строго обязательно.

2. УКАЗАНИЯ ПО ВЫПОЛНЕНИЮ РАБОТЫ

Задание 1. Исследовать работу логических элементов (ЛЭ) «И, И-НЕ, НЕ» рис.3.44

1.1. Найти на стенде микросхемы D7.1.,D2.2.,D10.1. и определить выполняемые ими логические функции.

1.2. Заполнить таблицы истинности, подавая на входы указанных микросхем комбинации логических уровней.

Для подачи на вход ЛЭ уровня логической «1» необходимо подключить, используя перемычки, соответствующий вход микросхемы к резисторам R76,R79,R72, либо R73, которые соединены с источником питания «+5 В.». Для подачи на вход ЛЭ уровня логического «0» необходимо этот вход подключить к общему проводу. Выходной сигнал с микросхем регистрировать осциллографом.

1.3. По таблицам составить логические уравнения, определить выполняемую функцию и привести условное обозначение элемента.

Таблица истинности для микросхемы D7.1 Условное обозначение

| A | B | F |

| 0 | 0 | |

| 0 | 1 | |

| 1 | 0 | |

| 1 | 1 |

Логическое уравнение …………………………………..

Выполняемая функция ………….

Таблица истинности для микросхемы D2.2 Условное обозначение

| А | B | F |

| 0 | 0 | |

| 0 | 1 | |

| 1 | 0 | |

| 1 | 1 |

Логическое уравнение ………………………………….

Выполняемая функция ……………….

Таблица истинности для микросхемы D10.1. Условное обозначение

| A | F |

| 0 | |

| 1 |

Логическое уравнение …………………………………….

Выполняемая функция ……

Задание 2. Определить логическую функцию, выполняемую комбинационным устройством.

2.1.Собрать монтажную схему (с помощью перемычек, выделены красным, рис.3.44) используя микросхемы D2.1, D2.2, D7.1, D10.1.

2.2.Составить логическую схему, используя монтажную, и описать ее уравнением. Упростить составленное уравнение, используя теорему Де-Моргана и постулаты Булевой алгебры, до получения элементарной функции.

2.2.Составить логическую схему, используя монтажную, и описать ее уравнением. Упростить составленное уравнение, используя теорему Де-Моргана и постулаты Булевой алгебры, до получения элементарной функции.

Рис.3.44. Структурная схема лабораторного стенда

2.3.Проверить полученное уравнение, экспериментально заполнив таблицу истинности и составив по ней логическое уравнение. Уровень логической «1» на входах ЛЭ задается постоянно ( входы А и В, рис.3.45) с помощью резисторов R72, R76, а уровень логического «0» с помощью перемычек подсоединяемых к общему проводу (выделены зеленым цветом). Выходной сигнал регистрируется осциллографом.

Таблица истинности комбинационного устройства

| A | B | F |

|

| ||

Логическое уравнение ……………………………….

Задание 3. Исследовать работу логического элемента «И» в функции электронного ключа.

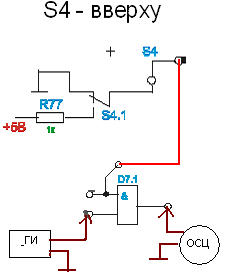

3.1. Соединить выход генератора (PULSE, 5 V p-p , MAX.) c одним из входов микросхемы D7.1. Второй вход микросхемы соединить с выключателем S4.

К выходу микросхемы подключить осциллограф (рис.10.). Включить генератор и стенд.

3.2.Определить при каком положении выключателя S4 на выходе элемента появляются импульсы. Зарисовать осциллограммы и пояснить работу ключа.

Рис.3.45. Электронный ключ

Задание 4. Исследовать работу формирователя импульсов по фронту прямоугольных импульсов генератора.

4.1.Собрать схему формирователя импульсов (см. рис. 3.46.). Для регистрации сигналов использовать двух лучевой осциллограф.

Установка органов управления осциллографа: развертка по горизонтали 0,5 мс./см., усиление для первого и второго лучей 2 В./см.; Нажатые кнопки на осциллографе. В блоке развертки: ТВ; +; внешн. II..

В блоке усилителей: I@; II@ .

У генератора использовать выход PULSE 5 V p-p..

4.2.Поставить выключатель S4 в верхнее положение включить генератор и стенд. Зарисовать осциллограммы.

4.3. Перевести S4 в нижнее положение (контакт S4.2 замкнут, как показано на рисунке.). Зарисовать с экрана осциллограммы первого и второго луча. Пояснить работу формирователя импульсов.

Рис.3.46. Формирователь импульсов

ЗАДАНИЯ И УКАЗАНИЯ ПО ВЫПОЛНЕНИЮ РАБОТЫ

А. Исследование двухвходовых логических элементов

1. Заполнить таблицы истинности исследуемых двухвходовых элементов. Для этого необходимо:

а) установить соответствующую кассету в стенд;

б) перерисовать табл. 1 и 2 в отчет;

в) установить требуемые комбинации логических нулей и едениц на входах исследуемых схем, определить состояние выхода для каждой входной комбинации и полученные результаты занести в табл. 1 отчета.

Рис.3.47 Логические схемы лабораторного стенда

Таблица 1

| Таблица истинности | Булево влияние | Логическая функция | Условное обозначение | ||||

| 16 | А | У | |||||

| 0 | |||||||

| 1 | |||||||

| 17 | А | В | У | ||||

| 0 | 0 | ||||||

| 0 | 1 | ||||||

| I | 0 | ||||||

| I | I | ||||||

| 18 | А | В | У | ||||

| 0 | 0 | ||||||

| 0 | 1 | ||||||

| I | 0 | ||||||

| I | I | ||||||

| 13 | А | в | У | ||||

| 0 | 0 | ||||||

| 0 | 1 | ||||||

| 1 | 0 | ||||||

| 1 | 1 | ||||||

2. Составить булевы выражения функционирования исследуемых логических элементов в соответствии с их принципиальной схемой, представленной на кассете, и занести полученные выражения и табл. 2 отчета.

3. Упростить составленные булевы выражении, пользуясь набором вычислительных правил булевой алгебры.

4. По упрощенному логическому уравнению определить логическую функцию каждого исследуемого элемента и занести ее в табл. 2 отчета.

5. Изобразить в табл. 2 отчета условное обозначение логического элемента, выполняющего соответствующую логическую функцию.

Таблица 2

| Таблица истинности | Булево выражение | Логическая функция | Условное обозначение | ||||||

| 16 | |||||||||

| А | В | У | |||||||

| 0 | 0 | ||||||||

| 0 | 1 | ||||||||

| 1 | 0 | ||||||||

| 1 | 1 | ||||||||

| 17 | А | В | У | ||||||

| 0 | 0 | ||||||||

| 0 | I | ||||||||

| I | 0 | ||||||||

| 1 | I | ||||||||

| 18 | А | В | С | Д | У | i | |||

| 0 | 0 | 0 | 0 | ||||||

| 0 | 0 | 0 | I | ||||||

| 0 | 0 | I | 0 | ||||||

| 0 | 0 | 1 | I | ||||||

| 0 | 1 | 0 | 0 | ||||||

| 0 | 1 | 0 | 1 | ||||||

| 0 | I | I | 0 | ||||||

| 0 | I | I | I | ||||||

| I | 0 | 0 | 0 | ||||||

| I | 0 | 0 | I | ||||||

| I | 0 | 1 | 0 | ||||||

| 1 | 0 | I | 1 | ||||||

| I | 1 | 0 | 0 | ||||||

| I | I | 0 | I | ||||||

| 1 | I | 1 | 0 | ||||||

| 1 | 1 | 1 | I | ||||||

Б. Исследование четырехвходного логического устройства

1. Заполнить таблицу истинности исследуемого четырехвходного логического устройства. Для этого необходимо:

а) установить соответствующую кассету в стенд;

б) устанавливая требуемые комбинации логических нулей и единиц на входах исследуемого логического устройства (см. табл.2), определить состояние его выхода соответствующее каждой входной комбинации, и занести результаты в табл.2 отчета.

2. Составить булево выражение функционирования исследуемого логическою устройства по результатам полученной таблицы истинности .

3. Упростить булево выражение, используя карту Карно.

4. Синтезировать принципиальную схему исследуемого логического устройства, выполняющего логические операции, описываемые упрощенные булевым выражением.

СОДЕРЖАНИЕ ОТЧЕТА

Отчет составляется индивидуально каждым студентом и должен содержать:

1) титульный лист с названием работы, исполнителя, индекса группы и даты выполнения;

2} электрические схемы всех исследуемых устройств, вычерченные с помощью инструментов с соблюдением условных графических обозначений элементов;

3) таблицы, исходные и преобразованные булевы выражения, синтезированную схему в соответствии с заданием.

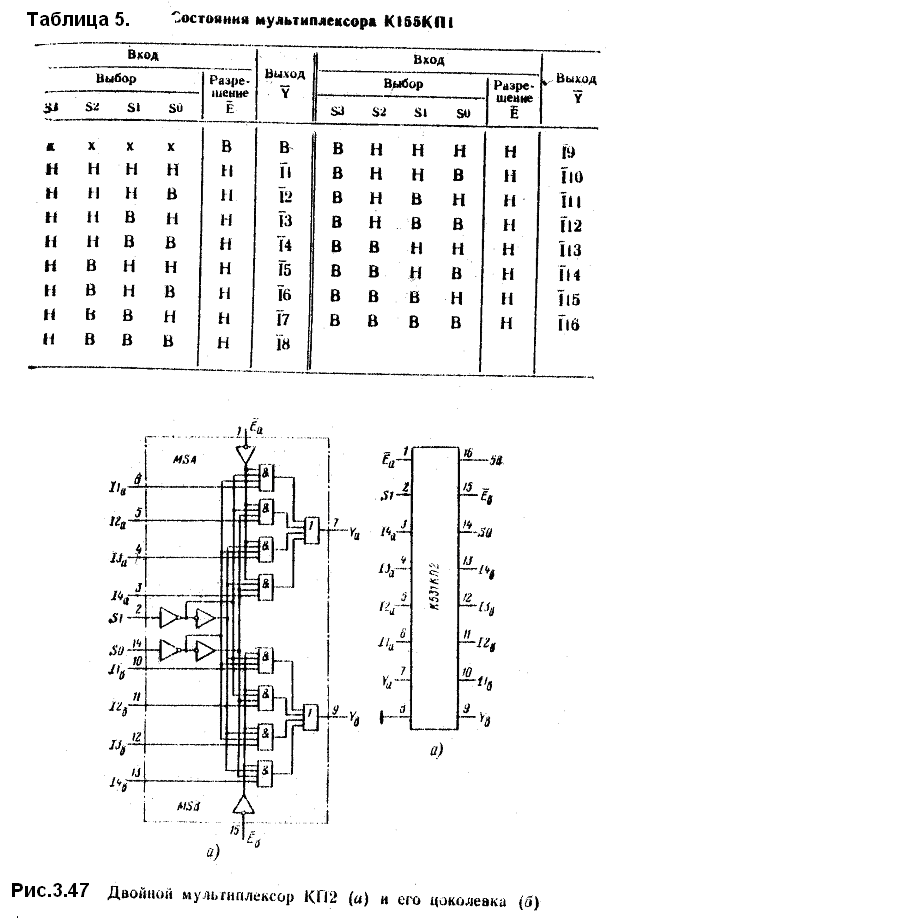

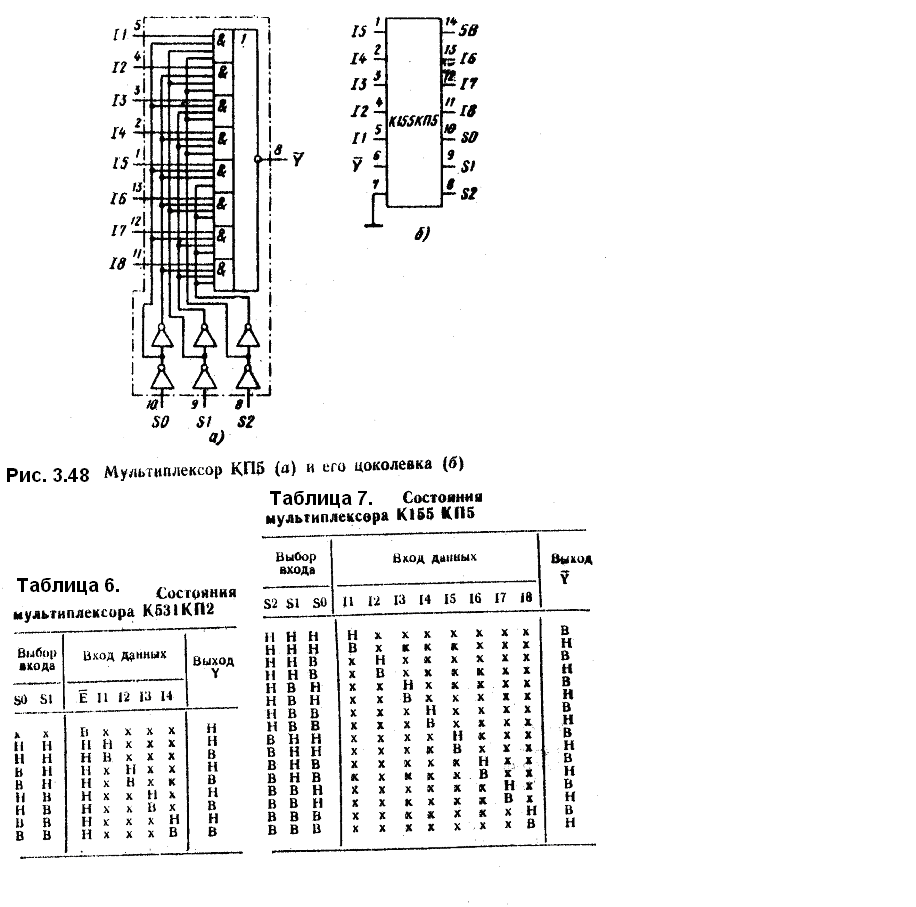

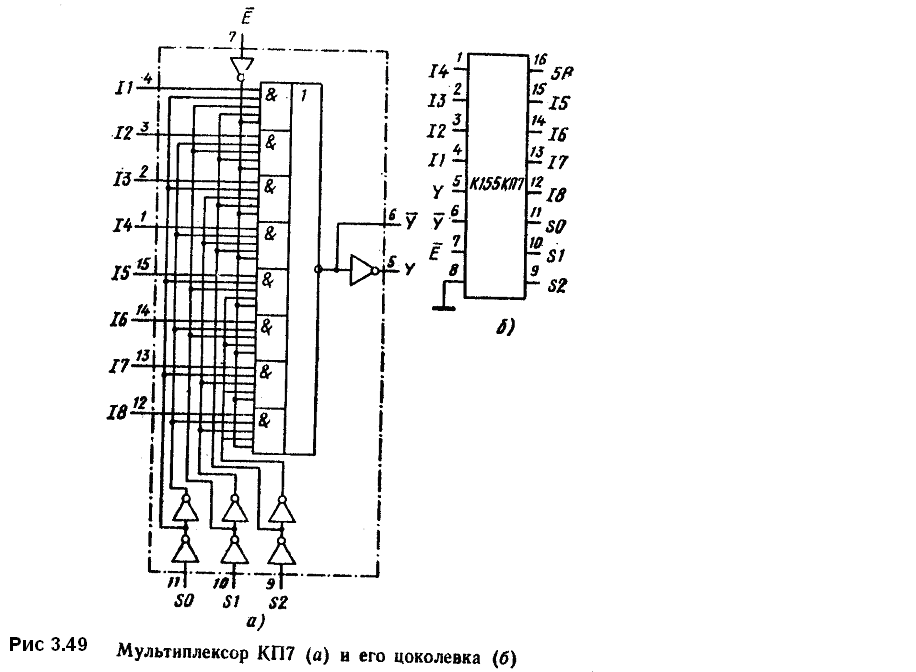

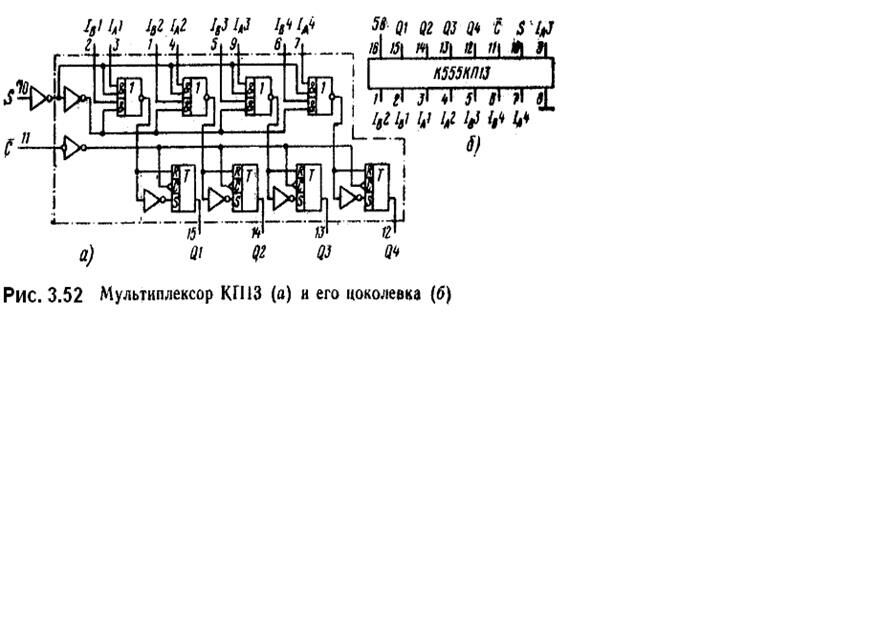

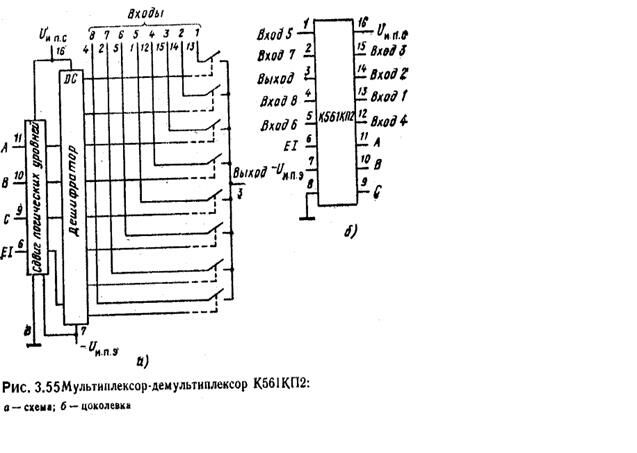

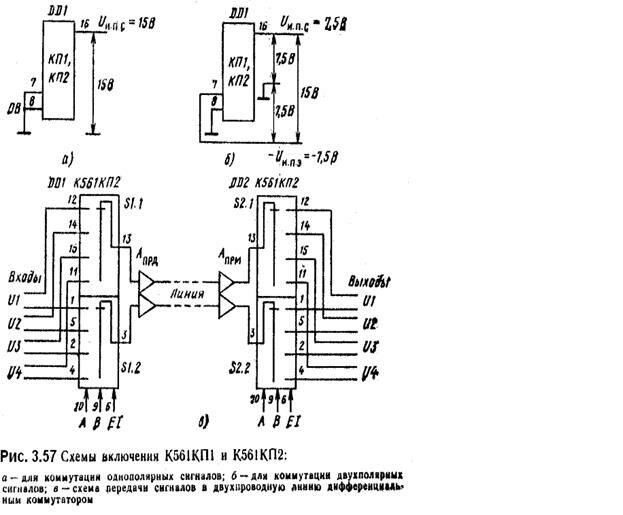

3.15 Дешифраторы, шифраторы, коммутаторы, мультиплексоры ТТЛ

"65 Договор аренды" - тут тоже много полезного для Вас.

.

3.16. Дешифраторы, шифраторы, коммутаторы, мультиплексоры КМОП

0

0 7

7