- Основная память со сложным расслоением

Лекция №7

Основная память со сложным расслоением

Фиксаторы помещены с выхода  модуля на его адресный вход. Это позволяет для

модуля на его адресный вход. Это позволяет для  модуля использовать свой относительный адрес, отличный от других.

модуля использовать свой относительный адрес, отличный от других.

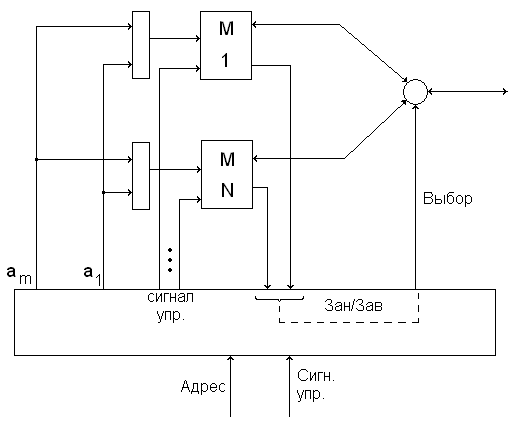

Эта структура более гибкая, поэтому необходимо новое устройство – контроллер памяти.

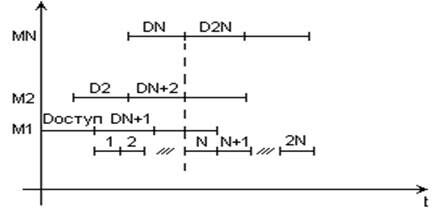

На контроллер поступает поток запросов от конвейера,  запрос требует 1 слова, и эти запросы обрабатываются по первому.

запрос требует 1 слова, и эти запросы обрабатываются по первому.

Для  запроса контроллер определяет занят модуль или нет, если свободен, то адрес /относительный/ помещается в адресный регистр и операция начинается. Если занят, то операция задерживается.

запроса контроллер определяет занят модуль или нет, если свободен, то адрес /относительный/ помещается в адресный регистр и операция начинается. Если занят, то операция задерживается.

Пока идет обращение к слову в соответствующем модуле, контроллер аналогично обрабатывает остальные запросы.

Когда модуль завершает операцию, то:

Рекомендуемые материалы

1) если операция была записью, то запускается новая операция;

2) если операция READ, то направляет данные к запросившим их конвейерам, а потом запускает новую операцию.

То есть выигрыш в производительности будет в N раз по сравнению с отдельным модулем.

Эта высокая скорость будет поддерживаться, если придет серия запросов, где первый модуль будет запрашиваться лишь 1 раз из N запросов.

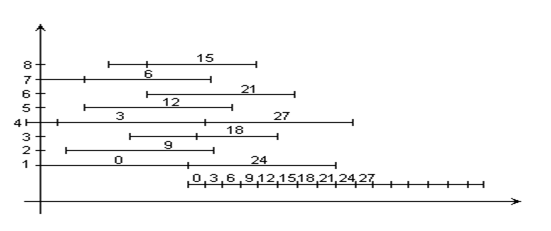

Будем считать, что память 8-кратно расслоенная. Тогда для запросов с любым промежутком 1, 3, 5, 7, 9, 11, скорость будет в 8 раз быстрее.

Для промежутка 3 последовательность адресов будет иметь вид 0, 3, 6, 9, 12, 15, 18, 21, 24, 27, а последовательность модулей 1, 4, 7, 2, 5, 0, 3, 6, 1, 4, 7. /Этот случай для равномерного распределения/.

При других значениях промежутка работа будет идти не с max скоростью, но все равно быстрее, чем с первым модулем.

Например, для промежутка = 2.

Входная последовательность адресов 0, 3, 6, 9, 12, 15, 18.

Промежуток = 3

Входная последовательность адресов 0, 2, 4, 6, 8

Промежуток = 2

Т.е. увеличение в 4 раза скорости по сравнению с первым модулем

Локальная память

Т.е. max скорость достижима лишь при обращении к сравнительно длинным наборам последовательно расположенных данных.

Эта скорость может совпадать с требуемой конвейером, но порядок доступа часто не соответствует тому, что необходим конвейеру.

Г.е.

Векторный процессор, оператор векторного сложения

1 опер + 1 опер  запись результата.

запись результата.

Т.е. необходимо по одному слову из  вектора.

вектора.

А при максимальной скорости выдается целая последовательность слов.

Т.е. необходимо ввести малую сверх быстродействующую память между конвейером и основной памятью. /кэш-память/

Она может быть видима или нет программисту.

Структуры:

1) произвольный доступ

2) с дисциплиной FIFO

3) ассоциативная память

Независимо от структуры организация лок. памяти одинакова!

а) поблочный обмен с основной памятью

б) одновременно более произв обмен с конвеером

Полная скорость доступа к лок памяти должна быть в 2 раза выше «30» для конвейера.

Существует 4 способа реализации лок. памяти.

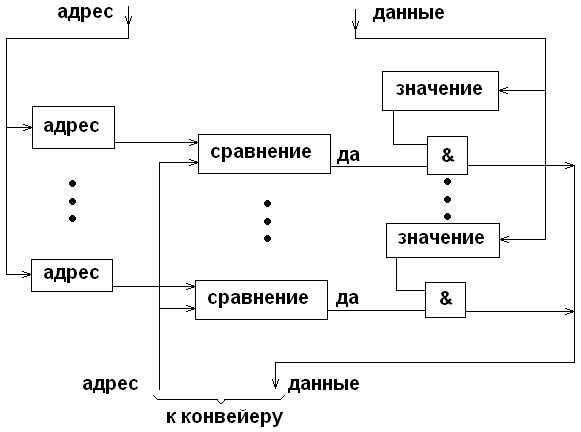

1) Ассоциативная КЭВМ-память.

элемент такой памяти содержит адрес основной памяти и данные с этого адреса.

элемент такой памяти содержит адрес основной памяти и данные с этого адреса.

Загрузка осуществляется поблочно, а считывание произвольно.

При загрузке данные и адрес заносятся в свободный элемент кэша.

Считывание

конвейер выдаёт необходимый адрес и производится сравнение с имеющимися адресными частями. Элемент памяти с соответствующим адресом выдаёт данные.

Конвейер лок. память не видит, но зато основная память представляется нерасслоенной и быстродействующей.

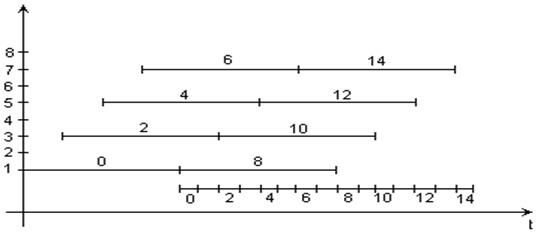

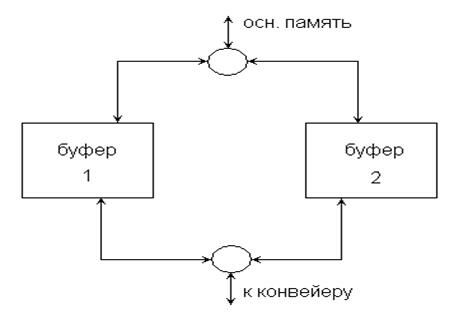

2) переключающийся /дуальный/ буфер

Это две памяти с произвольным доступом соединённых так, что пока одна осуществляет обмен с основной памятью, другая подключена к конвейеру.

Когда основная память и конвейер завершают работу, то происходит переключение.

Эта структура часто используется в векторных процессорах.

Т.е. векторные регистры CRA Y

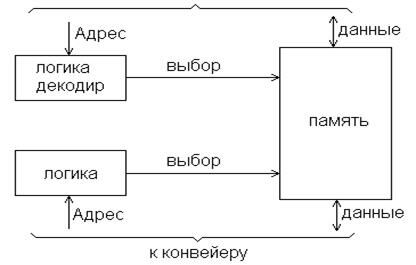

3) двухпортовая память с произвольным доступом.

Память небольшого объёма имеет два комплекта логических схем декодирования адресов и выборки, обеспечивающих одновременный доступ к её различным словам со стороны основной памяти и конвейера через 2 порта.

"Понятие блока. Операторы return, goto, метки" - тут тоже много полезного для Вас.

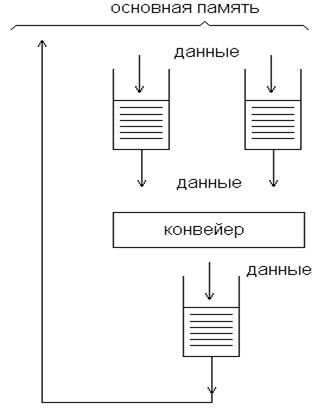

4) Очередь ????? FIFO

Данные поступают и выходят с различной скоростью. Здесь представлен арифметический конвейер векторного процессора.

Заполняется 2 входа конвейера и разгружается 1.

Пока обе входные очереди и 1 выходная не переполнятся, основная память может загружать или считывать данные в произвольном порядке.