Цап с параллельным интерфейсом входных данных

Цап с параллельным интерфейсом входных данных.

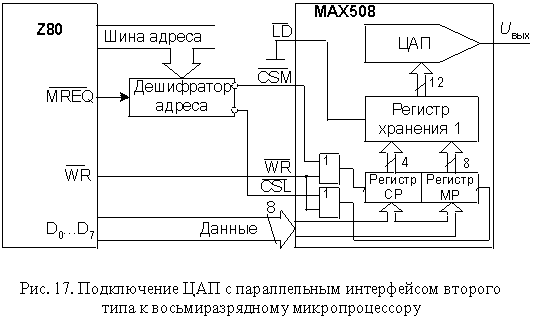

Чаще используются два варианта. В первом варианте на N входов данных N-разрядного ЦАП подается все входное слово целиком. Интерфейс такого ЦАП включает два регистра хранения и схему управления (рис. 15а). Два регистра хранения нужны, если пересылка входного кода в ЦАП и установка выходного аналогового сигнала, соответствующего этому коду, должны быть разделены во времени. Подача на вход асинхронного сброса CLR сигнал низкого уровня приводит к обнулению первого регистра и, соответственно выходного напряжения ЦАП.

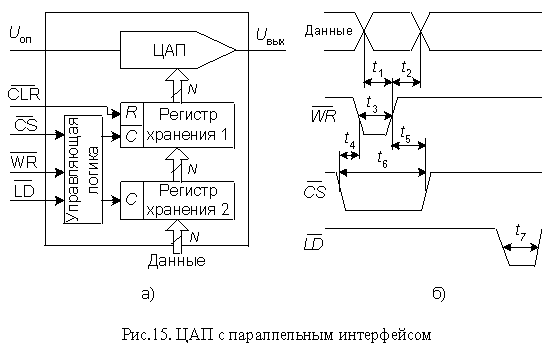

Пример блок-схемы подключения 12-ти разрядного ЦАП МАХ507 к 16-ти разрядному микропроцессору (МП) приведен на рис. 16. процессор посылает входной код в ЦАП как в ячейку памяти данных. Вначале с шины адрес/данные поступает адрес ЦАП, который фиксируется регистром по команде с выхода ALE микропроцессора и, после дешифрации, активизирует вход CS ЦАП. Вслед за этим МП подает на шину адрес/данные входной код ЦАП и затем сигнал записи на вход WR (см. рис. 15б).

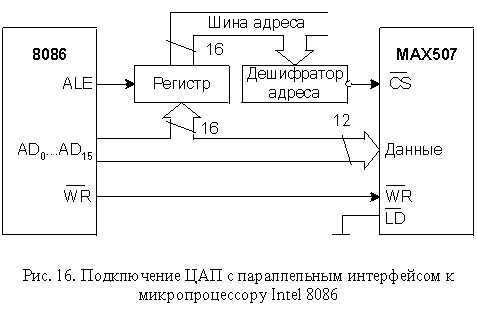

Для подключения многоразрядных ЦАП к восьмиразрядным микропроцессорам и микроконтроллерам используется второй вариант параллельного интерфейса. Он предусматривает наличие двух параллельных загрузочных регистров для приема младшего байта входного слова МБ и старшего байта - СБ (рис. 17). Пересылка байтов входного слова в загрузочные регистры может происходить в любой последовательности.