Проектирование узлов цифровой электронной техники

Проектирование узлов цифровой электронной техники

П79 Методические указания к выполнению домашних заданий по курсу электротехники и электроники /И.А. Ломов, В.Н. Атаманов, А.Б. Красовский и др. — М.: Изд-во МГТУ им. Н.Э. Баумана, 2002. - 48 с.: ил.

ISBN 5-7038-2062-6

Приведены варианты домашних заданий по проектированию комбинационного и последователъностного устройств цифровой электроники, а также по проектированию микропроцессорной системы. Представлены правила проектирования, справочные материалы и примеры выполнения заданий.

Для студентов механико-технологических специальностей.

Табл. 3. Ил. 21. Библиогр. 8 назв.

УДК 681.321

ББК 32.973.2

Рекомендуемые материалы

Игорь Александрович Ломов

Валерий Николаевич Атаманов

Александр Борисович Красовский

Анатолий Владимирович Лукашев

Виктор Семенович Семенов

ПРОЕКТИРОВАНИЕ УЗЛОВ ЦИФРОВОЙ ЭЛЕКТРОННОЙ ТЕХНИКИ

Редактор О.М. Королева

Корректор И.Е. Мелентьева

Подписано в печать 5.06.02. Формат 60x84/16. Бумага офсетная. Печ. л. 3,0.

Усл. печ. л. 2,79. Уч.-изд. л. 2,65. Тираж 1000 экз. Изд. № 61. Заказ 180т

Издательство МГТУ им. Н.Э. Баумана.

107005, Москва, 2-я Бауманская, 5.

ISBN 5-7038-2062-6. МГТУ им. Н.Э. Баумана, 2002

ВВЕДЕНИЕ

Важнейшим средством построения автоматов, управляющих различными техническими и технологическими процессами, является электронная техника. Большими возможностями обладает цифровая электронная техника, оперирующая с представлением информации в виде цифровых электрических сигналов.

Основу элементной базы современной цифровой электронной техники составляют интегральные микросхемы (ИС) — типовые узлы, обладающие определенными функциональными свойствами. Такая элементная база определяет подход к разработке электронных устройств, как к совокупности отдельных функциональных узлов.

Рассматриваемые в домашних заданиях комбинационное и последовательностное устройства на ИС малой и средней степени интеграции, а также микропроцессорная система являются основными типами объединения микросхем, отвечающих функциональным потребностям автоматов управления процессами.

Цель выполнения домашних заданий — ознакомление на практике с проектированием типовых устройств цифровой электронной техники. В работе представлены данные из каталогов для цифровых микросхем, приведены правила выполнения работ по проектированию и основные требования к оформлению конструкторской документации.

Третье домашнее задание заключается в проектировании микропроцессорной системы в программной ее части. Система должна обладать функциональными свойствами, заданными в первом и втором заданиях.

1. ЗАДАНИЯ

Задание 1. Спроектировать комбинационное устройство цифровой электронной техники для автомата управления технологической операцией.

На вход устройства поступают однозарядные сигналы A3, X2, XI от датчиков. На выходе устройства формируется сигнал Р, используемый для управления некоторым исполнительным механизмом. Значение Р =1 соответствует сочетаниям входных сигналов Х3, X2, XI, десятичные коды которых указаны в приложении (таблицы вариантов заданий). Для остальных сочетаний Р = 0.

При выполнении задания необходимо:

1. Изобразить проектируемое устройство как функциональный блок, указать входные и выходные сигналы. Составить таблицу истинности связи сигналов. Записать соответствующее логическое уравнение в совершенной дизъюнктивной нормальной форме (СДНФ).

2. Минимизировать логическое уравнение. Рассчитать по этому уравнению значение Р для всех сочетаний входных сигналов. Изобразить логическую схему проектируемого устройства.

3. Перевести минимизированное уравнение в базис И—НЕ. На основе этого уравнения построить схему электрическую принципиальную.

4. Определить быстродействие проектируемого устройства.

5. Разработать печатную плату и выполнить ее чертеж.

Задание 2. Спроектировать последовательностное устройство цифровой электронной техники для автомата управления технологическим процессом.

Последовательностное устройство — счетчик с произвольным порядком счета. На его вход сначала подается сигнал начальной установки НУ, затем импульсы С, переводящие счетчик в последующие состояния. Выходными сигналами устройства являются Q3, Q2 и Q1. Их значения определяют положение (включенное и отключенное) трех органов производственного автомата на каждом такте выполнения технологической операции.

Последовательность сочетаний сигналов Q3, Q2, QI как десятичных кодов задана в таблицах вариантов заданий. Первое сочетание должно устанавливаться после сигнала начальной установки.

При выполнении задания необходимо:

1. Изобразить проектируемое устройство как функциональный блок, указать входные и выходные сигналы. Составить таблицу состояний проектируемого устройства, в которой будут представлены входные и выходные сигналы. Обосновать количество необходимых для построения триггеров JK или D, как указано в таблицах вариантов заданий.

2. Выполнить проектирование, для чего построить таблицу переходов счетчика и таблицу управляющих сигналов триггеров. Осуществить минимизацию для построения комбинационных схем управления триггерами.

3. Записать уравнения функционирования счетчика.

4. Рассчитать по уравнениям и представить в таблице значения входных и выходных сигналив триггеров после сигнала начальной установки и всех заданных импульсов перехода к последующим состояниям. Построить соответствующие графики.

5. Изготовить комплект конструкторской документации на проектируемое устройство как на сборочную единицу: спецификация, сборочный чертеж, схема электрическая принципиальная, чертеж платы.

Задание 3.Спроектировать микропроцессорную систему, реализующую функциональные свойства комбинационного и последовательностного устройств, согласно заданиям 1 и 2.

Программу выполнения команд микропроцессором построить по следующему алгоритму. Сигнал НУ принять в качестве сигнала начала выполнения программы. При начальной инициализации в микропроцессорной системе подать на выход исходный сигнал — слово Q. Далее в бесконечном цикле опрашивать входные сигналы X, компиляцией минимизированного логического уравнения вырабатывать сигнал Р и подать его на выход.

Прием сигнала С (см. задание 2) осуществить как прием запроса на прерывание. Если сигнал С установлен, то интерпретацией выдать очередное сочетание сигналов Q по таблице состояний. После выполнения последнего сочетания Q остановить микропроцессор.

При выполнении задания необходимо:

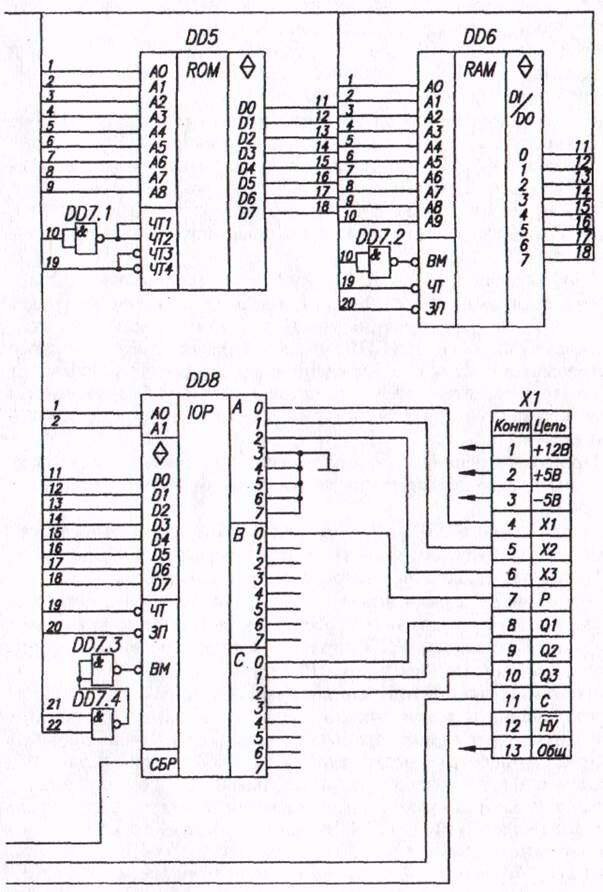

1. Изобразить условное обозначение микропроцессорной системы как функционального блока, распределив сигналы НУ, С, X. Р и Q по входам в микропроцессор и портам ввода-вывода. Составить таблицу истинности связи Р(Х) и таблицу состояний сигналов Q.

Указать необходимую для выполнения задания конфигурацию микропроцессорной системы: какие БИС должны в нее входить.

Записать распределение каналов А, Б и С БИС КР580ВВ55 как портов для ввода или вывода. Указать используемые биты для сигналов X, Р, Q.

Записать распределение адресов в микропроцессорной системе для постоянной и оперативной памяти.

Объявить дно стековой области памяти. Указать регистр микропроцессора, в котором будет осуществляться счет состояний выходных сигналов Q.

Все эти принятые решения отразить в алгоритме при инициализации микропроцессорной системы.

2. Составить алгоритм команд микропроцессора для выполнения заданного исходного алгоритма.

3. Записать программу на языке ассемблера. Выполнить ее трансляцию в коды команд.

4. Рассчитать быстродействие выработки сигнала Р(Х) и выдачи сигналов Q после приема запроса на прерывание.

5. Начертить схему электрическую принципиальную микропроцессорной системы.

6. Составить таблицу кодирования ППЗУ. Указать объем программы в байтах.

2. ПРАВИЛА ВЫПОЛНЕНИЯ ЭЛЕКТРИЧЕСКОЙ СХЕМЫ

Электрические схемы (их несколько видов) определены ГОСТ 2.701—84. Схема электрическая принципиальная включает в себя все применяемые в рассматриваемом устройстве электрические элементы и линии связи между ними. Правила ее выполнения описаны в ГОСТ 2.702-75. Электрические схемы для устройства цифровой электронной техники, кроме того, представлены в ГОСТ 2.751-73.

Выполнение схемы электрической принципиальной завершает этап электротехнического проектирования и служит основой для составления конструкторской документации на проектируемое изделие.

В электрической схеме применяемые изделия указывают в условных графических обозначениях (УГО). Если они для включенного и отключенного состояний различны, то в схеме их указывают для отключенного состояния. Условные графические обозначения элементов и их размеры определены стандартами ЕСКД; УГО изделий цифровой электронной техники — ГОСТ 2.743—82. Некоторые из них приведены в табл. 1.

Таблица 1

Условные графические изображения

| Обозначение | Наименование | ГОСТ |

| 1 | 2 | 3 |

|

| Логические элементы и интегральные мик- росхемы | 2.743-82 |

|

| Указатели выводов Прямой статический Инверсный статический Вход управления по Вход управления по Вывод, не несущий логической информации | 2.743-82 |

|

| Линия групповой электрической связи | 2.751-73 |

Допускается все обозначения пропорционально уменьшать или увеличивать, поворачивать на угол 90° или изображать зеркально повернутым по отношению к изображению, приведенному в стандарте.

Всем элементам схемы присваивают позиционные обозначения по ГОСТ 2.710—81. Например, R — резистор, С — конденсатор, S— ключ, X— разъем, V— полупроводниковый прибор, DA — микросхема аналоговая, DD — микросхема цифровая, логическая. Позиционное обозначение указывает на вид элемента и содержит его порядковый номер в схеме, например DD5.

Порядковые номера присваивают, начиная с единицы, последовательно для элементов преимущественно слева направо и сверху вниз. Позиционные обозначения проставляют на схеме около условного обозначения элемента над ним или с правой стороны.

Линии связи между элементами должны состоять, как правило, из горизонтальных и вертикальных отрезков с расстоянием между ними не менее 3 мм. Количество изломов и пересечений должно быть минимальным. Рекомендуемая толщина линий связи и графических обозначений составляет 0,3 — 0,4 мм.

Рис. 1

Рис. 2

Если линии связи затрудняют чтение схемы, их можно оборвать, закончив стрелкой. При этом необходимо указать обозначение или наименование, присвоенное этой линии, или вывода элемента.

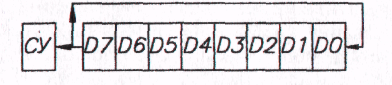

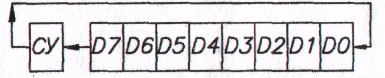

При изображении схем цифровой электронной техники по ГОСТ 2.751—73 используются линии групповой связи. Они обозначают группу линий связи, не соединенных между собой электрически. Эти линии выполняют вдвое толще одиночных линий

связи. Каждой линии, входящей в линию групповой связи, на обоих концах, а при разветвлении на всех концах, присваивают одинаковый номер.

Все линии схемы подразумеваются как входные и выходные. Для схемы в целом входные линии изображают с левой стороны листа или сверху; выходные — на правой стороне или внизу. Для элементов преимущественно входные — слева, выходные — справа.

Условные графические обозначения элементов цифровых электронных устройств и обозначения их выводов приведены в табл. 1. Примеры изображения их по каталогу представлены на рис. 1 и 2.

Все надписи на чертеже схемы, на линиях связи, около условных графических обозначений и внутри них выполняют основным шрифтом по ГОСТ 2.304-81.

Схема электрическая принципиальная должна сопровождаться перечнем элементов по ГОСТ 2.702—75. При большом числе элементов перечень элементов представляет собой текстовый документ. Перечень элементов можно указывать в виде таблицы на самом чертеже схемы электрической принципиальной. Часто это делают как сопроводительную надпись к чертежу схемы внизу или справа. В перечне элементов указывают позиционное обозначение, номер по каталогу и наименование. Если этих элементов два и более, указывают количество элементов.

3. ЭЛЕМЕНТНАЯ БАЗА

При проектировании устройств промышленной автоматики наиболее часто применяют микросхемы ТТЛ серии 155. Основные электрические параметры микросхем ТТЛ: высокий уровень сигнала — в интервале значений от 2,4 до 5,0 В, низкий — не более 0,4 В. Входной ток низкого уровня составляет +1,6 мА, высокого —0,04 мА. Выходной ток низкого уровня до —1,6 мА, высокого уровня — не определен. Коэффициент разветвления по выходу равен 10. Потребляемая мощность Рпотр, микросхемами указана в табл. 2. Напряжение питания составляет 5,0 В ±10 %. Время задержки t зр прохождения фронта сигнала через один элемент соответствующих микросхем также указано в табл. 2.

Таблица 2

Потребляемая мощность и время задержки

распространения сигнала ИС

| Параметр | ЛИ1 | ЛН1 | ЛЛ1 | ЛА1 | ЛЕ1 | ЛА2 | ЛАЗ | ЛА4 |

| Рпотр , мВт tзр , НС | --- 27 | т 22 | --- 22 | --- 27 | --- 22 | 26 33 | 110 29 | 80 29 |

| Параметр | ЛЕ4 | ЛП5 | ЛР1 | ЛР4 | ТМ2 | ТМ8 | ТВ1 | ТВ15 |

| Рпотр ,мВт tзр ,HC | --- 22 | 262 30 | 73 22 | 53 22 | 150 60 | --- 35 | 100 60 | --- 60 |

Микросхемы серии 155: ЛА1, ЛА2, ЛАЗ, ЛА4, ЛИ1, ЛЛ1, ЛЕ1, ЛЕ4, ЛН2, ЛП5, ЛР1, ЛР4, ТМ2, ТВ1 выполняют в четырнадцати-выводном корпусе 201.14. Выводы ИС нумеруют относительно ключа - выемки в корпусе; на виде сверху - против часовой стрелки. Чертеж корпуса 201.14 приведен на рис. 3.

Рис. 3

Напряжение питания +5 В подключают к выводу 14. Вывод 7 является общим как для минуса напряжения питания, так и для всех напряжений передачи сигналов.

Микросхемы ТМ8 и ТВ 15 выполнены в шестнадцативыводном корпусе 201.16: 16 — вывод +5 В, 8 — общий.

Для электрического соединения элементов, расположенных на печатной плате, с внешними устройствами применяют соединители, которые также являются стандартными элементами.

|

|

При выполнении заданий рекомендуется использовать соединитель РМ-В-вилка, устанавливаемый на плате. Его внутренние выводы располагаются в отверстиях платы под корпусом соединителя. Шаг равен 2,5 мм (рис. 4).

4. ПЕЧАТНАЯ ПЛАТА

| Рис. 4 |

Основным конструкционным узлом электронных приборов и устройств является плата. Термины по печатным платам определены ГОСТ 20406-75. Общие технические условия описаны в ГОСТ 23752-79. Печатная плата как конструкция — это пластина с установленными на ней микросхемами, резисторами, соединителями и др. Их

выводы соединяются между собой проводниковыми дорожками в соответствии со схемой электрической принципиальной.

Печатная плата как деталь — это пластина изолирующего материала с отверстиями под устанавливаемые элементы. Размеры между отверстиями кратные шагу выводов микросхем. Отверстия располагаются в центре контактных площадок, которые, как правило, имеют круглую форму. На обеих сторонах платы располагаются удерживающиеся на клею медные проводниковые дорожки. Они соединяют эти контактные площадки между собой по электрической схеме.

Технологически процесс изготовления печатной платы — детали заключается в обработке исходной изоляционной пластины с нанесенными по обеим сторонам сплошными медными листами. Машинным способом на медные поверхности по конфигурации площадок и дорожек наносится защитный слой краски. Далее пластина проходит травление в растворе кислоты. При этом вся медь, кроме защищенной краской, переходит в раствор. В дальнейшем краска удаляется и сверлением выполняются отверстия.

Существуют и другие конструкции и технологии изготовления плат. Сборочная операция изготовления платы-конструкции заключается в установке элементов, установке проводников в переходные отверстия с одной стороны на другую и соединении пайкой их выводов с контактными площадками.

5. КОНСТРУКТОРСКАЯ ДОКУМЕНТАЦИЯ

Комплект конструкторской документации на плату как сборочную единицу должен отвечать требованиям ЕСКД.

На стадии разработки рабочей документации обязательными по ГОСТ 2.102.68 являются документы: чертежи деталей, сборочный чертеж и спецификация. Чертеж схемы электрической принципиальной включают в комплект при проектировании устройств, имеющих электрическую часть, как это предусмотрено заданиями.

Основные правила выполнения чертежей печатных плат определены ГОСТ 2.417-78.

Размеры каждой стороны печатной платы по ГОСТ 10317—79 должны быть кратными: 2,5 мм при длине до 100 мм; 5 мм при длине до 350 мм; 10 мм при длине до 470 мм. Соотношение размеров сторон печатной платы должно быть не более 3:1. Допуски на линейные размеры предусматривают по ГОСТ 25346—82 и ГОСТ 25347—82. Соединитель может находиться на длинной или короткой стороне.

Чертеж рекомендуется выполнять в масштабе 2:1. Для двухсторонних плат указывают две проекции. Одну из них помечают как сторону расположения элементов соответствующей надписью над изображением. Для указания размещений отверстий и проводниковых дорожек поле печатной платы на каждой из проекций покрывают тонкими линиями прямоугольной координатной сетки. Шаг равен 2,5 мм. Линии нумеруют от левого нижнего угла стороны расположения элементов.

Отверстия располагают только в узлах координатной сетки. Ориентировка микросхем горизонтальная или вертикальная.

На оборотной стороне контактную площадку первого вывода микросхемы выполняют, например, прямоугольной формы, в отличие от остальных, которые имеют круглую форму.

Около расположения микросхем указывают их наименования по схеме электрической принципиальной. Надписи наносят краской, как и дорожки при изготовлении платы.

Проводниковые дорожки в основном располагаются на оборотной стороне, преимущественно по линиям координатной сетки на свободном поле или под корпусами микросхем. Дорожки не могут пересекаться, но могут переходить с одной стороны на дру- гую. Для этого выполняется переходное отверстие с контактными площадками на обеих сторонах. Следует иметь в виду, что большинство соединителей имеет конструкцию, допускающую пайку только с обратной стороны корпуса. Для микросхем такого ограничения нет.

Чертеж печатной платы сопровождается записью технических требований:

1. Шаг координатной сетки.

2. Диаметр и количество отверстий. Если отверстия разных диаметров, то и на чертеже и при записи в технических требованиях их указывают в условном обозначении — частичным затушевыванием.

3. Способы выполнения надписей на плате по ГОСТ 2.417—78.

Примечание. Чертеж печатной платы по заданию 1 указан на рис. 9, задания 2 - на рис. 17, а и 17, б.

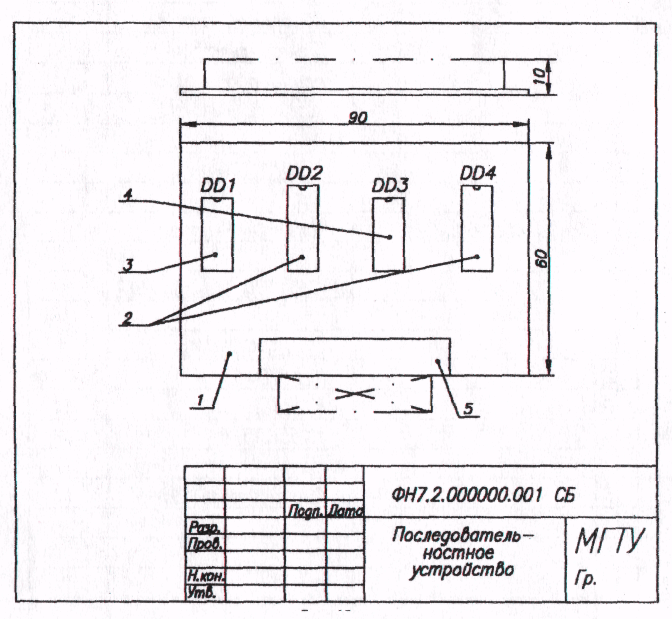

Сборочный чертеж на плату отражает взаимное расположение микросхем, соединителя и других возможных элементов. В изображениях микросхем указывают расположение ключа. Все элементы и печатная плата, как деталь, должны иметь указания позиций, наносимых вне поля изделия. Около элементов микросхем указывают их позиционные обозначения по схеме электрической принципиальной, предусмотренные в чертеже платы-детали.

На чертеже проставляют габаритные размеры.

Примечание. Сборочный чертеж по расчетам, приведенным в задании 2, показан на рис. 16.

Спецификация, как один из документов конструкторской документации, определена ГОСТ 2.108—68.

В графу "Поз" вносят позиции элементов и деталей сборочного чертежа.

В графу "Обозначение" вносят обозначения изделий и соответствующих им чертежей по ГОСТ 2.201—80. Они имеют буквенно-цифровой код с разделительными точками. Допустимо обозначение: ФН7.2. 000000.001, отражающее индекс кафедры "Электротехника и промышленная электроника", индекс читаемого курса и первый порядковый регистрационный номер. Обозначению сборочного чертежа присваивают индекс СБ, схемы электрической принципиальной — ЭЗ, спецификации — СП.

В графе "Примечания" указывают дополнительную информацию, в частности, позиционные обозначения по схеме электрической принципиальной.

Примечание. Пример выполнения спецификации по заданию 2 указан на рис.15.

6. ПРИМЕРЫ ОФОРМЛЕНИЯ ЗАДАНИЙ 1 и 2

Отчет по заданию должен быть выполнен в виде расчетно-пояснительной записки с этапами проектирования и содержать чертежи схем, конструкторскую документацию.

В записке необходимо указать текст задания, условно изобразить проектируемое устройство как функциональный блок с указанием входных и выходных сигналов. Записать таблицу связи этих сигналов. Далее следует представить описание этапов выполнения работы.

Задание 1. Спроектировать комбинационное устройство цифровой электронной техники для автомата управления технологической операцией.

На входы комбинационного устройства поступают входные сигналы от трех датчиков. На выходе формируется выходной сигнал Р, равный 1 при десятичных кодах входных величин 0, 2, 3, 7. При остальных кодах Р = 0.

1. Представление проектируемого устройства как функционального блока. Проектируемое комбинационное устройство как функциональный блок с указанием входных и выходных сигналов и таблица истинности их связи указаны на рис. 5.

Таблица

истинности

Рис. 5

Логическое уравнение, связывающее входные и выходные сигналы в СДНФ, имеет вид

(1)

(1)

2.Минимизация логического уравнения. Для выполнения тождественных преобразований, приводящих логическое уравнение в СДНФ к минимизированной дизъюнктивной нормальной форме (ДНФ), используют карту Карно — Вейча.

В карте по адресам ее ячеек расставляют нули и единицы из таблицы истинности. Соседние единицы объединяются. Объединения могут охватывать 2, 4 и 8 ячеек. Одна и та же единица может входить в несколько объединений. Чем объединений меньше и чем они крупнее, тем эффективней минимизация.

|

|

В минимизированное уравнение вместо элементарных конъюнкций СДНФ записываются конъюнкции адресов объединений и элементарные конъюнкции единиц, объединить которые не удалось.

Карта Карно — Вейча, соответствующая таблице истинности, показана на рис. 6.

Используя' карту, получим минимизированное логическое уравнение, описывавшее заданную логическую связь между входными и выходными сигналами. Оно оказывается в базисе НЕ, И, ИЛИ:

(2)

(2)

Рис. 6 Логическая схема, реализующая полученное минимизированное уравнение, приведена на рис. 7, а. Расчет значений выходных сигналов по минимизированному уравнению представлен на рис. 7, б.

Логическая схема Расчет Р(Х)

а б

Рис. 7

3. Построение схемы электрической принципиальной.

Устройство может выполняться на любых приведенных в каталогах электронной промышленности микросхемах. Желательно, чтобы их количество было минимальным и обеспечивало заданное функционирование устройства. При небольшом числе элементов в логической схеме такой результат дает перевод их в единый базис.

Выполним схему на основе уравнения в базисе И—НЕ.

Преобразуем минимизированное уравнение, вводя двойную инверсию и пользуясь теоремой де Моргана:

(3)

(3)

Схема электрическая принципиальная, реализующая преобразованное логическое уравнение в базисе И—НЕ, представлена на рис. 8.

Схема электрическая принципиальная

Рис. 8

4. Расчет быстродействия комбинационного устройства. Быстродействие проектируемого устройства оценивается временем задержки распространения фронта сигнала от входов до выхода. Оно зависит как от времени задержки сигнала в каждом элементе применяемых микросхем, так и от времени переходного процесса заряда — разряда емкости проводов связи между элементами. Указанное в табл. 2 время задержки для каждого элемента соответствующих микросхем определяет некоторое их конструктивное расположение на плате (эти значения ориентировочные).

Возможно различное число элементов в разных путях распространения сигнала от входов до выхода. В этом случае время задержки устройства оценивают суммой задержек на отдельных элементах по пути с наибольшим их числом. В проектируемом устройстве (см. рис. 8) входной сигнал проходит по линии, включающей в себя три последовательно соединенных логических элемента К155ЛАЗ, следовательно, можно записать

(4)

(4)

5. Выполнение чертежа печатной платы. Чертеж печатной платы, реализующей схему электрическую принципиальную, представлен на рис. 9.

Задание 2. Спроектировать последовательностное устройство — счетчик с произвольным порядком счета для использования в автомате управления технологическим процессом.

Входные сигналы: НУ — начальная установка и С — переход к очередному состоянию.

Выходные сигналы: Q3, Q2, Q1. Десятичные коды последовательности выходных сигналов Q равны: 1,0,3,2,6,7,5. Первый код указывает исходное состояние выходов.

Счетчик должен осуществлять циклический счет в соответствии с заданной последовательностью выходных сигналов.

1. Представление проектируемого устройства как функционального блока. Проектируемое последовательностное устройство как функциональный блок и заданная таблица состояний указаны на рис. 10.

Заданное устройство должно иметь семь состояний. Выбрать два триггера нельзя, так как они обеспечат только четыре состояния. Три триггера обеспечивают до восьми состояний. Выбираем для построения 3 JK триггера.

2. Проектирование с использованием табличного метода. Таблицу переходов счетчика строят на основе заданной таблицы состояний. В ней каждому состоянию сигналов Q3, Q2 и Q1в строку записывают их переходы к последующему состоянию.

Для заданной таблицы состояний (см. рис. 10) таблица переходов указана на рис. 11.

Таблица переходов позволяет построить таблицу управляющих сигналов, применяемых в проектируемом устройстве триггеров.

Сторона расположения элементов

Рис. 9

Таблица состояний

Рис. 10

Таблица переходов

Характ.табл. JK-mpuггepa Характ.табл. D-триггера

Таблица управляющих сигналов триггеров

Рис. 11

Для этого используют характеристические таблицы триггеров JK или D (см, рис. 11). Эти таблицы описывают свойства управляемости триггеров: какие необходимо подать управляющие сигналы, чтобы обеспечить необходимый переход. Звездочкой помечены сигналы 0 или 1, в любом случае обеспечивающие переход.

Таблица управляющих сигналов триггеров проектируемого счетчика также указана на рис. И. В ней вместо переходов таблицы записаны соответствующие управляющие сигналы, обеспечивающие эти переходы. Таблица управляющих сигналов является таблицей истинности комбинационных схем выработки сигналов J и К для каждого из триггеров по сигналам Q (см. рис. 11).

Для трех входных сигналов таблица истинности, а соответственно и карта Карно — Вейча должны иметь восемь строк и восемь ячеек. Не используемое в управлении автоматом состояние в картах для минимизации, в данном случае сочетание 100, также помечено звездочкой. Никогда не возникающее состояние можно записать как 1 и использовать его для более эффективной минимизации. Соответствующие карты указаны на рис. 12.

3. Представление уравнений функционирования счетчика:

|

| (5) |

Выбираем микросхемы триггеров К155ТВ15 — два, JK триггера. По результатам минимизации строим схему электрическую принципиальную (рис. 13). Так как она входит в комплект конструкторской документации, ее необходимо соответствующим образом оформить.

4. Расчет значений входных и выходных сигналов. Значения сигналов Q, J и К после сигнала начальной установки и по сигналам перехода к последующим состояниям рассчитаны по уравнениям функционирования счетчика. Результаты расчета сведены в таблицу и представлены на рис. 14. Соответствующие графики изображены на том же рисунке.

Быстродействие счетчика как время задержки от поступления на вход соответствующего фронта сигнала С до установления сигнала Q может быть рассчитано по данным табл. 2 и по схеме электрической принципиальной.

Рис. 12

Рис. 13

Сигнала Q,J,K no тактам

Рис. 14

В данном задании предполагается, что такты поступления сигнала С перехода к новому состоянию определяются интервалами времени, необходимыми для выполнения технологических операций в установке, т.е. составляют порядка единиц или десятков секунд. Они несоизмеримо больше времени задержки прохождения сигнала в электронном устройстве. Поэтому в графиках (см. рис. 14) время задержки принято равным нулю.

5.Комплект конструкторской документации включает в себя: спецификацию, сборочный чертеж, схему электрическую принципиальную и чертеж печатной платы. Спецификация для разработанного последовательностного устройства приведена на рис. 15; сборочный чертеж - на рис. 16; чертеж печатной платы — на рис. 17.

Рис. 15

Рис. 16

Сторона расположения элементов

Рис. 17, а

Рис. 17, б

7. УКАЗАНИЕ К ВЫПОЛНЕНИЮ ЗАДАНИЯ 3

Микропроцессорная система, выполняющая обработку сигналов, согласно заданиям 1 и 2, в целом как функциональный блок представлена на рис. 18. Таблица истинности Р(Х) определяет соответствующее минимизированное уравнение (2). Таблица последовательности состояний сигналов Q представлена на рис. 10.

Таблица Таблица

истинности состояний

Рис. 18

Задание 3 состоит в проектировании микропроцессорной системы в программной ее части. Составить программу — это записать последовательность команд для действий микропроцессора.

Нужно ввести через один из портов установленные внешними устройствами сигналы. Применяя пересылки, сдвиговые и логические операции выполнить в младшем разряде действия согласно уравнению (2). Полученный результат выдать через другой порт на выход. Такой подход к составлению программы называют компиляцией.

Можно в некоторую область памяти заранее записать таблицу выходных сигналов для всех сочетаний входных. Программу действия составить как нахождение необходимой строки этой таблицы по входному сигналу. Такой подход называют интерпретацией. Выяснить, какой подход лучше, можно по критериям быстродействия и объема программы.

Бесконечный цикл выполнения для микропроцессорных программ является основным. При этом можно ввести цикл ожидания прихода сигнала, разрешающего выполнить некоторые действия.

Перед написанием программы необходимо составить ее алгоритм. Вначале следует изобразить исходный алгоритм, в котором записать блоки задания — что нужно сделать. Далее его детализируют до уровня отдельных команд. Такой алгоритм уже указывает последовательность команд — как выполнить задание.

На основе алгоритма написать программу. Оптимальный вариант для данного задания — написать программу на языке ассемблера. Затем она транслируется в коды — байты команд.

Для расчета быстродействия при написании программы необходимо ввести графу, в которую нужно записывать количество тактов, необходимых микропроцессору на выполнение каждой команды.

С точки зрения программирующего, микропроцессор — это набор регистров и счетчиков. Для микропроцессора КРБ80ВМ80 — это восьмиразрядные регистры A, F, В, С, D, E, H, L, a PC — программный счетчик и SP — указатель стека являются шестнадцатиразрядными счетчиками (рис. 19). Действия над их содержимым определяются командами.

В списке команд этого микропроцессора их 244. Почти все действия выполняются в арифметико-логическом устройстве (АЛ У). Всеми операциями управляет первичный управляющий автомат (ПУА) в непрерывающемся переходе от выполнения одной команды к следующей. Составленную программу как последовательность байтов следует записывать в память. Если она неизменная, то ее байты записывают в постоянную память, выполненную на БИС ППЗУ. Такие микропроцессорные системы называют контроллерами.

После импульсного сигнала СБР программный счетчик обнуляется, т.е. PC = 0000H Начинается выполнение программы. Содержание PC появляется на магистрали адресов и сопровождается соответствующим сигналом чтения памяти от системного контроллера (рис. 20). Первый байт передается из БИС памяти в микропроцессор и выполняется.

В процессе выполнения команд при обработке каждого их байта кроме основных действий происходит увеличение содержания программного счетчика на единицу. Так подготовляется адрес для выборки следующего байта в двух- или трехбайтных командах или байта следующей команды. Выполняется линейный алгоритм построения программы.

Существуют команды занесения в PC адреса, указываемого в составе самой команды. Она оказывается в этом случае трехбайтной. По этим командам выполняются заданные алгоритмом переходы по программе, в частности организуются циклы.

Фиксированные, заранее известные адреса можно занести в PC командами RSTN, где N от 0 до 7. Эти команды однобайтовые. Их удобно использовать при прерываниях.

Прерывания инициируются внешним устройством, подающим на микропроцессор сигнал запроса прерывания (ЗПР). Приняв запрос на прерывание, микропроцессор после завершения выполнения текущей команды должен получить код команды RSTN. Выполняя ее, он перейдет к реализации фрагмента программы, обслуживающего это прерывание, который записан с соответствующего адреса памяти.

Необходимая команда RSTN подготовляется аппаратно. В алгоритме программы ее нет. В состав микропроцессорной системы вводится регистр прерывания, в котором записывается код этой команды. Приняв сигнал ЗПР, микропроцессор через системный контроллер сигналом подтверждения прерывания (ППР) выводит выход этого регистра из высокоомного состояния. Содержащийся в нем код поступает по магистрали данных в микропроцессор и команда выполняется.

Программа обслуживания прерываний завершается командой RET, возвращающей микропроцессор к выполнению прерванной программы.

После сигнала СБР и приема сигнала ЗПР прерывания запрещены, т.е. не будут восприняты микропроцессором. Существуют команды, разрешающие и запрещающие прерывания.

Условные ветвления в алгоритме программы — это переходы по указываемому в команде адресу в соответствии со значением ДА флага. По значению НЕТ команда условного перехода игнорируется, т.е. выполняется только PC — PC + 1.

Флагами являются отдельные разряды регистра флагов F. Флаги устанавливаются при выполнении команд, влияющих на них. Каждый из флагов фиксирует значение одного из признаков выходного сигнала АЛУ после выполнения команды (см. рис. 19). Например, флаг Zнулевого результата равен единице, если выходной сигнал данных нулевой по всем восьми разрядам, и Z= 0, если сигнал не нулевой. Флаг СУ является по существу девятым разрядом выходного сигнала АЛУ. Его значение СУ = 1 указывает на переполнение разрядной сетки при выполнении операции суммирования, либо принимает значение бита, попадающего в него при выполнении сдвиговой операции. Если команда не влияет на флаги, то их значения сохраняются.

Рис. 19

Рис. 20, а

Рис. 20, б

Запись данных в оперативную память микропроцессорной системы и их считывание может осуществляться командами с непосредственным указанием любого из адресов ОЗУ. Для обращения к оперативной памяти также можно использовать стековую ее организацию. Стековая область памяти — это, как правило, последние адреса реально используемых БИС оперативной памяти. Запись и считывание в эту область происходит по текущему содержанию указателя стека SP.

Такое использование оперативной памяти организует доступ к ячейкам памяти при записи и считывании только по очереди. Реализуется принцип: первым вошел при записи, последним выйдешь при считывании. Это программно более компактно, а при выполнении программы реализуется с большим быстродействием.

Каждая команда характеризуется: кодом команды — 1 байт (первый байт двух- или трехбайтных команд), общим количеством байт в команде, мнемоническим описанием команды, являющимся ее названием, описанием выполняемых по этой команде действий, влиянием на флаги и количеством тактов выполнения команды. При выполнении команды ее код, полученный микропроцессором по магистрали данных, устанавливается на входе первичного управляющего автомата. По тактам с частотой 2 МГц этот автомат выдает сигналы, управляющие всеми операциями в микропроцессоре. При этом выполняются действия, определенные этой командой.

Схема электрическая принципиальная микропроцессорной системы на основе комплекта БИС КР580 в конфигурации, соответствующей поставленной в задании задаче управления, представлена на рис. 20.

БИС ГФ24 - генератор, ВМ80 - микропроцессор, ВК38 - системный контроллер образуют процессор управляющей системы. Реальные возможности такого процессора шире требуемых для выполнения задания, поэтому есть неиспользуемые выводы этих БИС. Они на схеме не указаны.

В условных обозначениях всех микросхем не указаны номера выводов.

Память в системе образуется двумя БИС. Постоянная память для записи программ выполнена на БИС КР556РТ17 — ППЗУ с пережигаемыми перемычками, организация 512x8. Оперативная память для записи и считывания промежуточных данных выполнена на БИС КР535РУ8 - ОЗУ с организацией 1Кх8. Для ее активизации в качестве сигнала ВМ используется бит адресного сигнала А9.

RLC

RAL

RRC

RAR

Рис. 21

Для ввода и вывода данных из микропроцессорной системы используется БИС ВВ55 — интерфейс ввода-вывода. После включения напряжения питания по сигналу СБР все внутренние регистры этой БИС обнуляются. Для начала работы по передаче данных ее каналы А, В и С, обладающие свойствами двунаправленных регистров, необходимо настроить на направление передачи. Занесение в РУС — регистр управляющего слова (порт 03) слова данных 98Я настраивают канал А (порт 00) на ввод, канал В (порт 01) на вывод, младшие четыре бита канала С (порт 02) на вывод, старшие — на ввод.

При обращении к ВВ55 по адресному сигналу и соответствующим сигналам ЧТВВ или ЗПВВ она активизируется сигналом ВМ, образуемым их конъюнкцией.

В качестве регистра прерывания использован регистр ИР82. На его входе, как указано на рис. 21, образован код команды RST4. В каждом конкретном случае составления программы необходимо выбрать наиболее подходящую команду RSTN и в схеме указать образование ее кода.

Внешний сигнал начальной установки воспринимается как СБРВ — входной сброс, поступающий на генератор. В микропроцессор он попадает синхронизированным с тактовыми сигналами.

Таблица кодирования ППЗУ — это перечень полученных в результате трансляции байтов команд с указанием адресов, по которым они располагаются.

Таблица формируется по строкам, указывающим адрес первого в строке байта, затем самих байтов, которых в строке 16. Эти адреса, так же как и байты, выражаются числами в шестнадцатеричной системе счета: 0000, 0010, 0020, 0030 и т.д.

Объем программы в байтах указывается десятичным числом.

8. КОМАНДЫ МИКРОПРОЦЕССОРА КР580ВМ80

При описании команд используются обозначения (табл. 3):

N(**) — порт ввода или вывода, фактически адресный сигнал, 1 байт;

D8 — операнд двухбайтной команды, записывается программирующим как некоторое число, 1 байт;

D16 — операнд трехбайтной команды, записывается программирующим;

D8CT — старший байт;

D8MJI — младший байт;

ADR — адрес в составе трехбайтной команды, 2 байта;

R — регистр;

RP — регистровая пара ВС, DE, HL;

PSW — слово состояния, фактически регистровая пара AF;

M(RP) — ячейка памяти микропроцессорной системы, адрес которой находится в RP.

Таблица 3

ОПИСАНИЕ КОМАНД

Продолжение табл. 3

Продолжение табл. 3

Продолжение табл. 3

Окончание табл. 3

| Код | Байты | Мнемоника | Действия | Флаги | Такты |

| F3 00 76 | 1 1 1 | DI NOP HLT | Прерывания запрещены Нет операции, PC=PC+1 Останов | НЕТ НЕТ НЕТ | 4 4 4 |

Приложение

Варианты заданий

Задание 1 на проектирование комбинационного устройства представлено набором цифр. Его выходной сигнал Р равен 1 при подаче на вход сигналов Х3, X1, X1, сочетание которых является двоичным кодом заданных цифр. Для остальных сочетаний входных сигналов Р = 0.

Задание 2 на проектирование последовательностного устройства также задано набором цифр и указанием, на основе какого типа триггера выполнять проектирование. Выходных сигналов устройства три: Q3, Q1, Q1. Цифры задания указывают последовательность значений этих сигналов при переходах по сигналам С.

Вариант 1

| № п/п | Задание 1. Проектирование комбинационного устройства | Задание 2. Проектирование последовательностного устройства | |

| 1 2 3 4 5 | 0,3,6,7 0,1,3,6 0,1,3,4,7 1,3,4,7 1,2,3,5,6 | 6,1,3,0,5 4,2,3,6,7,5 6,4,3,0,2,1,7 0,2,4,3,1,6,5,7 2,4,1,3,5,7,6,0 | D D JK JK JK |

| 6 7 8 9 10 | 0,1,3,6,7 1,2,3,4 0,1,2,7 0,2,3,5,7 1,3,5,6 | 1,7,4,6,0,3,2 1,4,3,7,6,5,0,2 4,3,1,6,5,7,2 6,1,3,4,2,7 3,4,5,2,0,1,7,6 | D JK JK D JK |

| 11 12 13 14 15 | 0,2,3,4,7 0,1,2,6,7 2,4,5,7 0,3,4,5 1,2,5,6,7 | 6,1,7,2,3 3,5,2,1,0,7,4,6 7,6,4,5,3,1 2,4,3,7,6,5,1,0 5,6,3,2,0,1,7,7 | D JK D JK JK |

| 16 17 18 19 20 | 0,3,5,7 1,3,4,6,7 1,2,3,4,5 0,1,5,6 1,2,4,5 | 5,2,7,1,3,6 1,7,3,6,4,5,0,2 7,6,3,5,4,2 5,6,0,3,7 7,4,3,5,1,0,2,6 | D JK D D JK |

| 21 22 23 24 25 | 1,3,4,5,6 1,2,5,7 0,1,3,4,6 0,2,3,4,5 0,4,5,6 | 3,4,5,0,7,6 4,5,6,3,2,1,7 1,3,2,5,7,6,0,4 5,3,6,1,0,2,7,4 7,5,6,3,4,0,1,2 | D JK JK JK JK |

Вариант 2

| № п/п | Задание 1. Проектирование комбинационного устройства | Задание 2. Проектирование последовательностного устройства | |

| 1 2 3 4 5 | 1,2,6,7 2,3,4,7 1,2,3,4,6 0,2,5,7 1,2,4,5,6 | 3,0,2,1,6,4,7 4,3,0,6,1,7 7,4,6,3,5,2,1 2,3,1,4,6,7,5,0 7,4,5,3,6,1 | JK D D JK D |

| 6 7 8 9 10 | 2,3,4,5,6 0,2,3,5 0,5,6,7 0,1,2,5,6 0,2,4,7 | 4,3,1,6,5,7,0,2 4,5,2,1,7 3,4,2,7,5,6,0,1 6,2,4,1,3,5,7 4,5,3,1,0,2,7,6 | JK D JK D JK |

| 11 12 13 14 15 | 0,3,4,5,7 0,1,4,6,7 3,4,5,6 2,3,5,6 0,2,4,5,7 | 1,6,5,7,4,3,2 6,0,3,1,2,7 3,5,4,2,1,0,7,6 0,2,1,4,3,7,6,5 5,6,3,4,0,1,2,7 | JK D JK D JK |

| 16 17 18 19 20 | 1,2,4,6 0,1,2,5,6 2,3,4,5,7 0,1,4,7 1,4,6,7 | 4,3,7,6,5,2,0,1 6,3,2,5,4 5,7,6,0,4,1,3,2 7,6,3,4,5,2,0 2,7,5,6,0,4,3,1 | JK D JK D JK |

| 21 22 23 24 25 | 0,3,4,6,7 0,3,4,6 0,2,5,6,7 0,1,5,6,7 0,2,3,6 | 7,4,2,1,3,6 4,7,0,2,1,5 7,4,6,5,3,0,1,2 1,7,4,5,6,3,2,0 5,0,4,3,2,1,7,6 | D D JK JK JK |

Вариант 3

| № п/п | Задание 1. Проектирование комбинационного устройства | Задание 2. Проектирование последователъностного устройства | |

| 1 2 3 4 5 | 2,4,5,7 0,5,6,7 0,2,4,5,7 0,2,4,7 2,3,4,5,7 | 4,3,5,1,0,7,6,2 5,2,3,1,4,6,7 1,2,7,4,6,5,0 5,2,0,1,7,6,3,4 4,3,2,1,7,6,5 | JK D D JK D |

| 6 7 8 9 10 | 0,1,2,4 1,3,4,6,7 0,1,4,6,7 0,3,6,7 0,1,3,6 | 2,1,0,7,6,3,5,4 6,1,3,4,2,7 5,6,0,3,7,2 2,1,6,4,3,0,2,5 2,7,5,6,3,4,0,1 | JK D D JK JK |

| 11 12 13 14 15 | 1,3,4,5,6 1,3,4,7 1,2,3,5,6 0,1,3,6,7 1,2,3,4 | 5,6,4,3,0,2,1,7 4,3,5,1,2,0,7,6 5,6,7,0,1,3 6,5,7,4,3,1 7,6,4,5,3,1,0,2 | JK JK D D JK |

| 16 17 18 19 20 | 2,3,4,7 0,1,2,5,6 1,3,5,6 0,1,3,4,6 0,1,5,6,7 | 0,2,4,3,1,6,5,7 6,7,5,0,4,2,1,3 4,5,2,1,0,3 3,1,2,7,5,6,0,4 3,0,1,2,7,4,6,5 | JK JK D JK JK |

| 21 22 23 24 25 | 1,2,6,6 1,2,4,5 0,2,3,5,7 0,3,5,7 0,1,2,6,7 | 6,2,4,1,3,5,7 5,7,0,4,2,3,1,6 3,6,4,5,0,2,1,7 5,2,1,4,3,7,6 6,1,30,2,4 | D JK JK D D |

Вариант 4

| № п/п | Задание 1. Проектирование комбинационного устройства | Задание 2. Проектирование последователъностного устройства | |

| 1 2 3 4 5 | 0,2,3,5 0,1,2,7 1,3,5,6 1,2,5,7 1,2,5,6,7 | 7,6,3,5,2,0,1 4,3,7,6,5,2,0,1 7,4,5,6,3,2 1,7,4,6,0,3 7,4,6,3,5,2,1,0 | D JK D D JK |

| 6 7 8 9 10 | 0,3,4,5,7 1,2,3,4,5 0,1,3,5 0,1,4,7 0,3,4,5 | 4,6,7,5,0,2,3,1 6,4,1,3,2,5 1,6,4,4,0,2 6,1,7,2,3 3,5,7,6,0,2,4,1 | JK D D D JK |

| 11 12 13 14 15 | ОД,3,4,7 0,3,4,6 0,2,5,6,7 0,2,3,4,5 0,1,5,6 | 5,6,0,3,4,2,7 6,5,7,4,3,1 1,0,2,7,6,4,5,3 5,2,7,1,0,4 3,2,1,7,6,5,0,4 | IK D JK D JK |

| 16 17 18 19 20 | 2,3,5,6 0,3,4,6,7 0,2,5,7 0,2,3,4,7 2,3,4,5,6 | 4,6,5,3,0,1,2,7 7,4,5,3,6,1,0,2 3,4,1,5,6,7,0,2 3,4,5,0,1,7 0,4,3,1,2,7,5,6 | JK JK JK D JK |

| 21 22 23 24 25 | 3,4,5,6 1,4,6,7 1,2,3,4,6 1,2,4,6 0,1,2,5,7 | 1,2,3,5,6,7,0,4 4,6,3,5,1,2,0,7 0,4,2,1,3,6,7,5 4,3,0,6,2,7 2,3,1,6,5,7,0,4 | JK JK JK D JK |

Вариант 5

| № п/п | Задание 1. Проектирование комбинационного устройства | Задание 2. Проектирование последо-вательностного устройства | |

| 1 2 3 4 5 | 1,3,4,7 1,2,3,5,6 1,2,4,5,6 0,3,6,7 0,1,3,5 | 3,7,6,5,2,4,0,1 6,5,7,0,2,4,3,1 7,4,6,5,3,0 6,5,0,2,1,4,3,7 6,0,3,1,5,2 | JK JK D JK D |

| 6 7 8 9 10 | 0,1,3,4,7 0,2,4,7 0,2,3,4,7 0,2,3,6 0,1,4,7 | 7,6,3,5,4,2,1,0 5,1,0,7,4,3,2,6 1,7,5,6,4,3,0,2 0,4,3,2,1,7,6,5 6,3,2,5,0,4 | JK JK JK JK D |

| 11 12 13 14 15 | 0,3,4,5 0,2,4,5,7 1,2,5,7 0,1,3,4,6 0,2,3,4,5 | 2,0,7,6,4,3,5,1 7,5,6,3,4,0,1 4,3,0,2,1,6,7,5 1,0,2,7,4,5,3,6 4,7,0,2,1,3 | JK D JK JK D |

| 16 17 18 19 20 | 0,1,2,6,7 0,1,2,4 1,2,3,4 1,2,4,5 0,4,5,6 | 7,4,5,6,3,2,0 2,1,3,6,7,5,0,4 6,4,1,3,2,5 1,0,7,4,6,3,5,2 1,2,7,4,2,5 | D JK D JK D |

| 21 22 23 24 25 | 0,3,4,6 0,1,4,6,7 2,3,4,5,6 1,3,4,5,6 0,1,2,5,6 | 5,6,7,0,2,3,4,1 7,4,3,1,2,6,5 5,6,7,0,4,1,2,3 1,2,0,7,4,6,3,5 5,6,7,0,4,1 | D D JK JK D |

Список рекомендуемой литературы

1. Сигорский В.П. Математический аппарат инженера. Киев: Техника, 1975. 766 с.

2. Интегральные микросхемы: Справочник /Б.В. Тарабрин, С.В. Якубовский, Н.А. Барканов и др.; Под ред. Б.В. Тарабрина.М.: Энергоатомиздат, 1985. 528 с.

Ещё посмотрите лекцию "26 Японцы в париже" по этой теме.

3. Зельдин Е.А. Цифровые интегральные микросхемы в информационно-измерительной аппаратуре. Л.: Энергоатомиздат, 1986. 280 с.

4. Разработка и оформление конструкторской документации: Справочник РЭА /Э.Т. Романычева, А.К. Иванова, А.С. Куликов и др.; Под ред. Э.Т. Романычевой. М.: Радио и связь, 1989.448 с.

5. Токхейм Р. Основы цифровой электроники: Пер. с англ. М.: Мир, 1988. 392 с.

6. Каган Б.М., Сташин В.В. Основы проектирования микропроцессорных устройств автоматики. М.: Энергоатомиздат, 1987. 304с.

7. Щелкунов Н.Н., Дианов А.П. Микропроцессорные средства и системы. М.: Радио и связь, 1989. 288 с.

8.ЛевентальЛ., Сейвилл У. Программирование на языке ассемблера: Пер. с англ. М.: Радио и связь, 1987. 448 с.