Программируемые пользователем вентильные матрицы

· Курс «Информационные технологии

· в проектировании ЭВС»

· Лекция №3

· «Элементная база электронных устройств и систем»

3. FPGA — программируемые пользователем вентильные матрицы

3.1. Основные сведения

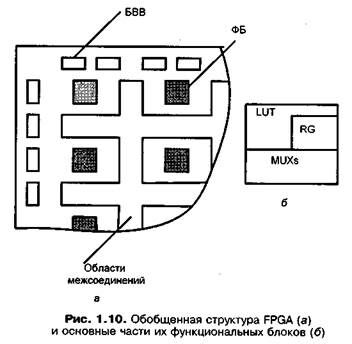

В наиболее типичном варианте FPGA представляет собою микросхему высокого уровня интеграции, содержащую во внутренней области матрицу идентичных функциональных блоков и систему их межсоединений, размещенную между строками и столбцами матрицы, а в периферийной области — блоки ввода/вывода (рис. 1.10, а). Кроме этого варианта существуют FPGA, в которых функциональные блоки расположены по строкам (строковые FPGA), однако рассматривать эти варианты отдельно нет оснований, поскольку существенные черты FPGA остаются одинаковыми для обоих вариантов.

Рекомендуемые материалы

Все части FPGA (функциональные блоки (ФБ), система межсоединений и блоки ввода/вывода БВВ) являются конфигурируемыми или реконфигурируемыми, причем (в отличие от БМК) средствами самих пользователей.

Перечисленные части — основа FPGA. Кроме них современные варианты FPGA, как правило, оснащены дополнительными средствами для автоподстройки задержек в системе тактирования (PLL, Phase Locked Loop или DLL, Delay Locked Loop), средствами поддержки интерфейса JTAG и др.

При конфигурировании FPGA функциональные блоки настраиваются на выполнение необходимых операций преобразования данных, а система межсоединений — на требуемые связи между функциональными блоками. В результате во внутренней области FPGA реализуется схема нужной конфигурации. Расположенные по краям кристалла блоки ввода/вывода обеспечивают интерфейс FPGA с внешней средой. Блоки ввода/вывода современных FPGA можно программировать на выполнение требований множества стандартов передачи данных (число таких стандартов может доходить до 20).

На рис. 1.10, б укрупненно показан состав типичного функционального блока ФБ, в который входят функциональный преобразователь ФП, реализованный в виде программируемого запоминающего устройства (LUT, Look-Up Table), триггер (регистр RG) и мультиплексоры (MUX), играющие роль средств конфигурирования ФБ.

LUT — наиболее распространенная разновидность ФП в FPGA со статической памятью конфигурации. В схемах FPGA с однократным программированием перемычек находят применение ФП в виде простых логических вентилей (SLC, Simple Logic Cell) и логических модулей на основе мультиплексоров [1].

3.2. Функциональные блоки FPGA

Табличный ФП типа LUT представляет собою запоминающее устройство, хранящее значения искомых функций, считываемые по адресу-аргументу. Запоминающее устройство с организацией 2m x n имеет m адресных входов и n выходных линий. В таком запоминающем устройстве можно хранить таблицу для считывания n функций от m переменных, поскольку каждый разряд хранимого массива данных можно рассматривать как столбец значений переключательной функции. В память можно записывать любые числа, и, следовательно, разрядные столбцы этих чисел могут воспроизводить любые функции m переменных. Время вычисления результата не зависит от воспроизводимой функции и равно времени считывания слова из памяти.

Второй тип ФБ — схема, основой которой служат программируемые мультиплексоры (фирма Actel и др.). В этих ФБ выходная величина описывается некоторой так называемой порождающей функцией, соответствующей использованию всех входов схемы как информационных. При программировании на некоторые входы задаются константы 0 и 1, разные сочетания которых порождают целый спектр возможностей воспроизведения логических функций. Подробнее о таких возможностях говорится в работах [1, 2 и др.].

Третий тип ФБ — так называемые "мелкозернистые", блоки, составленные, чаще всего, из транзисторных пар, выделяемых из цепочек транзисторов с n- и р-каналами. Из таких пар собираются традиционные для КМОП-схем логические элементы, методы синтеза которых традиционны.

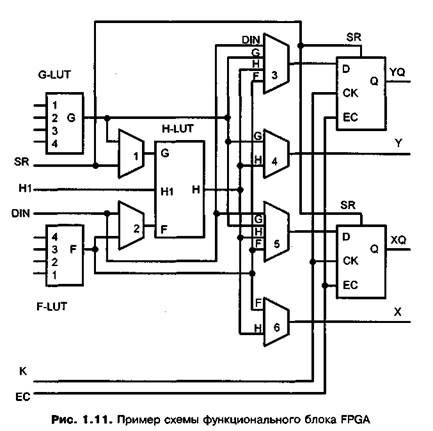

Типичную структуру ФБ FPGA с триггерной памятью конфигурации рассмотрим на примере микросхемы семейства Spartan фирмы Хilinx (рис. 1.11). Фирма Xilinx изобрела и активно разрабатывает оперативно реконфигурируемые FPGA, ее продукция занимает 30—40% мирового рынка ПЛИС. После семейства Spartan фирма выпустила семейство Spartan II, но для иллюстрации особенностей FPGA выбрано первое из этих семейств, т. к. второе по схемотехнике блоков аналогично семействам Virtex и Virtex E.

По своей структуре микросхемы Spartan продолжают линию развития классических FPGA, популярным представителем которой является семейство ХС4000 той же фирмы. В функциональных блоках этих микросхем логические преобразования выполняются тремя LUT-блоками (функциональными преобразователями ФП) G, F и Н. Преобразователи G и F — программируемые запоминающие устройства (ЗУ) с организацией 16x1, способные воспроизводить любые функции четырех переменных, значения которых могут быть переданы на выходы Y и X через мультиплексоры 4 и 6 при соответствующем их программировании (через линии верхних входов мультиплексоров).

На рисунках, как и ранее, в обозначениях мультиплексоров не отражена их программируемость, поскольку все они без исключения обладают этим свойством.

Через верхний вход мультиплексора 1 и нижний вход мультиплексора 2 функции G и F могут быть поданы на ФП-Н (ЗУ с организацией 8x1) для образования "функции от функций" с целью получения результирующей функции, зависящей от более чем четырех аргументов. К третьему входу ФП-Н подключен входной сигнал H1, так что Н =f(G, F, H1). Аргументами для ФП-Н, поступающими от мультиплексоров 1 и 2, в зависимости от их программирования может быть не только набор G, F, H1, но также наборы G, H1, DIN; SR, H1, DIN; SR, H1, F. Линии DIN и SR используются либо для передачи в триггер непосредственно входных данных и сигнала установки/сброса (Set/Reset), либо как входы ФП-Н.

Перечисленные ресурсы логической части ФБ позволяют воспроизводить:

- любую функцию с числом аргументов до 4 включительно плюс вторую такую же функцию плюс любую функцию с числом аргументов до трех;

- любую функцию 5 аргументов (одну);

- любую функцию 4 аргументов и одновременно некоторые функции 6 аргументов, некоторые функции с числом аргументов до 9.

Сигналы H1, DIN, SR, ЕС являются для ФБ входными, они подаются на его внутренние схемы через группу из четырех мультиплексоров MUX "4—1" (на рисунке не показаны), к которым подключены 4 линии внешней шины управления С1...С4. Это позволяет распределять сигналы H1, DIN, SR и ЕС по линиям С1...С4 в любом желаемом варианте.

Мультиплексоры 3...6 направляют те или иные сигналы данных управления на триггеры 1 и 2. Триггеры могут использоваться для фиксации и хранения выходных сигналов функциональных преобразователей или же работать независимо от них. Входной сигнал ФБ DIN может быть прямым входом для любого триггера. Сигнал H1 тоже можно передавать любому триггеру, но через ФП-Н, что вносит в цепь его передачи некоторую задержку.

Оба триггера имеют общие входы СК тактирования от сигнала К, разрешения тактирования ЕС и установки/сброса SR. Внутренние программируемые цепи в схеме триггера (на рис. 1.11 не показаны) позволяют индивидуально программировать полярность тактирующего сигнала СК. Сигнал ЕС синхронизирован с сигналом СК, сигнал SR асинхронный и для каждого триггера с использованием внутренних цепей триггера программируется как сигнал установки или сброса. Этот сигнал определяет состояние, в котором окажется триггер после процесса конфигурации микросхемы. Конфигурация определяет и характер воздействия на триггеры импульсов GSR (Global SR) и SR при работе схемы.

3.3. Блоки ввода/вывода FPGA

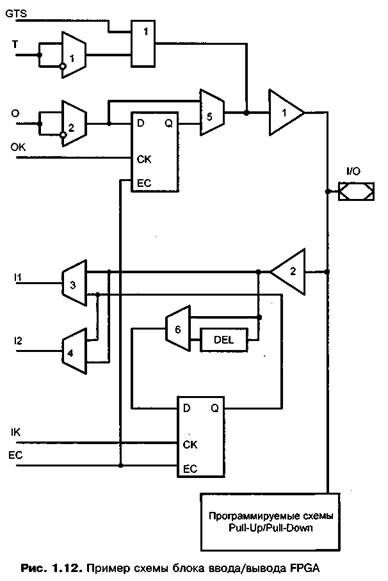

Блоки ввода/вывода, показанные на примере микросхем семейства Spartan фирмы Хilinx (рис. 1.12), обеспечивают интерфейс между выводами корпуса FPGA и ее внутренними логическими схемами. Каждому выводу корпуса придается блок ввода/вывода БВВ, который может быть конфигурирован как вход, выход или двунаправленный вывод.

Работа БВВ как выходного блока обслуживается следующими элементами: выходным буфером 1, триггером 1, мультиплексорами 1, 2, 5 и логической схемой ИЛИ. Выводимый сигнал О можно получать в прямой или инверсной форме в зависимости от программирования мультиплексора 2. Этот сигнал может передаваться на выходной буфер непосредственно или сниматься с триггера при соответствующем программировании мультиплексоpa 5. Сигналы Т и GTS (Global Tri-State), согласно логике ИЛИ, управляют переводом буфера в третье состояние, причем активный уровень сигнала Т программируется с помощью мультиплексора 1. Внутренние программируемые цепи триггера (на рисунке не показаны) позволяют изменять полярность тактирующего фронта. Сам буфер имеет программируемые крутизну фронта выходного сигнала и его уровни (КМОП/ТТЛ). Крутизна фронтов в некритичных к скорости передачи цепях снижается для уменьшения уровня помех на шинах питания и земли. Используется так называемый мягкий старт (Soft Start-Up), снижающий помехи при конфигурировании схемы и переходе ее к рабочему режиму, когда одновременно активизируются многие буферы. Первая активизация автоматически происходит с пологими фронтами перепадов напряжения. Затем вступает в силу заданный выбор той или иной крутизны фронтов в зависимости от принятой конфигурации БВВ.

Тракт ввода сигналов содержит входной буфер 2, триггер 2, программируемые мультиплексоры 3, 4, 6, элемент задержки ЭЗ и программируемые схемы задания определенных потенциалов выводу, к которому не подключен вводимый или выводимый сигнал (схемы Pull-Up/Pull-Down). Вводимый сигнал в зависимости от программирования мультиплексоров 3 и 4 или поступает непосредственно в систему коммутации FPGA по входным линиям II и 12, или же фиксируется триггером и с его выхода передается в эти линии. Триггеры могут конфигурироваться как тактируемые фронтом или как защелки (D-триггеры, управляемые уровнем). Выбор осуществляется присвоением триггеру соответствующего библиотечного символа. В цепи передачи сигнала на триггер 2 могут быть включены элементы задержки (при передаче сигнала через нижний вход мультиплексора 6). Включение задержки гарантирует необходимые временные соотношения между входными сигналами триггера D и глобальным сигналом тактирования.

Входной буфер может конфигурироваться для восприятия входных сигналов с пороговым значением ТТЛ (1,2 В) или КМОП (0,5 Ucc). Выходные уровни тоже конфигурируются, две глобальные регулировки входных порогов и выходных уровней независимы.

3.4. Системы межсоединений

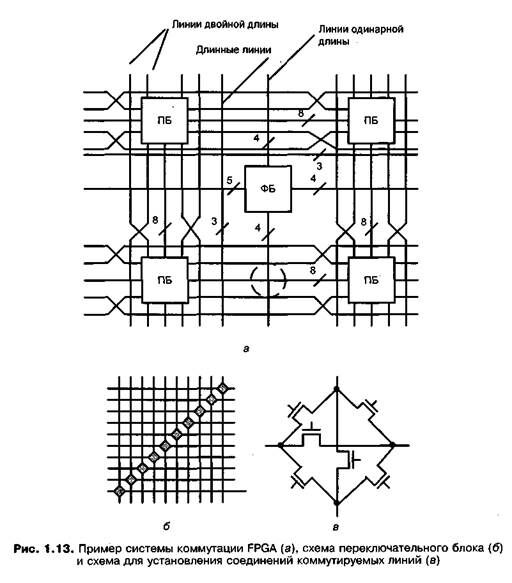

Для систем межсоединений FPGA организация непрерывных соединений затруднительна. Для них характерны сегментированные линии связей, составленные из отдельных проводящих отрезков — сегментов. Сегменты соединяются в нужную цепь с помощью программируемых ключей. Выбор длины сегментов должен учитывать, что короткие сегменты затрудняют передачу сигналов на большие расстояния (в длинных связях появится много программируемых ключей, а вместе с ними задержек сигналов и затрат площади кристалла), а длинные сегменты неудобны для коротких связей. Поэтому система межсоединений имеет, как правило, иерархический характер, и в ней сочетаются различные типы сегментов (основные связи, связи двойной длины, прямые связи для близлежащих функциональных блоков, длинные линии, пересекающие кристалл по всей его длине или ширине).

Систему межсоединений FPGA образуют сегментированные линии и переключательные блоки ПБ (PSM, Programmable Switching Matrix). Функциональные блоки имеют квадратные геометрические очертания, их выводы распределены по всем сторонам квадрата для облегчения коммутируемости. Для межсоединений функциональных блоков во внутренней области кристалла имеются три типа связей: одинарной длины, двойной длины и длинные линии. Упрощенная система коммутации FPGA показана на рис. 1.13, а на примере FPGA семейства ХС4000 фирмы Xilinx.

На пересечениях вертикальных и горизонтальных каналов расположены переключательные блоки (рис. 1.13, б). В пределах ПБ пересекаются вертикальные и горизонтальные линии связей, и в каждом пересечении имеется цепь из 6 транзисторов для установления того или иного соединения. Сигнал, поступающий в ПБ по какой-либо линии (например, горизонтальной), может быть направлен вверх, вниз или прямо в зависимости от того, какой транзистор будет открыт при конфигурировании FPGA. Возможна и одновременная передача сигнала по нескольким направлениям, если требуется его разветвление.

Линии одинарной длины осуществляют, преимущественно, межсоединения соседних или близлежащих ФБ, линии двойной длины огибают переключательные блоки, соседние по отношению к данному, и проходят к следующим, чем облегчается установление более длинных связей. По три длинных линии, пересекающих весь кристалл по длине (ширине), реализуются сверху, снизу и по обоим бокам ФБ.

Лекция "Сети Frame Relay" также может быть Вам полезна.

Выводы функциональных блоков пересекают горизонтальные и вертикальные каналы трассировки, проходящие непосредственно около них, и могут программируемыми точками связи подключаться к линиям каналов. Дальнейшее направление сигналов в нужные цепи осуществляется переключательными блоками.

Линии двойной длины сгруппированы в пары, имеется по 4 вертикальных и горизонтальных линии, обеспечивающих более быструю и эффективную передачу сигналов на средние расстояния. Длинные линии, рассчитанные на передачу сигналов на большие расстояния и при большой нагрузке, имеют в середине ключ, разделяющий линию на две части ((рис. 1.13, в).

Кроме системы коммутации для функциональных блоков FPGA (в частности, семейство Spartan) может иметь дополнительные трассировочные ресурсы, расположенные в виде кольца вне пределов матрицы ФБ. Эти ресурсы позволяют изменять назначение вводов/выводов микросхемы и облегчают, тем самым, модификацию проекта, реализованного на FPGA, без влияния на разводку печатных плат, на которых монтируются микросхемы.

В число FPGA по принятой классификации попадают микросхемы с числом эквивалентных вентилей около 200 – 85000, системными частотами приблизительно 50 – 80 МГц, числом пользовательских выводов 100 – 300. Лидером в производстве однократно программируемых FPGA считают фирму Actel, a в производстве FPGA с триггерной памятью конфигурации — фирму Xilinx.

Дополнительная литература к лекции

- Угрюмов Е.П. Цифровая схемотехника. – СПб.: БХВ-Петербург, 2000. – 528 с.

- Шалыто А.А. Методы аппаратной и программной реализации алгоритмов. – СПб.: Наука, 2000. – 780 с.