Прямой доступ к памяти

Прямой доступ к памяти.

При работе в режиме прямого доступа к памяти (ПДП) контроллер ПДП выполняет следующие функции:

• принимает запрос на ПДП от внешнего устройства;

• формирует запрос микропроцессору на захват шин системной магистрали;

• принимает сигнал, подтверждающий вход микропроцессора в состояние захвата (перехода в z-состояние, при котором процессор отключается от системной магистрали);

• формирует сигнал, сообщающий внешнему устройству о начале выполнения циклов ПДП;

• выдает на шину адреса системной магистрали адрес ячейки ОП, предназначенной для обмена;

• вырабатывает сигналы, обеспечивающие управление обменом данными;

Рекомендуемые материалы

• по окончании ПДП либо организует повторение цикла ПДП, либо

прекращает режим ПДП, снимая запросы на него.

Циклы ПДП выполняются с последовательно расположенными ячейками памяти, поэтому контроллер ПДП имеет счетчик числа переданных байтов.

Рекомендуем посмотреть лекцию "14. Требования к оформлению реквизитов".

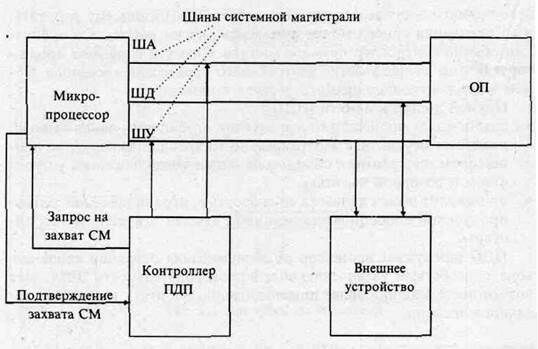

На рис. 6.4 приведена схема взаимодействия устройств микропроцессорной системы в режиме ПДП.

Рис. 6.4. Взаимодействие устройств в режиме ПДП

Контроллер ПДП может работать в двух основных режимах: в режиме программирования и в режиме выполнения циклов ПДП.

В режиме программирования микропроцессор работает с КПДП, как с внешним устройством. После загрузки в КПДП управляющих слов контроллер переходит в пассивное состояние. В этом состоянии КПДП будет находиться до тех пор, пока не поступит запрос на ПДП от ВУ или от микропроцессора. Обнаружив запрос на ПДП, контроллер выставляет микропроцессору запрос на захват системной магистрали и ожидает от него подтверждения захвата (т.е. отключения МП от СМ, перехода его выходов в состояние высокого сопротивления, г-состояния). При получении сигнала подтверждения захвата, контроллер начинает выполнять циклы ПДП.

Системная магистраль (СМ) в режиме прямого доступа к памяти используется мультиплексно КПДП и микропроцессором, причем основное управление системной магистралью выполняет КПДП, а МП получает к ней доступ на очень короткие промежутки времени для обмена информацией с основной памятью.