Операционный_синтез_цифровых_устройств (775248), страница 4

Текст из файла (страница 4)

На рис. 4 изображена принципиальная схема ОЗУ, построенная из четырех ИС К155РУ2:

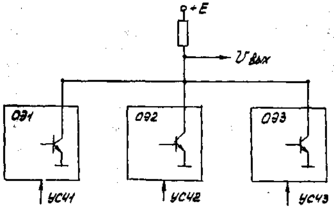

Рис. 3. Операционные элементы с открытым коллектором

Рис. 4. Схема ОЗУ на К155РУ2

ОЗУ[0:63]{1:4} = ОЗУ[0:15]{1:4} . ОЗУ[16:31]{1:4} . ОЗУ[32:47]{1:4} . ОЗУ[48:63]{1:4}

У всех интегральных схем ОЗУ входные информационные шины, выходные информационные шины и шины младших разрядов кода адреса являются общими. Старшие разряды кода адреса используются для селекции выбранной ИС либо по записи, либо по считыванию, для чего применяются дополнительные логические схемы (дешифратор и 8 схем И).

Недостатком схем с открытым коллектором является их относительно низкое быстродействие, что обусловливается большой постоянной времени заряда паразитной емкости линии связи через резистор общей нагрузки.

Более совершенной является схема с тремя состояниями выхода, в которой при отсутствии сигнала считывания выход операционного элемента полностью отключается от магистрали (общей шины).

В операционных элементах с тремя состояниями выхода, построенных по ТТЛ логике, специальный сигнал управления закрывает как верхний, так и нижний транзистор выходного каскада, переводя элемент в состояние высокого выходного сопротивления. В этом состоянии операционный элемент не оказывает никакого воздействия на выходную шину, позволяя тем самым использовать ее другому элементу.

Термин "три состояния выхода" подчеркивает активный характер формирования логической переменной как по нулю, так и по единице, когда в режиме передачи открыт либо верхний, либо нижний транзистор выходного каскада элемента. Упрощенная принципиальная схема ТТЛ элемента с тремя состояниями выхода изображена на рис. 5. По сравнению с обычным элементом в него введена дополнительная связь между одним из входов и базой верхнего транзистора выходного каскада. Теперь этот вход рассматривается как управляющий, низкий уровень управляющего сигнала переводит логический элемент в третье состояние (состояние отключения от общего выходного провода).Нетрудно видеть, что управляющий сигнал высокого уровня эквивалентен сигналу считывания операционного элемента, работающего на общую шину.

Рис. 5. ТТЛ элементы с тремя состояниями выхода

Идея третьего состояния выхода нашла свое воплощение в построении операционных элементов микропроцессорных вычислителей. Для упрощения связи этих элементов с общей шиной входную и выходную шину элемента соединяют внутри корпуса микросхемы, разделяя режим записи и считывания значением сигнала, управляющего третьим состоянием. Двунаправленность движения информации между элементами, объединенными магистральной связью, указывают при помощи двух стрелок на шине связи элемента с общей шиной.

2.4. ЗАДАЧИ

Применение методов структурного синтеза для построения операционной части операционных устройств проиллюстрируем на примерах решения двух задач, одна из которых приводит к комбинационной реализации устройства, а другая - к регистровой.

2.4.1. Задача 1

Спроектировать устройство, преобразующее восьмиразрядный двоичный код числа А{1:8} в выходной код В{1:К} следующим образом:

если А{1:2}= 00, то В{1:К}= А{1:8} + 8

если А{1:2}= 01, то В{1:К}= А{1:8} + 16

если А{1:2}= 10, то В{1:К}= А{1:8} + 32

если А{1:2}= 11, то В{1:К}= А{1:8} + 64

здесь 8, 16, 32 и 64 - десятичные эквиваленты двоичных кодов, которые прибавляются к исходному коду А.

Прежде всего определим разрядность выходного кода. Заметим, что разрядность кода наибольшей константы равна 7 (64=26), что меньше разрядности кода А. Поэтому разрядность суммы, определяемая как разрядность наибольшего слагаемого плюс единица, будет равна 9. Итак, имеем К=9.

Будем решать задачу комбинационными средствами, тогда микропрограмма выродится в описание комбинационного оператора

ОПЕРАТОР СУММА (В, А, 8, 16, 32, 64)

ПЕРЕМЕННЫЕ

ВНЕШНИЕ: А{1:8}, В{1:9}

ВНУТРЕННИЕ:

Описание внутренних переменных зависит от способа решения поставленной задачи. В простейшем случае выходной код может формироваться как результат мультиплексирования кодов суммы, полученных на одном из четырех комбинационных сумматоров. Поэтому внутренние переменные могут быть описаны следующим образом:

ВНУТРЕННИЕ: СМ1{1:9}, СМ2{1:9}, СМ3{1:9}, СМ4{1:9}, МS{1:9}

Описание оператора включает в себя ряд комбинационных преобразований:

СМ{1:9} = 0.А{1:8} + 8

СМ2{1:9} = 0.А{1:8}+ 16

СМЗ{1:9} = 0.А{1:8}+ 32

СМ4{1:9} = 0.А{1:8}+ 64

P1 = А{1:2} ∞ 00

Р2 = А{1:2} ∞ 01

Р3 = А{1:2} ∞ 10

Р4 = А{1:2} ∞ 11

MS {1:9}= P1 & CM{1:9}v P2 & CM2{1:9}

РЗ & СМ{1:9} v Р4 & СМ4{1:9}

В{1:9} = МS{1:9}

При описании оператора мы приняли, что мультиплексирование осуществляется под воздействием четырех коммутирующих сигналов P1-P4, формируемых четырьмя логическими схемами. Имена этих схем, совпадающих с именами коммутирующих сигналов, должны быть внесены в описание внутренних переменных:

ВНУТРЕННИЕ: P1, Р2, РЗ, Р4

Для построения структурной схемы устройства необходимо иметь те операционные элементы, которые описаны как ВНУТРЕННИЕ. Это четыре девятиразрядных комбинационных сумматора, четыре схемы формирования признаков и один мультиплексор, переключающий четыре девятипроводные шины. Можно воспользоваться и стандартным мультиплексором, переключаемым кодом. Тогда вместо сигналов признаков на него необходимо будет подать переключающий код А 1:2 . Такой мультиплексор описывается предложением:

MS{1:9}= MS (СМ [1:4] {1:9}. A{1:2})

Описание оператора позволяет нам установить характер связей между операционными элементами. Нетрудно видеть, что связь между входной шиной и сумматорами будет разветвляющейся для всех разряда в. а для первых двух разрядов входной шины добавляется еще и связь с управляющим входом мультиплексора.

Знак тождества в выражении B{1:9} = MS{1:9} указывает, что выходная шина мультиплексора используется как выходная шина всего устройства. Структурная схема устройства приведена на рис. 6, а.

Рис. 6. Структурная схема устройства суммирования: а - до упрощения; б - минимизированная

Перейдем к упрощению устройства. Для этого воспользуемся известными законами эквивалентного преобразования предложений операционного описания.

Подставим описание сумматора в описание мультиплексора:

MS{1:9}= P1 & (0.А{1:8} + 8) v P2 & (0.А{1:8} + 16) v P3 & (0.А{1:8} +

+ 32) v P4 & (0.A{1:8} + 64)

Применением распределительного закона раскроем скобки:

МS{1:9} = P1 & 0.A{1:8} v P2 & 0.A{1:8} v P3 & 0.A{1:8} v P4 0.A{1:8} +

+ (P1 & 8 v P2 & 16 v P3 & 32 v P4 & 64)

Вынесем за скобки 0.А{1:8}:

MS{1:9}= (P1 v P2 v P3 v P4) & 0.A{1:8}+ (P1 & 8 v P2 & 16 v P3 & 32 v P4 & 64)

Поскольку признаки составляют полную группу событий, их дизъюнкция тождественно равна единице, поэтому

МS{1:9}= 0.А{1:8} + (P1 & 8 v P2 & 16 v P3 & 32 v P4 & 64)

Полученное выражение показывает, что синтезируемое нами устройство может быть построено на одном сумматоре и мультиплексоре констант:

MS{1:9}= P1 & 8 v P2 & 16 v P3 & 32 v P4 & 64

СМ{1:9}= 0.А{1.8}+ МS{1:9}

В{1:9} = СМ{1:9}

Дальнейшее упрощение связано с поразрядным преобразованием предложения описания мультиплексора.

Представим десятичные коды в виде их двоичных эквивалентов

MS{1:9}= P1 & 000001000 v P2 & 000010000 v P3 & 000100000 v P4 & 001000000

Выполним операцию конъюнкции над признаками и константами:

MS{1:9}= 00000.Р1.000 v 0000.Р2.0000 v 000.РЗ.00000 v 00.Р4.00000

Каждый из разрядов MS{1:9} формируется как дизъюнкция cooтветствующих разрядов всех четырех кодов:

МS{1:9}= 00.P4.P3.P2.P1.000

Из выражения видно, что мультиплексор может быть заменен схемами формирования признаков P1, Р2, Р3 и Р4, выходные сигналы которых образуют изменяемый по признакам "код константы":

P1 = ┐А1 & ┐А2

Р2 = ┐A1 & A2

Р3 = А1 & ┐A2

Р4 = А1 & A2

СМ{1:9} = 0.А{1:8} + 00.P4.P3.P2.P1.000

Окончательное упрощение связано с уменьшением разрядности комбинационного сумматора путем посегментного преобразования его операционного описания.

Разобьем кода слагаемых сумматора на два сегмента. Результаты сложения внутри сегментов могут быть объединены в сумму, если при формировании старшего сегмента учтен перенос из сегмента младших разрядов. Выражение

СМ{1:К}= А{1:К}+ В{1:К}

эквивалентно выражению

CM{1:K} = (А{1:L} + B{1:L} + П{L}).(A{L+1:К} + В{L+1:К}),

где П{L} - перенос из L + 1 разряда.

Если одно из слагаемых внутри сегмента младших разрядов равно нулю, то перенос Р заведомо пропадает:

СМ{1:К}= (А{1:L} + В{1:L}).(А{L+1:К}+0)

или

СМ{1:К}= (А{1:L} + В{1:L}).A{L+1:К}

Воспользовавшись полученным соотношением, преобразуем описание комбинационного сумматора к виду

СМ{1:9}= {0.А{1:5} + 00.Р4.Р3.Р2.Р1).А{6:8}

Поскольку старший разряд слагаемых равен нулю, старший разряд суммы может формироваться по значению переноса из предыдущего разряда (СМ {1} = П{1} = П1). Тогда

СМ {1:9}= П1.(А{1:5} + 0.P4.P3.P2.P1).A{6:8}

Откуда видно, что разрядность сумматора может быть уменьшена на 4 бита. В конечном итоге описание оператора синтезируемого устройства принимает вид

ОПЕРАТОР СУММА (В, А, 8, 16, 32, 64)

ПЕРЕМЕННЫЕ

ВНЕШНИЕ: А{1:8}, В{1:9}

ВНУТРЕННИЕ: Р1, Р2, РЗ, Р4, СМ{1:5}

P1 = ┐А1 & ┐А2

Р2 = ┐А1 & A2

РЗ = А1 & ┐A2

Р4 = А1 & A2

СМ{1:5} = А{1:5}+ 0.P4.P3.P2.P1

В{1:9} = П1.СМ{1:5}.А{6:8}

Структурная схема минимального эквивалентного устройства изображена на рис. 6,6. Если считать, что сложность мультиплексора сравнима со сложностью комбинационного сумматора, то объем устройства в результате его минимизации сократился почти в 9(!) раз.

2.4.2. Задача 2

Спроектировать устройство, определяющее максимальный размер группы из рядом стоящих единиц кода А{1:64}.

Проектируемое операционное устройство может быть построено в принципе и как комбинационное, и как регистровое. Однако нетрудно показать, что комбинационная реализация приводит не только к чрезмерным аппаратурным затратам, но и требует больших усилий на проектирование. Действительно, согласно правилам комбинационного синтеза, достаточно построить таблицу истинности на 64 переменные, заполнить наборами переменных все ее 264 строк и для каждого набора определить искомый выходной код. Далее нужно произвести минимизацию системы семи логических функций 64 переменных. Такая процедура, естественно, практически не реализуема.

Будем строить проектируемое устройство как регистровое, в котором выходной код формируется в процессе побитовой обработки кода А{1:64}.

Можно предложить следующий алгоритм формирования выходного кода:

-

Конечное число рядом стоящих единиц принимается за ноль.

-

Слева направо в коде А подсчитывается число рядом стоящих единиц и формируется текущее число рядом стоящих единиц.

-

Если текущее число больше конечного, оно становится конечным числом рядом стоящих единиц.

-

Если просмотрены не все разряды кода А, повторяется пункт 2; в противном случае процедура заканчивается.

Предложенный алгоритм может быть трансформирован в алгоритм функционирования операционного устройства, если его шаги будут выражены в терминах работы операционных элементов.

Примем, что входной код А{1:64} записывается в сдвигающий регистр РЕГА{1:64}, который обеспечивает просмотр всех разрядов кода А, начиная с первого А{1}. Это организуется засылкой в разряд РЕГА{1} значений разрядов РЕГА{2}, РЕГА{3} и т.д. путем сдвига кода регистра на один разряд влево. Будем подсчитывать число рядом стоящих единиц в счетчике единиц СЧ{1:7}, а число циклов работы устройства - в счетчике циклов СЧЦ{1:7}. Для формирования выходного кода воспользуемся статическим регистром РЕГ{1:7}, куда будем переписывать код числа единиц в группе единиц из счетчика единиц. Работу устройства организуем следующим образом. Обнулим содержимое счетчиков и выходного регистра и запишем входной код в регистр А. Проанализируем значение первого разряда регистра А. Если он равен единице, то произведем счет единиц в группе и подготовим устройство к работе в следующем цикле - сдвинем содержимое регистра А влево на один разряд и прибавим в счетчик циклов единицу. Проверим, не является ли цикл последним. Если цикл последний, то закончим процесс, если нет - продолжим его для следующего разряда входного кода.

Если при анализе первого разряда регистра А было установлено, что он равен нулю, то это означает, что группа единиц закончилась и возникла необходимость (если это нужно) перезаписи содержимого счетчика единиц в регистр выходного кода. Условимся, что эта перезапись осуществляется при равенстве единицы признака P1, формируемого схемой сравнения "не больше" кодов счетчика единиц и регистра выходного кода.

Завершение работы устройства связано с просмотром всех разрядов входного кода, что определяется появлением в счетчике циклов кода конечного цикла и формированием признака окончания процесса Р2.

Теперь алгоритм работы операционного устройства принимает вид, изображенный на рис. 7.