Преимущества регистр-регистровой архитектуры

Лекция 10.

Преимущества регистр-регистровой архитектуры

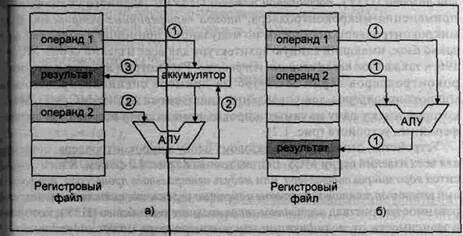

При построении большинства микропроцессоров и микроконтроллеров (например, серии 8-разрядных микроконтроллеров MCS-51) используется традиционная, так называемая аккумуляторная архитектура, когда один из регистров специального назначения аккумулятор по умолчанию является источником одного из двух операндов и одновременно приемником результата операции, выполняемой в арифметико-логическом устройстве (АЛУ). Такой подход позволяет существенно уменьшить формат команды за счет адресации в поле операндов только одного из операндов.

Для выполнения какого-либо действия в процессорах «классической» аккумуляторной архитектуры в общем случае кроме собственно команды, пример, сложения, требуются по крайней мере еще две операции пересылки данных: загрузка первого операнда в аккумулятор и через него в один из портов арифметико-логического устройства (АЛУ), а также пересылка результата операции из аккумулятора по месту назначения уже после завершения операции (рис.17) при этом второй операнд извлекается из оперативной памяти непосредственно в процессе выполнения операции. Также в процессе выполнения операции результат помещается в аккумулятор.

По мере развития микропроцессорной техники аккумуляторная архитектура стала тормозом в пoвышении производительности центрального процессора и уступила место так называемой регистр-регистровой архитектуре. Основным отличием регистр-регистровой архитектуры от аккумуляторной является то, что любые ячейки интегрированной на кристалл микроконтроллера сверхбыстродействующей оперативной памяти, регистрового ОЗУ, могут рассматриваться либо как операнды-источники, либо как аккумулятор для приема результата операции. При таком подходе любая из команд процессора может быть трехоперандной и необходимость в дополнительных операциях пересылки данных из аккумулятора и обратно отпадает. Естественно, что регистр-регистровая архитектура требует более сложного формата команды. Наряду с полем кода операции в формате команды будут присутствовать поля адресов операндов-источников и операнда-приемника.

Рис. 17. Сравнение аккумуляторной (а) и регистр-регистровой архитектуры (б)

Таким образом, любая ячейка регистрового файла, внутренней сверхоперативной памяти, может выполнять функцию как источника данных, так и приемника данных.

Главные преимущества регистр-регистровой архитектуры:

• Отсутствует необходимость в предварительной загрузке одного из, операндов в аккумулятор перед выполнением операции.

• Содержимое источников данных в результате выполнения операции может оставаться неизменным, либо модернизироваться по желанию программиста. В последнем случае источник данных одновременно будет и приемником результата операции.

Рекомендуемые материалы

• Резко уменьшается число операций по пересылке данных и возрастает скорость вычислений.

• Появляется возможность расширения системы команд трехоперандными высокопроизводительными командами.

Совокупность перечисленных выше факторов вместе с главным преимуществом - возможностью выполнения операций непосредственно над 16-разрядными операндами, приводит к повышению производительности 16-разрядных микроконтроллеров в несколько раз по сравнению с 8-разрядными контроллерами, работающими на тех же тактовых частотах.

Блок-схема микроконтроллера MCS-196.

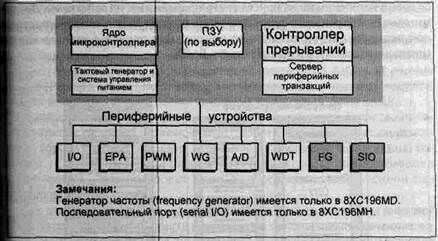

Микроконтроллеры семейства MCS-196 являются однокристальными микроЭВМ с интеграцией на кристалл центрального процессора, оперативной памяти (ОЗУ), постоянной памяти (ПЗУ) и заданного спецификой применения микроконтроллера, набора периферийных устройств. Все микроконтроллеры построены по модульному принципу и содержат базовый блок, имеющий единую архитектуру для всех изделий серии MCS-196, а также блок периферийных устройств. Рассмотрим архитектуру микроконтроллеров серии MCS-196 на примере специализированных микроконтроллеров для управления двигателями 8xC196MC/MD/MH. которые имеют одну из самых широких номенклатур встроенных периферийных устройств (рис. 18).

Устройства, относящиеся к базовому блоку микроконтроллера, общему для всех изделий серии MCS-196, выделены на рис. 18 фоном. К ним относится ядро микроконтроллера или модуль центрального процессора, встроенный генератор тактовой частоты и система управления питанием, интегрированное на кристалл постоянное запоминающее устройство (ПЗУ), которое в зависимости от модификации микроконтроллера может отсутствовать. контроллер прерываний (Interrupt Controller), а также сервер периферийных транзакций (PTS) — специализированный контроллер прерываний, обеспечивающий быстрый обмен данными между периферийными устройствами и памятью практически без участия центрального процессора.

Рис. 18. Типовая архитектура микроконтроллеров семейства MCS-196 на примере микроконтроллеров для управления двигателями 8xC196MC/MD/MH.

В набор интегрированных на кристалл периферийных устройств для микроконтроллеров 8xC196MC/MD/MH входят:

порты ввода/вывода (I/О);

процессор событий (EРA);

генератор широтно-импульсных сигналов (PWM);

многоканальный генератор периодических сигналов (WG);

аналого-цифровой преобразователь (A/D);

сторожевой таймер (WDT);

генератор частоты (FG1;

последовательные порты ввода/вывода данных (SIO).

Набор встроенных периферийных устройств меняется в зависимости от типа микроконтроллера и определяет область его преимущественного применения.

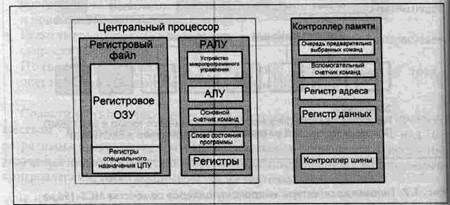

Модуль центрального процессора. Модуль центрального процессора обеспечивает выполнение программы пользователя и состоит из центрального процессора (ЦПУ) Central Processing Unit (CPU) и контроллера памяти Memory Controller (рис. 19). В состав центрального процессора входят регистровый файл Register File и регистровое арифметико-логическое устройство (Register Arithmetic-Logic Unit) или сокращенно РАЛУ (RALU).

Внутренняя 16-разрядн4я шина связывает центральный процессор с контроллером памяти и контроллером прерываний (interrupt controller), а также со всеми встроенными на кристалл периферийными устройствами. Дополнительная внутренняя 8-разрядная шина используется для непосредственной передачи байтов команды из контроллера памяти в регистр команд (instruction register), расположенный в РАЛУ.

Рис. 19. Структура модуля центрального процессора

В состав центрального процессора входит устройство микропрограммного управления (microcode engine), предназначенное для приема от контроллера памяти кода очередной команды, дешифрации кода и генерации последовательности управляющих команд, подаваемых на регистровое арифметико-логическое устройство, и необходимых для выполнения операций над байтами, словами и длинными словами, расположенными в 256-байтовом нижнем регистровом файле. Использование механизма адресации операндов через вертикальное окно в нижнем регистровом файле, позволяет выполнять в РАЛУ также и операции с данными, расположенными в верхнем регистровом файле, а в новейшей серии микроконтроллеров MCS-296 — даже во внешней памяти.

Центральный процессор связывается с внутренней кодовой и внешней памятью (программ и данных) через контроллер памяти. Исключение составляет регистровый файл, доступ к которому обеспечивается непосредственно. В состав контроллера памяти входят несколько устройств: вспомогательный счетчик команд (Slave PC), 4-байтовая очередь из предварительно выбранных из памяти и готовых для выполнения кодов команд (Queue), контроллер шины (Bus Controller), регистры адреса (Adress Register) и данных (Data Register).

Запрос на доступ к памяти может поступить как от центрального процессора при выполнении текущей команды, например, для получения операнда из внешней памяти по косвенному адресу, расположенному в одном из регистров-слов внутреннего ОЗУ, так и от диспетчера очереди предварительно выбранных кодов команд. Механизм предварительной выборки команд существенно повышает производительность центрального процессора так как к моменту завершения выполнения текущей команды следующая команда уже считана из памяти и готова для немедленного выполнения. Центральный процессор получает коды команд из 4-байтовой очереди команд (Prefetch Queue по специальной 8-разрядной шине. Код текущей исполняемой инструкции всегда находится в регистре команд РАЛУ. За выполнение пpoграммы пользователя в правильной последовательности отвечает основной счетчик команд (Master Program Counter), содержимое которого указывает на адрес очередной, подлежащей выполнению команды. Содержимое основного счетчика команд автоматически увеличивается в зависимости от длины текущей команды встроенной схемы инкрементирования.

Как отмечено выше для ускорения выборки кодов команд из внешней или внутренней кодовой памяти используется вспомогательный счетчик команд (Slave PC), содержимое которого задает адрес команды, подлежащей выборке из памяти. Выбранная команда поступает в очередь на выполнение. Как только очередная команда считывается из очереди и передается на дешифрирование в устройство микропрограммного управления центрального процессора, диспетчер очереди формирует запрос в контроллер шины Bus Controller) на считывание очередной команды. Контроллер шины входит в состав контроллера памяти и обеспечивает формирование необходимых управляющих сигналов как для считывания данных из внешней, внутренней памяти или внешнего периферийного устройства, так и для записи данных во внешнее ОЗУ или в периферийное устройство. Таким образом, контроллер шины обеспечивает считывание кодов машинных команд и запись/считывание данных. Запрoc на считывание очередной инструкции поступает от диспетчера очереди, а запрос на запись/считывание данных (операндов) - от центрального процессора. Запpoc от диспетчера очереди имеет более высокий приоритет.

Если линейная последовательность выполнения команд программы нарушается, например, вследствие выполнения команды условного или безусловного перехода или вызова подпрограммы, значение вспомогательного счетчика команд перезагружается текущим значением основного счетчика команд и очередь ранее выбранных команд аннулируется (очищается). Перезагрузка вспомогательного счетчика команд и извлечение первого байта кода инструкции из памяти занимает 4 машинных такта.

Замечание. Если при отладке микропроцессорной системы Вы пользуетесь логическим анализатором, то имейте в виду, что команды из памяти выбираются с опережением. В данный момент выполняется команда, которая уже была считана ранее

Регистровое АЛУ имеет достаточно сложную внутреннюю структуру. В его состав помимо собственно 16-разрядного арифметико-логического устройства, регистра команд и устройства микропрограммного управления входят несколько вспомогательных регистров:

• Регистры старшего и младшего слова, предназначенные для использования в командах с 32-разрядными операндами в качестве регистров временного хранения данных. Они имеют собственные устройства сдвига, что ускоряет выполнение команд сдвига, нормализации, умножения и деления.

• Регистр второго операнда АЛУ, используемый в двухоперандных командах. в частности, для хранения множителя или делителя в операциях умножения, деления, соответственно.

• 6-разрядный счетчик числа циклов для организации сдвига операнда на заданное число разрядов со схемой автоматического декрементирования.

• Регистр селектирования заданного бита, который позволяет автоматически генерировать необходимую маску при выполнении команд тестирования бита по номеру бита, указанному в команде.

• Регистры констант (0, 1, 2), необходимых для ускорения типовых операций в АЛУ.

После завершения любой операции в АЛУ результат анализируется и соответствующие признаки результата (нуля, переноса, переполнения и т.д.) выставляются в слове состояния программы Program Status Ward (PSW). Признаки результата операции используются в командах условной передачи управления для организации ветвлений в программе.

Регистровый файл

Различные типы микроконтроллеров отличаются количеством ячеек памяти в регистровом файле, так называемом регистровом ОЗУ (РОЗУ). Естественно, что чем больше объем сверхоперативной регистровой памяти, тем более сложные вычисления и с большим быстродействием могут быть организованы в микропроцессорной системе на базе данного микроконтроллера.

Первые 256 ячеек регистрового файла имеют короткие байтовые адреса и относятся к нижнему регистровому файлу, а все остальные — 16-разрядные адреса и относятся к верхнему регистровому файлу. Наибольшим быстродействием обладают команды с прямой регистровой адресацией операндов в нижнем регистровом файле. При этом используются байтовые адресные поля и команды имеют предельно короткий формат и наименьшее время выполнения. Для доступа к операндам за пределами нижнего регистрового файла (в том числе и к внешней памяти) используются специальные способы адресации, в частности косвенная, базово-индексная, а также адресация через специальные вертикальные окна.

Младшие 24 байта нижнего регистрового файла относятся к регистрам специального назначения центрального процессора (CPU special-function registers - SFRs). Здесь расположен также указатель стека (Stack Pointer SP). Вся остальная область регистрового ОЗУ, в том числе область верхнего регистрового файла, является оперативной памятью общего назначения и может использоваться программистом по своему усмотрению. Доступ производится к байтам, словам или двойным словам. Набор регистров специального назначения отличается в микроконтроллерах разных типов. Эти регистры позволяют управлять системой прерываний, селектировать вертикальные окна и выполнять целый ряд дополнительных функций.

Особенность организация памяти микроконтроллеров MCS-196

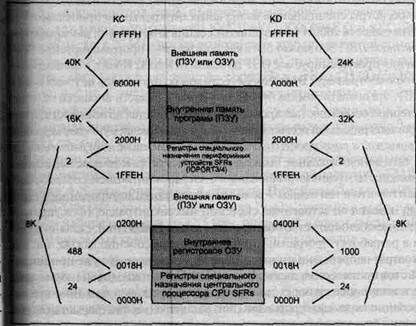

Типичная схема организации памяти 16-разрядных микроконтроллеров Intel на примере 8ХС196КС и 8XC196KD приведена на рис. 20.

Нижняя область встроенного регистрового ОЗУ (ООООН-0017Н) жестко закреплена за регистрами специального назначения центрального процессора (CPU SFRs), через которые осуществляется управление системой прерываний, механизмом селектирования горизонтальных и вертикальных окон, а также встроенными периферийными устройствами (для некоторых типов микроконтроллеров).

Начиная с адреса 0018Н располагается область регистрового 03У (Register RAM), объем которой различен для разных контроллеров и варьируется как правило, в диапазоне от 232 байт до 1 Кбайта.

Следующий сектор памяти объемом несколько меньше 8 Кбайт используется для адресации внешней памяти и/или внешних периферийных устройств В конце этой области памяти располагается еще одна область регистров специального назначения - регистров специального назначения периферийных устройств SFR (в данном случае регистров портов ввода/вывод 10PORT3 и 10PORT4). Размер этой области определяется объемом интегрированной на кристалл периферии и, например, у контроллеров 8XC196MC/MD/MH достигает 256 байт (1FEOH-1FFFH).

Рис 20. Карта распределения памяти для микроконтроллеров 8xC196KC/KD

Дело в том, что в микроконтроллерах с большим количеством интегрированных на кристалл периферийных устройств начальной области памяти 24 байта оказывается недостаточно для размещения всех регистров специального назначения периферийных устройства для их размещения отведена специальная область памяти. При этом в начальной области памяти остаются только регистры специального назначения центрального процессора.

Начиная с адреса 2000Н располагается секция внутреннего, интегрированного на кристалл ПЗУ. Это может быть как однократно-программируемое ПЗУ так и масочно-программируемое ПЗУ объемом от 8 до 32 Кбайт, в зависимости от типа микроконтроллера. В том случае, если микроконтроллер не имеет встроенного ПЗУ, эта область памяти будет относиться к области внешней памяти.

Характерной особенностью процессоров Intel является возможность задать в начале рассматриваемой области памяти не только желаемую конфигурацию микроконтроллера и микропроцессорной системы, в том числе цикл работы внешней шины, но и дополнительные коды секретности, которые полностью исключают возможность несанкционированного чтения или записи содержимого внутренней памяти и тем самым — возможность несанкционированного тиражирования изделия со встроенной системой микроконтроллерного управления. Последнее обстоятельство обеспечивает защиту вложений, сделанных заказчиком в разработку программного продукта, что особенно важно, так как доля этих затрат непрерывно растает и по некоторым оценкам уже приближается к 80% стоимости всего проекта. В начальной области кодовой памяти располагаются также вектора переходов на подпрограммы обслуживания прерываний.

Первым адресом, по которому процессор обращается для выполнения программы пользователя, является адрес 2080Н. Сюда передается управления и после сброса системы по сигналу RESET. Расположенная вслед за внутренним ПЗУ память, вплоть до адреса FFFFH может рассматриваться как внешняя память программ и/или данных и/или область aдресации внешних устройств ввода/вывода пользователя. Некоторые самые современные микроконтроллеры, например, 8XC196NP, 8XC196NU, 80C296SA, предназначенные для высокопроизводительной обработки больших массивов информации в реальном времени имеют 'возможности расширенной адресации памяти. В этом случае объем прямоадресуемой памяти возрастает до 1 Мбайта, 6 Мбайт и даже до 16 Мбайт. При этом внутренняя шина адреса микроконтроллера вместо 16-разрядной становится 24-разрядной, а во вне выводятся дополнительно 4 или 8 старших разрядов адресной шины.

Возможности подключения внешней памяти и внешних устройств ввода/вывода

На стадии разработки и отладки микропроцессорной системы приходится использовать внешнюю память программ и только затем, когда алгоритмы и программное обеспечение полностью оттестированы и начинается серийный выпуск изделия , программное обеспечение «прошивается» в внутреннюю память микроконтроллера. Кроме того, в ряде применений требуется внешняя память данных, часто энергонезависимая, для хранения промежуточных массивов информации, результатов тестирования работоспособности оборудования, текущих настроек системы управления, циклограмм управления оборудованием в функции времени и т.д.

Обратите внимание на лекцию "Таблицы".

В системах встроенного управления, где часто приходится изменять алгоритмы управления и программное обеспечение, единственной альтернативой оказывается применение в качестве внешней памяти программ так называемой флэш-памяти. Эта память, впервые анонсированная фирмой Intel в 1988 г., бурно развивается и на сегодняшний день сочетает в себе достоинства ОЗУ и ПЗУ, являясь энергонезависимой памятью с высокой плотностью хранения информации, высоким быстродействием, малым потреблением энергии, исключительной надежностью и помехоустойчивостью. Она допускает более 100 тысяч циклов перезаписи.

Вместе с тем, несмотря нa большое количество интегрированных на кристалл периферийных устройств, их часто оказывается недостаточно для решения конкретной задачи. В этом случае приходится дополнительно использовать внешние периферийные устройства: программируемые порты ввода/вывода данных, контроллеры прерываний, контроллеры последовательного ввода/вывода данных и т.д.

Встроенный контроллер внешней шины обеспечивает корректное подключение к микроконтроллеру внешней памяти и внешних периферийных устройств, а также формирование необходимых сигналов управления ими. Большинство микроконтроллеров MCS-196 имеют мультиплицированную шину адреса/данных, а самые совершенные из них могут работать и с мультиплицированной шиной адреса/данных, что повышает производительность системы и упрощает интерфейс с внешней памятью и периферией.

В зависимости от разрядности используемой внешней памяти и периферии шина может работать в нескольких режимах:

Стандартном — как 16-разрядная мультиплицированная шина (вся внешняя память и периферия 16-разрядные). 8-разрядном — когда вся внешняя память и периферия 8-разрядные. Динамически переключаемом между 8- и 16-разрядным режимами в зависимости от типа внешнего устройства, к которому в данный момент происходит обращение.

Кроме того, наличие специального входа готовности Ready допускает расширение сигналов чтения RD# и записи WR# для подключения медленно-действующей памяти и устройств ввода/вывода (например, жидкокристаллического дисплея). Более того, изменяя программно байты конфигурации микроконтроллера, можно задать требуемое число тактов ожидания для оптимального сопряжения микроконтроллера с внешними устройствами.