Лекция 3. Классификация ПЛИС

Лекция 3. Классификация ПЛИС

Рынок ПЛИС. ПЛИС становятся в последнее время всё более распространённой и привычной элементной базой для разработчиков цифровых управляющих устройств. Они характеризуются ростом плотности упаковки элементов на кристалле [1]. Многие ведущие производители либо начали серийное производство, либо анонсировали ПЛИС с эквивалентной ёмкостью более 1 миллиона логических вентилей. Цены на ПЛИС неуклонно падают. В 1995 году ПЛИС ёмкостью 100 000 вентилей стоила в Москве, в зависимости от производителя, приёмки и быстродействия порядка $2000, через 5 лет такая микросхема уже стоит $200. ПЛИС ёмкостью 10 000--30 000 логических вентилей стоят $10.

В таблице 3.1 приведена динамика развития рынка ПЛИС [2]. В зависимости с этим появляется ряд вопросов, касающихся того, какую элементную базу и как использовать её в новых разработках.

Таблица 3.1 – Объём рынка ПЛИС, млн $

| Область продаж | 1995 г. | 1996 г. | 1997 г. | 1998 г. | Рекомендуемые материалыВариант 3 - Контрольная работа - Объектно-ориентированное программирование на С Отчет по учебной практике - ГОСТ 7.32-2017 Гидравлический пресс 3.2 МН (для горячей объёмной штамповки) -60% Ответы к РК №3 ЛР 3 - Знакомство со средой MATLAB - Simulink -60% Ответы к РК №3 1999 г. |

| Военно-промышленная и космическая | 68 | 92 | 119 | 150 | 188 |

| Гражданская | 1125 | 1598 | 2146 | 2823 | 3678 |

| Итого | 1193 | 1690 | 2265 | 2973 | 3866 |

Классификация ПЛИС использует структурный признак [1], [3], который даёт наиболее полное представление о классе задач, пригодных для решения на ПЛИС. Общепринятой оценкой логической ёмкости ПЛИС является число эквивалентных вентилей, определяемое как среднее число вентилей 2И-НЕ, необходимых для реализации эквивалентного проекта на ПЛИС и базовом матричном кристалле (БМК). Эта оценка весьма условна, поскольку ПЛИС не содержат вентилей 2И-НЕ в чистом виде, однако для проведения сравнительного анализа различных архитектур она вполне пригодна. Основным критерием такой классификации является наличие, вид и способы коммутации элементов логических матриц. До настоящего времени в литературе отсутствует единая терминология по интегральным микросхемам ПЛИС, из-за чего в разных источниках они могут различаться.

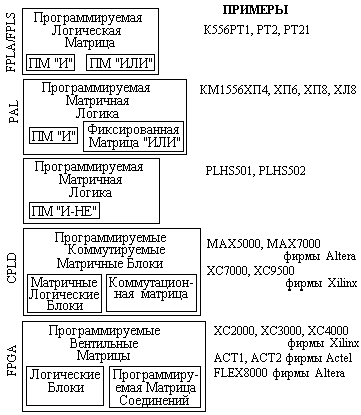

Рассмотрим историю развития архитектур ПЛИС. В конце 1970 годов на рынке появились ПЛИС с программируемыми логическими матрицами, имеющие программируемые матрицы И и ИЛИ. В зарубежной литературе соответствующими этому классу аббревиатурами являются FPLA (Field Programmable Logic Array) и FPLS (Field Programmable Logic Sequencers). В те времена отечественная электронная промышленность была ещё «на плаву», и вскоре появились отечественные схемы (см. рисунок 3.1) К556РТ1, РТ2, РТ21. Недостаток такой архитектуры – слабое использование ресурсов программируемой матрицы ИЛИ.

Идя по пути совершенствования такой архитектуры, разработчики ПЛИС предложили более простую архитектуру программируемой матричной логики (PAL – Programmable Array Logic и GAL – Gate Array Logic). Это ПЛИС, имеющие программируемую матрицу И и фиксированную матрицу ИЛИ. У ПЛИС GAL на выходе имеется триггер. К этому классу относится широкая номенклатура ПЛИС небольшой степени интеграции. В качестве примеров можно привести отечественные ИС КМ1556ХП4, ХП6, ХП8, ранние разработки (середина – конец 80-х годов) ПЛИС фирм Intel, Altera и др. Однако за любую унификацию надо платить избыточностью.

Другим подходом уменьшения избыточности программируемой матрицы (ПМ) ИЛИ является программируемая макрологика. ПЛИС, построенные по данной архитектуре, содержат единственную ПМ И-НЕ или ИЛИ-НЕ, но за счёт многочисленных инверсных обратных связей способны формировать сложные логические функции.

|

Рисунок 3.1 – Типы ПЛИС | Перечисленные архитектуры ПЛИС, содержащие небольшое число ячеек, к настоящему времени морально устарели и применяются для реализации относительно простых устройств, для которых не существует готовых ИС средней степени интеграции. Для реализации серьёзных алгоритмов управления они не пригодны. В начале 80-х годов на мировой рынок микроэлектронных изделий выходят три ведущие фирмы-производители ПЛИС. В 1984 г. основана компания Xilinx, Inc. (www.xilinx.com), в 1985г. – компания Actel Corporation (www.actel.com), в 1988 г. – фирма Altera Corporation (www.altera.com). Эти три ком пании занимают до 80 % всего |

рынка ПЛИС и являются основными разработчиками идеологии их применения. Если ранее ПЛИС являлись одним из множества продуктов, выпускаемых такими гигантами, как Intel, AMD и др., то, начиная с середины 80-х годов, на рынке ПЛИС происходит специализация и законодателями мод становятся фирмы, специализирующиеся на разработке и производстве ПЛИС.

С новыми производителями появились и новые архитектуры. ИС ПМЛ (PLD) имеют архитектуру, весьма удобную для реализации цифровых автоматов. Развитие этой архитектуры – CPLD (Complex Programmable Logic Devices) – ПЛИС, содержащие несколько логических блоков (ЛБ), объединённых коммутационной матрицей. Каждый ЛБ представляет собой структуру типа ПМЛ, т.е. программируемую матрицу И и фиксированную матрицу ИЛИ. ПЛИС типа CPLD, как правило, имеют высокую степень интеграции (до 10 000 эквивалентных вентилей, до 256 макроячеек). К этому классу относятся ПЛИС семейства MAX5000 и MAX7000 фирмы Altera, схемы ХС7000 и

ХС9500 фирмы Xilinx.

Другой тип архитектуры ПЛИС – программируемые вентильные матрицы (ПВМ), состоящие из логических блоков (ЛБ) и коммутирующих путей – программируемых матриц соединений. Логические блоки таких ПЛИС состоят из одного или нескольких относительно простых логических элементов, в основе которых лежит таблица перекодировки (ТП – Look-Up Table, LUT), программируемый мультиплексор, D-триггер, а также цепи управления. Таких простых элементов может быть достаточно большое количество, у современных ПЛИС емкостью до 1 миллиона вентилей число логических элементов достигает нескольких десятков тысяч. За счет такого большого числа логических элементов они содержат значительное число триггеров, а также некоторые семейства ПЛИС имеют встроенные реконфигурируемые модули памяти (РМП – Embedded Array Block, ЕАВ). Это делает ПЛИС данной архитектуры весьма удобным средством реализации алгоритмов цифровой обработки сигналов, основными операциями в которых являются перемножение, умножение на константу, суммирование и задержка сигнала. Вместе с тем, возможности комбинационной части таких ПЛИС ограничены, поэтому совместно с ПВМ применяют CPLD для реализации управляющих и интерфейсных схем. В зарубежной литературе такие ПЛИС получили название FPGA (Field Programmable Gate Array- программируемый полем массив вентилей). К FPGA (ПВМ) относятся ПЛИС ХС2000–ХС4000 фирмы Xilinx, АСТ1, АСТ2 фирмы Actel, а также семейства FLEX8000 фирмы Altera.

Множество конфигурируемых логических блоков (Configurable Logic Blocks, CLBs) объединяются с помощью матрицы соединений. Характерными для FPGA архитектурами являются элементы ввода/вывода (Input/Output Blocks, IOBs), позволяющие реализовать двунаправленный ввод/вывод, третье состояние и т. п.

Особенностью современных ПЛИС является возможность тестирования узлов с помощью порта JTAG (B-scan), а также наличие внутреннего генератора (Osc) и схем управления последовательной конфигурацией.

Фирма Altera пошла по пути развития FPGA архитектур и предложила в семействе FLEX10K так называемую двухуровневую архитектуру матрицы соединений. Логические элементы (ЛЭ) объединяются в группы – логические блоки (ЛБ). Внутри логических блоков ЛЭ соединяются посредством локальной программируемой матрицы соединений, позволяющей соединять любые ЛЭ. Логические блоки связаны между собой и с элементами ввода-вывода посредством глобальной программируемой матрицы соединений (ГПМС). Локальная и глобальная матрицы соединений имеют непрерывную структуру – для каждого соединения выделяется непрерывный канал.

Перспектива развития ПЛИС. Дальнейшее развитие архитектур идёт по пути создания комбинированных архитектур, сочетающих удобство реализации алгоритмов цифровой обработки сигналов на базе таблиц перекодировок и реконфигурируемых модулей памяти, характерных для FPGA структур и многоуровневых ПЛИС с удобством реализации цифровых автоматов на CPLD архитектурах. Так, ПЛИС APEX20K Altera содержит в себе логические элементы всех перечисленных типов, что позволяет применять ПЛИС как основную элементную базу для «систем на кристалле» (System-On-Chip, SOC) В основе идеи SOC лежит интеграция всей электронной системы в одном кристалле (например, в случае ПК такой чип объединяет процессор, память и т.д.). Компоненты этих систем разрабатываются отдельно и хранятся в виде файлов параметризируемых модулей. Окончательная структура SOC-микросхемы выполняется на базе этих «виртуальных компонентов» с помощью программ систем автоматизации проектирования (САПР) электронных устройств EDA (Electronic Design Automation). Благодаря стандартизации в одно целое можно объединять «виртуальные компоненты» от разных разработчиков.

Критерии выбора ПЛИС. При выборе элементной базы устройств управления руководствуются следующими критериями отбора:

· быстродействием;

· логическая ёмкость, достаточная для реализации алгоритма;

· схемотехнические и конструктивные параметры ПЛИС, надёжность, рабочий диапазон температур, стойкость к ионизирующим излучениям и т.п.;

· стоимость владения средствами разработки, включающая как стоимость программного обеспечения, так и наличие, и стоимость аппаратных средств отладки;

· стоимость оборудования для программирования ПЛИС или конфигурационных ПЗУ;

· наличие методической и технической поддержки;

· наличие и надёжность российских поставщиков;

· стоимость микросхем.

Лекции ни в коей мере не подменяют собой фирменную документацию, без которой проектирование управляющих устройств просто невозможно. Следует также заметить, что необходимо капитальней изучать английский язык, чтобы свободней работать с технической документацией.

Вопросы для проверки усвоения материала

1. Структурный признак классификации ПЛИС.

2. Структура программируемых логических матриц.

3. Перспектива развития ПЛИС.

4. Критерии выбора ПЛИС.

Литература

Люди также интересуются этой лекцией: 1.10 Свободное и вынужденное движение.

1. Вицын Н. Современные тенденции развития систем автоматизированного проектирования в области электроники//Chip News, №1, 1997, с. 12-15

2. Стешенко Б.В. ПЛИС фирмы АLTERA: проектирование устройств обработки сигналов. –М.: ДОДЭКА, 2000. –128 с. (6-7 с.)

3. Мальцев П.П., Гарбузов Н.И., Шарапов А.П., Кнышев Д.А. Программируемые логические ИМС на КМОП-структурах и их применение.1998. –М.: Энергоатомиздат, -159 с. (101-106 с.)

4. www.xilinx.com – сайт компании Xilinx, Inc.

5. www.actel.com – сайт компании Actel Corporation

6. www.altera.com – сайт фирмы Altera Corporation